Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

61 - 80 / 224

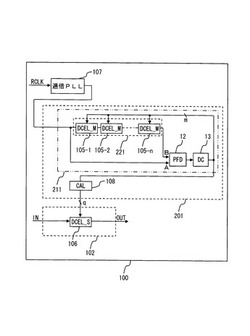

遅延ロックループ回路、信号遅延方法

【課題】回路面積を大きくすることなく、遅延ロックループ回路を提供すること

【解決手段】逓倍PLL107は、基準クロックを逓倍して出力する。DLL211は、逓倍PLL107から出力されたクロックと、逓倍PLL107から出力されたクロックを遅延させたクロックと、を比較し、比較結果に基づいて所定の遅延量を持つ遅延信号を生成する。遅延制御信号演算回路108は、DLL211が生成した遅延信号に基づき、所望の遅延制御信号を生成する。第1の遅延回路102は、遅延制御信号演算回路108が生成した遅延制御信号に基づいて、入力信号を遅延させる。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

PLL回路

【課題】ループフィルタの回路面積を削減すると共に、電圧制御発振器の動作の安定化やノイズ感度の低減が可能なPLL回路を提供することである。

【解決手段】本発明のPLL回路は、位相比較器3の出力信号に応じて出力電圧を制御する第1及び第2のチャージポンプ回路4、5と、第1のチャージポンプ回路4の出力に基づく信号から所定の周波数成分が除去された第1の電圧信号を出力する第1のフィルタ6と、第2のチャージポンプ回路5からの電流を入力し、所定の一定電圧を第2の電圧信号として出力する第2のフィルタ7と、第1のフィルタ6からの第1の電圧信号と基準電圧との比較結果に基づき第3の電圧信号を出力する電圧制御部30と、第1及び第2の電圧信号を低ゲイン入力、第3の電圧信号を高ゲイン入力とし、当該第1乃至第3の電圧信号に基づき発振周波数を生成する電圧制御発振器10を備える。

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

電子機器

【課題】ダブルオーブン型OCXOを用いる場合と同等の周波数安定度を維持しつつ、ダブルオーブン型OCXOを用いる場合よりもサイズ及びコストを低減可能な電子機器を提供する。

【解決手段】基地局本体部100は、電子部品(パワーアンプユニット101、デジタルユニット102、又は電源ユニット103)と、シングルオーブン型OCXO11と、シングルオーブン型OCXO11と電子部品とを収納する筐体110とを備える。筐体110には、電子部品が発する熱が伝達される。シングルオーブン型OCXO11は、筐体110に接触した状態で配設される。

(もっと読む)

通信装置、位相同期ループ、移動体および通信方法

【課題】通信装置、位相同期ループ、移動体および通信方法を提供すること。

【解決手段】受信信号の同期保持を行うための位相同期ループ254を備え、前記位相同期ループは、n次の位相同期ループ用の回路構成nを包含する、m次の位相同期ループ用の回路構成m(m>n)、を有するループフィルタ109と、前記ループフィルタにおいて有効化される回路構成を、前記回路構成nと前記回路構成mとで切替える切替部と、を含む、通信装置。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

量子干渉装置、原子発振器、および磁気センサー

【課題】ドップラー拡がりによる光共鳴波長分布を持つ原子集団に対しEIT現象を効率

よく発生させる原子発振器を提供する。

【解決手段】各共鳴光を出射するLD2と、LD2の中心波長を発生する中心波長発生手

段1と、二つの異なる基底状態のエネルギー差(ΔE12)に相当する周波数の1/2の

周波数を発振する発振器9と、ドップラー拡がりに対して十分小さい周波数を発振する発

振器10と、電気信号によりLD2から出射された共鳴光11に周波数変調を与えるEO

M(電気光学変調素子)3、4と、EOM4により変調された光12の波長により光の吸

収量を変化させる、気体状アルカリ金属(セシウム)原子を封入したガスセル5と、ガス

セル5から透過する光13を検出する光検出器(光検出手段)6と、光検出器6の出力に

基づきガスセル5のEIT状態を検出して出力電圧を制御する周波数制御手段7と、を備

えて構成されている。

(もっと読む)

原子発振器

【課題】周波数基準を実現させると共に、光源駆動制御回路系を簡略化して装置を小型化

し、且つ安価な光源を利用することでコストを低減することができる原子発振器を提供す

る。

【解決手段】この原子発振器50は、アルカリ金属の一種であるCs原子の異なる遷移エ

ネルギーに対応する二種類の周波数の励起光対を発生させる光源1と、少なくとも気体状

のCs原子を封入したCsセル2と、光検出器3と、光検出器3により検出した光強度の

変化に応じてその出力値(電圧等)を制御する周波数制御手段4と、周波数制御手段4の

出力値によりその出力周波数を制御可能な基準発振源5と、基準発振源5の出力周波数を

光源1が発生する二種類の励起光対の周波数差の周波数に逓倍する逓倍手段6と、逓倍手

段6で発生した周波数差の二種類の励起光対を光源1から発生させる光源駆動電流の変調

手段7と、を備えて構成されている。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

原子発振器およびその周波数安定化方法

【課題】外部磁場の変動によっても発振周波数の安定した小型の原子発振器および発振周

波数を安定化する方法を提供すること。

【解決手段】ガスセル2に封入されたアルカリ金属元素に、磁場発生手段4によって磁場

を印加することにより、アルカリ金属元素の基底準位がゼーマン分裂を起こす。印加され

る磁場は、逆回転の2つの円偏光に変換されたレーザー光に対し、ゼーマン分裂後の基底

準位間のエネルギー差△E12が略一定値となるような領域の磁場である。したがって、

磁場の変動に対してエネルギー差△E12の変動を少なくできる。磁場による変動の少な

い準位間のエネルギー差△E12を利用して、基準周波数8を制御しているので、磁気シ

ールド等が不要で、発振周波数の安定した小型の原子発振器10およびその周波数安定化

方法を得ることができる。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

電圧制御発振器を用いた方法及び配置

【解決手段】自己注入同期電圧制御発振器の配置(1)では、一組の結合する第1及び第2電圧制御発振器(21,22)がチップ(2)上に配置され、増幅器(23)が同一の反射型チップ(2)上に配置され、オフチップ遅延線路(10)が、前記結合された第1及び第2電圧制御発振器(21,22)の外部端子に接続される一端子であって前記外部端子からの信号を反射するように適合された一端子で配列され、低位相雑音及び小型化を示すVCOの配置(1)を提供するために、増幅器(23)は、前記外部端子からの注入信号を増幅するため及び増幅された注入信号を前記第1及び第2電圧制御発振器(21,22)の一つに供給するために配置される。 (もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

原子発振器の物理部

【課題】ガスセルの加熱効率の低下および光源の過熱を防止し、出力周波数が安定するとともに長寿命で信頼性の高い小型の原子発振器を提供する。

【解決手段】原子発振器の物理部50は、ガスセル10の一方の窓部2の外側にヒータ25、光学素子層15、ペルチェ素子21、傾斜部材35がこの順に重ねられ、傾斜部材35の傾斜の頂部から両側に形成された傾斜面にVCSEL30およびフォトセンサ40が配置されている。また、ガスセル10の他方の窓部3の外側には光反射膜45が形成されている。すなわち、ペルチェ素子21の低温となる面側にVCSEL30およびフォトセンサ40が配置され、ペルチェ素子21の高温となる面側にヒータ25が配置されている。また、光透過性を有さない傾斜部材35、ペルチェ素子21、ヒータ25の励起光の光路となる領域には貫通孔35a,35b,21a,21b,25a,25bが設けられている。

(もっと読む)

61 - 80 / 224

[ Back to top ]