Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

101 - 120 / 224

半導体集積回路装置、及び、クロックデータ復元方法

【課題】 インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】 インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

発振装置

【課題】比較的小さい回路規模で、発振停止を防ぐことのできる発振装置を提供する。

【解決手段】電流源から動作電流が加えられて発振信号を出力する発振器と、予め決められた時間の計測を開始し、前記計測が終了するとタイムアウト信号を出力する、少なくとも一つのタイマーと、前記タイマーから出力される前記タイムアウト信号を受信したときに、前記発振器から出力される前記発振信号の発振レベルと基準レベルとを比較し、前記発振レベルが前記基準レベル以上である場合、前記発振器に加えられる前記動作電流を減少させる制御を少なくとも1回行う制御部と、を備える。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

デジタル位相ロックループを実施するためのシステム及び方法

【課題】デジタル位相ロックループを実施するシステム及び方法を提供する。

【解決手段】デジタル位相ロックループを実施する装置は、VCO制御電圧に応答して1次クロック信号を発生する電圧制御式発振器を含む。検出手段は、カウントアップ信号及びカウントダウン信号を含むカウンタ制御信号を発生し、1次クロック信号と基準信号の現在の関係を示す。アップ/ダウンカウンタは、次に対応するカウンタ制御信号に応答してカウンタ値を増分又は減分する。カウンタ値は、次に電圧制御式発振器により発生された1次クロック信号の周波数を調節するためにデジタル/アナログ変換器によってVCO制御電圧に変換される。代替実施形態では、上述のアップ/ダウンカウンタを利用して、デジタル/アナログ変換器でVCO制御電圧を発生する以外の適切な技術の利用により、カウンタ値に比例して電圧制御式発振器の周波数を調節することができる。

(もっと読む)

光学系及び原子発振器

【課題】小型化、薄型化を実現した光学系を備えた原子発振器を提供する。

【解決手段】この光学系1aは、台座10の上に設置された端面発光型レーザダイオード(コヒーレント光源)2、受動光学素子4、ガスセル6、及び台座12の上に設置したフォトダイオード(導波路型受光素子:光検出器)8を基板11上の面方向に沿って順次配置し、夫々の素子が図示しないボンディングワイヤにより基板11に電気的に接続されている。

(もっと読む)

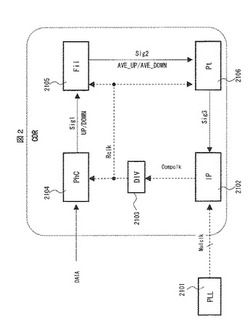

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

DLL回路及びこれを用いた半導体装置、並びに、DLL回路の制御方法

【課題】チップ上における占有面積が小さく、広範囲なクロック周波数に対応可能なDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させるディレイライン210と、ディレイライン210による遅延量を制御する制御回路とを備える。ディレイライン210は、従属接続された複数の可変遅延素子500を有し、可変遅延素子500は、バイアス電流量によって遅延量が変化する差動回路構成であり、制御回路は、バイアス電流量を設定する第1の制御部300と、複数の可変遅延素子500のうち出力を取り出す可変遅延素子を選択する第2の制御部400とを有している。本発明によれば、可変遅延素子によってディレイラインが構成されていることから、少ない段数にて広範囲なクロック周波数に対応することが可能となる。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を設定された遅延量だけ遅延して出力する遅延線路と、出力端子から出力される第2のクロック信号と第1のクロック信号との位相差に基づいて、遅延線路の遅延時間長を設定する遅延時間長設定部と、第1のクロック信号と第2のクロック信号の位相関係が特定の位相関係にあるか否かを検出する位相関係判定部と、特定の位相関係の検出時、遅延線路を含む伝搬経路上の第1のクロック信号を位相反転する位相反転/非反転部とで構成する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

PLL装置、映像同期制御装置及び表示装置

【課題】コストを抑えつつ、外部同期信号と内部同期信号との同期スピードを早くすることができるPLL装置、映像同期制御装置及び表示装置を提供する。

【解決手段】位相差比較部11が外部同期信号とフィードバックされて入力される内部同期信号との位相差を検出する。位相差判定部12は、検出された位相差が所定のしきい値以上であるか否か又は所定のしきい値未満であるか否かを判定する。VCXO18は、位相差判定部12の判定結果に応じて、フィードバックされる出力信号の周波数を可変する。

(もっと読む)

光学系及び原子発振器

【課題】受光素子を発光素子と同一側に併置することが可能となり、受光素子を電気的に接続するボンディングワイヤを短くしてモジュール実装を容易とし、且つ、S/Nを改善した光学系を備えた原子発振器を提供する。

【解決手段】この光学系1は、波長が異なるコヒーレント光としての2種類の共鳴光を入射したときの量子干渉効果による光吸収特性を利用して発振周波数を制御する原子発振器100の光学系1であって、ガスセル8中の金属原子に共鳴光3を供給するコヒーレント光源2と、共鳴光3に含まれるp偏光5を通過させs偏光13を光路変換する偏光分離手段4と、円偏光を直線偏光に若しくはこの逆に変換する1/4λ波長板6と、ガス状の金属原子を封入したガスセル8と、ガスセル8を通過した光9を再びガスセル8に導く導光手段10と、偏光分離手段4により光路変換されたs偏光14を検出する光検出器15と、を備えている。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

チャージポンプ回路、チャージポンプ装置、PLL回路、DLL回路、クロックデータリカバリシステム

【課題】チャージポンプ回路による充放電動作の正確性を向上させる。

【解決手段】充放電回路101では、充電部111は、制御信号UPに応答して充電電流を発生させ、放電部112は、制御信号DNに応答して放電電流を発生させ、これらの合成電流が中間電流Iaとして出力される。レプリカ回路102は、充放電回路101と同一の構成を有し、制御信号SIGに応答して、充電電流と放電電流との電流量の差(誤差成分)に相当する中間電流Ibを出力する。電流調整回路103は、中間電流Ibの極性を反転させ、調整電流Icとして出力する。これにより、中間電流Iaから中間電流Ib(誤差成分)が除去される。

(もっと読む)

クロック生成回路

【課題】大きなジッタや周波数オフセットを有する時刻情報が入力された場合でも、ジッタに追従して安定したシステムクロックを、優れたノイズ特性の回路により生成する。

【解決手段】周波数調整範囲が広い1個の電圧発振器を用いるのではなく、それぞれ周波数調整範囲が比較的狭く、かつ、互いに異なる3個のVCXO12〜14を備え、その内で入力PCRの周波数帯に応じて、クロック切替部15と制御部16とからなる選択手段により、周波数調整範囲が最適なものを適応的に選択する。これにより、大きなジッタや周波数オフセットを有するPCRが入力された場合でも、PCRジッタに追従して安定したシステムクロックを生成することができる。VCXO12〜14は、全体としては広い周波数調整範囲を持っていながら、その広い周波数調整範囲を持つ1個のVCXOに比べて発振出力のノイズ特性を優れたものにできる。

(もっと読む)

受信回路及び電子機器

【課題】PLLの低消費電力化、回路規模の低減、設計の困難性の低減。

【解決手段】所定の局部発振周波数IPA,QPAを出力する局部発振回路110を含み、受信信号RFと局部発振周波数IPA,QPAとを乗算した中間周波信号Iin,Qinを出力するアナログ直交復調回路100と、中間周波信号Iin,Qinを入力しフィルタ信号Iout,Qoutを出力する中心周波数と通過帯域とのどちらか少なくとも一方を可変にできる可変バンドパスフィルタ200と、フィルタ信号Iout,Qoutをデジタル信号Idi,Qdiに変換するアナログ−デジタル変換回路310,320と、所定の数値制御発振周波数IPB,QPBを出力する数値制御発振回路410を含み、デジタル信号Idi,Qdiと数値制御発振周波数IPB,QPBとを乗算した復調信号Idm,Qdmを出力するデジタル直交復調回路400と、を含む受信回路。

(もっと読む)

101 - 120 / 224

[ Back to top ]