Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

81 - 100 / 224

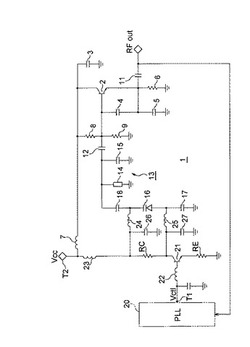

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

圧電発振器、および圧電発振器を用いた受信装置

【課題】温度補償回路を内蔵しない圧電発振器を用いて、GPS衛星の測位信号の捕捉時

間を短縮化させることができる圧電発振器、その圧電発振器を用いた受信装置および圧電

発振器を用いた受信装置の衛星捕捉制御方法を提供する。

【解決手段】圧電発振器用IC2と圧電振動子4を同一パッケージに組み立てて圧電発振

器1を構成すると、温度センサ7は精度よく圧電振動子4の温度を検出できる。圧電発振

器1を恒温槽に入れて、温度Tと出力周波数foutの周波数の関係を取得する。得られた

周波数−温度特性より、温度係数(A,B,C,D)とオフセット係数(E)を算出して

メモリ10に書き込む。この圧電発振器1を受信装置に組み込んだときにメモリ10から

温度係数とオフセット係数を抽出して近似曲線計算式から圧電発振器1の周波数偏差を求

め、周波数偏差分だけ、衛星からの探索範囲をオフセットさせて、GPS衛星の周波数を

捕捉する。

(もっと読む)

発振回路、及び映像表示装置

【課題】小規模の回路追加により、既存の回路を有効に活用しながら映像信号のクロックの周期とサンプリングクロックの周期との齟齬を解消する発振回路、及び映像表示装置を提供することを課題とする

【解決手段】分周器33と位相比較器31とを有する生成回路3へ、所定の発振信号を供する発振回路4であって、位相比較器31における比較結果に応じた周期のクロック信号を生成するクロック信号生成部42と、クロック信号生成部42が生成したクロック信号の一部をマスクした信号を分周器33へ供するクロック信号マスク部43と、を備え、クロック信号マスク部43は、生成回路3が生成するサンプリング信号の周期が、映像信号を生成する際に用いられるクロックの周期と同じになるようにクロック信号の一部をマスクする。

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号の位相に対して、クロック信号の位相を制御する遅延ロックループ回路であって、回路規模の縮小化及び低消費電力化を図かったアナログDLL回路を提供する。

【解決手段】基準クロック信号の位相と、第1のクロック信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、イニシャル信号の入力時において、位相比較器が出力する信号に応じた選択信号を発生する初期位相差検出器と、イニシャル信号の入力時において、初期位相差検出器からの選択信号に応じて、複数の位相が異なる第2のクロック信号の内から、基準クロック信号に最も近接した位相を有する第2のクロックを選択して、第3のクロック信号として出力する初期位相差設定回路と、第3のクロック信号に、位相比較器からの信号に応じた、位相遅延を付加した第1のクロック信号を出力する電圧制御可変遅延線とを備える遅延ロックループ回路を提供する。

(もっと読む)

デジタル放送受信装置、時刻情報生成回路、及びデジタル放送受信方法。

【課題】

従来の複数PCRに同期したSTCクロック再生方法は、複数チャンネル毎にPCRとの差分情報を参照するVCXOを独立に備えて複数のマスタクロックを生成し、これらマスタクロックを互いに独立に使用してSTCクロックを再生するPLLを有する構成となっており、高価な回路構成となっていた。

【解決手段】

複数PCRに同期させるために得られた各差分情報を一定周期で切り替えて、一組のVCXOに供給し、時分割にマスタクロックを生成し、各STCクロックを再生するPLLを機能させる。上記、切り替え時に未選択側の差分情報が必要なPLLは出力クロックの変動を抑えるためにPLL内部の位相比較をHoldさせることにより、安価で安定度の良い回路構成を可能にする。

(もっと読む)

同期検出回路、これを用いたパルス幅変調回路、及び同期検出方法

【課題】部品点数の削減、高い検出精度の確保、処理速度低下の防止等を図る。

【解決手段】位相ロックループ回路15により、基準クロック信号に基づいて互いに位相が異なる複数相の多相クロック信号を生成する多相クロック生成回路11と、前記多相クロック信号の中から、同期信号に同期するクロック信号を特定する同期クロック特定回路12とを有する同期検出回路2であって、前記多相クロック生成回路11は、前記基準クロック信号を逓倍した周波数を有する高速多相クロック信号と、前記高速多相クロック信号を分周した周波数を有する低速多相クロック信号とを生成し、前記同期クロック特定回路は、同期信号と前記高速多相クロック信号との比較結果と、前記同期信号と前記低速多相クロック信号から選択された代表クロック信号との比較結果とに基づいて、前記同期信号の同期位置を示す同期位置信号を生成する。

(もっと読む)

同期化制御回路、半導体装置及び制御方法

【課題】従来の回路に比較し、面積の縮小や消費電力の低減を図ることができる同期化制御回路を提供する。

【解決手段】分周回路部26において、外部クロックに対し位相の進んだ内部クロックLCLKを分周して分周クロックRSELOを生成し、分周クロックRSELOを遅延させて遅延分周クロックRSELIを生成する。外部クロックに対し位相の遅れた内部クロックPCLKに同期して外部から取り込まれた信号を、遅延分周クロックRSELIに同期してラッチ回路22に保持する。次いで、ラッチ回路22の出力信号を分周クロックRSELOに同期してラッチ回路23に読み込み、内部クロックLCLKに同期した信号として出力する。そして、分周回路部26が、変更可能な所定の分周数で内部クロックLCLKを分周する可変分周回路24を備える。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

位相同期発振器アレイ及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】発振信号の位相差が90度である4位相の同一周波数の発振信号を出力する位相同期発振器アレイである。複数の閉線路21〜23から成る複数のリング共振器と、閉線路の全長を1/4分割した位置に設けられた4つのポート21a〜21dのうち隣接する2つのポート21b、21cと、この閉線路21に隣接する閉線路22の隣接する2つのポート22a、22d間を、それぞれ、負性抵抗として、接続する差動発振器31a、31bと、少なくとも何れか1方の端部に配置される閉線路21において、その閉線路の4つのポートのうち、差動発振器が接続されていない2つのポート21a、21dに対して、90度の位相差を有した信号を励振する励振装置30とを有する。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

原子発振器

【課題】ガスセルの加熱効率の低下を抑えられるとともに、小型化が可能な原子発振器を提供する。

【解決手段】ガスセル10は、円筒部1と、その円筒部1の両端の開口部を封鎖する窓部2,3とにより、密閉されたキャビティT1が形成され、このキャビティT1内にアルカリ金属を気化させた多数の金属原子が封入される。二つの窓部2,3それぞれの外側の面には、ITOなどの透明電極膜からなる第1の加熱ヒーター12、および第2の加熱ヒーター13がそれぞれ積層されて設けられている。第1の加熱ヒーター12および第2の加熱ヒーター13の一端部分からは第1のヒーター配線22および第2のヒーター配線23が引き出されている。第1のヒーター配線22および第2のヒーター配線23は温度制御回路を有する制御回路基板に接続され、第1の加熱ヒーター12および第2の加熱ヒーター13は、第3のヒーター配線15により接続されている。

(もっと読む)

FM受信装置

【課題】ノイズの少ないFM受信装置を提供する。

【解決手段】アンテナと、発振回路と、位相比較回路と、チャージポンプ回路と、ループフィルタと、VCOと、VCO発振信号を所定の周波数ごとに分周し分周発振信号を生成する第1の分周回路と、VCO発振信号を所定の周波数ごとに分周し局部発振信号を生成する第2の分周回路とを備え、VCOはLC共振回路を含まない構成のものであり、分周発振信号を位相比較回路の入力信号とするものであって、局部発振信号と電波の信号より、複数の中間周波数信号を生成するミキサと、中間周波数信号をA/D変換するA/D変換器と、A/D変換器より出力された信号のうち、複数の中間周波数信号に対応するいずれか一つを選択し復調するデジタル復調器と、を備えたことを特徴とするFM受信装置を提供することにより上記課題を解決する。

(もっと読む)

クロック・データ・リカバリ回路

【課題】

USB2.0規格などの高速シリアル通信に用いるクロック・データ・リカバリ回路に関し、受信データの取り込みエラーを防止し、かつLSI化に適した回路を提供する。

【解決手段】

周期T1のクロックをN分割したT2単位でずらしたN相のクロックを出力する手段6、シリアル転送された信号をT2毎にサンプリングしてT1毎にNビットパラレルデータに変換する手段4、その出力データをデジタル処理してNビットパラレルデータに変換する手段で、またデータ変化点を示すNビットパラレルデータに変換する手段8、変化点を示すデータを位相情報入力として前記デジタル処理されたデータのデータ変化点の略中間位置を示すデータを出力する手段10、その出力データが示したビット位置に対応する前記デジタル処理されたデータを復元データとする手段12を備える。前記デジタル処理は、移動平均処理、デューティずれ補正処理とすることができる。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

原子発振器およびその制御方法

【課題】光情報の検出精度の劣化を抑えながら、ガスセルの温度制御を量子レベルで制御する原子発振器およびその制御方法を提供する。

【解決手段】本実施形態の原子発振器の光学系の要部である物理部50は、ガス状の金属原子を封入したガスセル10およびそれを保持するガスセル保持部材21からなるセルユニット20、ガスセル10を所定の温度に加熱するヒータ15、ガスセル10中の金属原子を励起するコヒーレント光の光源である光源30、ガスセル10を透過した励起光を検出するフォトセンサ40、フォトセンサ40により検出された励起光の強度に基づいてヒータ15を制御する温度制御手段、を有する。ガスセル10は、円筒部11と、該円筒部11の両端の開口部をそれぞれ封鎖して励起光の光路の入射面および出射面を形成する窓部12と、を有し、ヒータ15が、窓部12の前記光路と異なる領域に設けられている。

(もっと読む)

無石英発振器の通信装置と自動校正する嵌入式バーチャル水晶クロック出力方法

【課題】無石英発振器の通信装置と自動校正する嵌入式バーチャル水晶クロック出力方法を提供する。

【解決手段】無石英発振器の通信装置と自動校正する嵌入式バーチャル水晶クロック出力方法は、通信システムの送受信両端の一通信装置により、もう一つの通信装置に参考信号を提供し、通信装置は、この参考信号を元に、対応する参考周波数を生成することができる。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路で低消費電力で帯域制限された正確な短パルスの発生回路を具現。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点からから所定量の時間差で位相が順次変化するn個の信号(nは2以上の整数)を発生するタイミング発生回路10と、起動信号から発生しようとするパルスの継続時間に相当するパルス幅のパルス幅信号を発生するパルス幅信号発生回路30と、パルス幅信号の帯域を制限するフィルタ回路142,143と、所定の電位を供給する第1の電源147及び第2の電源146と、フィルタ回路142,143の出力値によってそのインピーダンス値が制御される可変インピーダンス回路144,145と、n個の信号の少なくとも一部の信号の論理関数値によって出力端子と第1の電源または第2の電源とを可変インピーダンス回路を介して交互に切り替えて接続する。

(もっと読む)

81 - 100 / 224

[ Back to top ]