Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

161 - 180 / 224

集積化されたPLL濾波器に係る変動するチャージポンプ電流

位相同期ループに関するデュアルパスループ濾波器について記述される。チャージ電流を変更することは、付加的な雑音を発生し余計な電力を消費するかもしれない能動形回路を使用することなしに、濾波器が部分的に位相同期IC回路の中に集積されることを可能にする。低減された濾波器キャパシタンスは集積することが可能である。  (もっと読む)

(もっと読む)

局部発振装置及びこれを用いた無線送受信機

【課題】周波数安定性と位相雑音特性に優れた局部発振装置を提供すること。

【解決手段】所定の信号処理手段に入力される少なくとも2つの局部発振信号を出力する局部発振装置であって、固定周波数である第1の局部発振信号を発する第1の発振手段と、可変周波数である第2の局部発振信号を発する第2の発振手段と、を備え、第2の発振手段は、第1の局部発振信号を入力して当該第1の局部発振信号の変化を補正する第2の局部発振信号を出力する。

(もっと読む)

可変位相器

【課題】 半導体可変位相器は周波数や周囲温度によって位相量が変化し、かつ時間を基準とした位相量を設定することができない。時間を基準とした位相量を設定するためには、予め使用する周波数で校正値を測定しておかなければならず、手間がかかりかつ精度を維持することが難しいという課題を解決する。

【解決手段】 2つの固定遅延器を用いて位相量と位相比較器出力との関係を求めておき、この関係を用いて設定する時間基準の位相量に対応する位相比較器の出力値を求め、位相比較器の出力がこの出力値になるように可変遅延器の制御電圧を調整するようにした。高精度で時間基準の位相量を設定することができる。

(もっと読む)

PLL回路

【課題】短時間に希望する周波数に収束するものであって、しかも使用するトランジスタの個数を減らして、コンパクトかつ安価に構成できるPLL回路を提供する。

【解決手段】PLL回路は、基準信号S0と周波数信号S1もしくは比較信号S2とが入力される周波数一致検出回路60を備えている。この周波数一致検出回路60によって制御される電流制御回路として、バイアス回路80、分圧回路90、および分圧比制御回路100を備え、VCO40の出力信号である周波数信号S1が基準信号S0の周波数によって設定される周波数から大きく外れている場合、チャージポンプ回路20からローパスフィルタ30に出力される被積分電流を増加させるように制御し、反対に、周波数信号S1が基準信号S0の周波数に近い場合には被積分電流を減少させるように制御している。

(もっと読む)

クロック生成回路

【課題】異なる複数の放送方式で共用でき、しかも回路構成の簡単化及び小型化を図り得るクロック生成回路を提供する。

【解決手段】従来の電圧制御型水晶発振器に比して周波数可変範囲の広い電圧制御型発振器11を使用するとともに、分周値を可変設定できる分周器12,14を使用するようにし、分周器12,14それぞれの分周値を取り扱う地上デジタル放送信号の放送方式に応じて分周値設定テーブル16から読み出して設定するだけで、1台の電圧制御型発振器11を各放送方式で共用できるようにしている。

(もっと読む)

PLL制御発振器

【課題】小型化を促進して生産性を良好にし、電気的性能を向したPLL制御発振器を提供する。

【解決手段】水晶振動子3Aと発振回路と温度補償回路とからなる温度補償水晶発振器と、前記温度補償水晶発振器を基準信号源としてPLL制御されたLC発振回路を備えたPLL制御発振器において、前記温度補償水晶発振器の水晶振動子を除く発振回路と、前記温度補償発振器の温度補償回路と、前記PLL制御されたLC発振回路とを1チップIC20に集積化して、前記ICチップと前記水晶振動子とを一体化してなり、前記水晶振動子はH状とした容器本体36の一方の凹部の内壁段部に水晶片の一端部が固着され、前記ICチップは前記一方の凹部底面に固着されてなり、前記容器本体の他方の凹部底面には前記LC発振回路のインダクタ28a28bを形成するとともに、前記インダクタは前記LC発振回路の発振周波数を調整するプリントによるインダクタである。

(もっと読む)

遅延を選択可能な遅延ロック・ループ

【課題】改良された遅延ロック・ループを提供する。

【解決手段】DLLは、位相検出信号と結合された制御モジュールを含む。制御モジュールは位相検出信号を用いてフィードバック選択信号及び出力選択信号を生成する。フィードバック選択信号及び出力選択信号はマルチプレクサに結合される。各マルチプレクサはマルチタップ遅延ライン(MTDL)に結合される。MTDLは、2つのマルチプレクサによって選択可能な複数の遅延された信号を提供する。フィードバック選択信号に結合された第1マルチプレクサは、フィードバック・クロック信号を選択する。出力選択信号に結合された第2マルチプレクサは、DLL出力信号を選択する。制御モジュールは、出力信号の遅延をプログラム又は設定するために使用できる遅延選択信号などのような、他の信号を受け取ることができる。更に、複数の出力信号をDLLから得ることができる。

(もっと読む)

リーク電流補償回路を備えたPLL回路

【課題】ループフィルタを構成するMOSトランジスタのリーク電流による電圧制御発振回路のコントロール電圧の変動を防止し、回路面積の縮小が図られたPLL回路を提供する。

【解決手段】

ループフィルタの電圧をサンプリングし保持するサンプル・ホールド回路と、そのサンプル・ホールド回路により保持された保持電圧とループフィルタの電圧を比較する演算増幅器と、比較結果によりループフィルタから漏洩したリーク電流を補償するリーク電流補償経路を備え、ループフィルタを構成するMOS容量のゲート酸化膜をサンプル・ホールド回路を構成するMOS容量のゲート酸化膜よりも薄いものを用いる。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】 参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】 位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

再生装置及び方法

【課題】回路規模を小さくし、コストを低減することを課題とする。

【解決手段】ディスク状記録媒体から検出された再生信号を用いて、再生信号に同期したクロックを生成する第1のクロック生成手段(102〜113)と、ディスク状記録媒体上に形成されたウォブル周期に対応する周波数を含むウォブル信号を用いて、ウォブル周期に対応する周波数を有するクロックを生成する第2のクロック生成手段(119〜125)と、第2のクロック生成手段により生成されたクロックに基づいて、ウォブル信号に重畳されているアドレス情報を検出するアドレス検出手段(126〜134)とを有する再生装置が提供される。再生時には、第1のクロック生成手段と第2のクロック生成手段とを同時に動作させる。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)。二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。  (もっと読む)

(もっと読む)

半導体装置

【課題】微細プロセスに好適で高性能化したV−I変換回路とPLL回路を備えた半導体装置を提供する。

【解決手段】入力電圧がゲートに供給された第1導電型のソースと第1電圧との間第1抵抗を設ける。第2電圧側に設けられた第2導電型の第2MOSFETと第3MOSFETで電流ミラー回路を構成し、上記第1MOSFETのドレイン電流に対応した出力電流を形成する。第1定電流源の定電流を上記第1電圧側に設けられた第1導電型の第4MOSFETと第5MOSFETで電流ミラー回路を介して上記第2、第3MOSFETの電流ミラー回路に流すようにする。上記中心電圧に対応した入力電圧の変化範囲と、中心電流に対応した出力電流の変化範囲とがほぼ対応するよう上記第5MOSFETに流れる定電流値及び上記第1MOSFETのコンダクタンスを設定する。

(もっと読む)

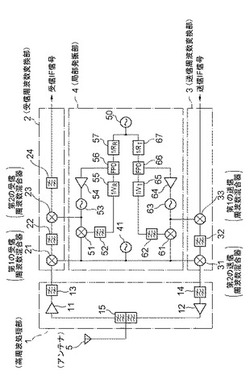

直交信号発生回路並びにそれを備えた受信チューナおよび通信機器

【課題】小型、低消費電力で、しかも互いに精度良く直交する2つの信号を出力できる直交信号発生回路を提供すること。

【解決手段】発振信号を発生する発振器1と、発振器1の発振信号を2分周して互いに実質的に直交する2つの分周信号Sig1,Sig2を出力する分周器2を備える。制御回路3は、2つの分周信号Sig1,Sig2のうちの一方の分周信号Sig1を入力部31に受けて、一方の分周信号Sig1が所定の基準信号と同期するように発振器1の発振信号をフィードバック制御する。分周器2が2つの分周信号Sig1,Sig2のうちの他方の分周信号Sig2を出力する配線12に、制御回路3の入力部31の入力インピーダンスと実質的に同一のインピーダンスをもつ負荷4が接続されている。

(もっと読む)

PLL周波数シンセサイザ

【課題】ロックアップタイムが短縮でき、かつ回路規模も小さくて済むPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザにおいて、ループフィルタ7をノッチ周波数がリファレンス周波数に設定されたツインT型ノッチフィルタ71とツインT型ノッチフィルタ71の後ろに直列接続されたローパスフィルタ72とで構成すると共に、ツインT型ノッチフィルタ71の一部を構成する抵抗R2とローパスフィルタ72の一部を構成する抵抗R2とを共用にした。

(もっと読む)

PLL回路におけるアクティブフィルタ。

【課題】 PLL回路の内部のローパスフィルタを構成する回路素子、特に静電容量の値を小さくすることによって、ローパスフィルタをチップに内蔵化可能とする。

【解決手段】 位相比較器の後段に2つのチャージポンプ回路を備えるPLL回路内で用いられるアクティブフィルタが、一方のチャージポンプ回路の出力とアースとの間に接続される第1の回路要素と、他方のチャージポンプ回路の出力とアースとの間に接続される第2の回路要素と、第1、第2の回路要素のそれぞれの両端の電圧を加算する電圧加算器とを備える。

(もっと読む)

ルビジウムランプ励振回路

【課題】ランプ励振器でルビジウムランプを点灯するためのスパーク発生回路にはトランスなど大型部品が含まれ、原子発ランプ励振器の小型化、低価格化が困難である。また、ランプ励振器の発振回路におけるブロッキング振動がランプ励振器の動作を不安定にする。

【解決手段】ランプ励振器100のルビジウムランプLP1に巻かれた励振コイルL1のHot Endの面と前記ルビジウムランプLP1の発光面とが一致するように、且つ、励振コイルL1の巻き線を発光部の全域に亘るように巻き、さらにその巻き線はチップ部LP1aには施さないように構成するとともに、前記ランプ励振器のLC発振回路13に供給する前記ルビジウムランプLP1点灯後の直流電源電圧を、ランプ点灯検出回路の検出信号に基づいてリレーRL1の接点を開放して抵抗R5を介することによって、点灯させるための直流電源電圧Vccより低減して供給するように構成する。

(もっと読む)

発振器、PLL回路および受信機、送信機

【課題】 回路規模を縮小することができるとともに集積化に適した発振器、PLL回路および受信機、送信機を提供すること。

【解決手段】 可変容量回路230、230Aの静電容量を可変することによって電圧制御型発振器21の発振周波数が変更される。可変容量回路230は、制御信号によって静電容量が連続的に変更可能な複数の可変容量素子60〜64と、可変容量素子のそれぞれに対応しており静電容量が固定の複数のコンデンサ50〜54と、可変容量素子とこれに対応するコンデンサとからなる組合せ回路を一組として複数の可変容量素子60〜64と複数のコンデンサ50〜54のそれぞれの選択的な接続の有無を組合せ回路を単位として切り替える複数のスイッチ71〜74、81〜84とを備えている。

(もっと読む)

スケーリングされた制動コンデンサを有する位相ロック・ループ

【課題】フィードバック・ループのループ・ダイナミクスおよび安定性に普通なら及ぼすような影響を及ぼすことなく、ループ・フィルタを実施するために使用されるコンデンサの面積を縮小すること。

【解決手段】チャージ・ポンプPLLの面積を縮小するために、ループ・フィルタ電圧の比例成分と積分成分を分離し、別の回路を追加して、積分成分が、実際に使用されたよりもはるかに大きな容量値によって影響を受けたかのように見えるようにすることができる。一態様では、電流ミラーを使用して、総ループ・フィルタ電圧からループ・フィルタ電圧の積分成分の一部分を減じることができる。次いで、差動信号を使用して、チャージ・ポンプPLLで発振器を駆動する。他の態様では、第3の積分器または自動較正ループを使用して、発振器の中央周波数を設定する。

(もっと読む)

半導体装置

【課題】高速動作する複数の回路ブロック間で同時に割り込み処理をおこなう場合のタイミング設計を容易化し、回路規模・消費電力を低減する。

【解決手段】クロック信号発生回路5と、クロック信号clkに同期して動作する複数の回路ブロック6とを有し、複数の回路ブロックのそれぞれは、周波数引き込み過程のクロック信号に同期して出力した割り込み信号reset_inを受けてリセット処理を行う。

【効果】タイミングマージンを大幅に向上させる。

(もっと読む)

遅延ロックループ

本発明は、遅延ロックループに関する。改良した遅延ロックループを提供するため、本発明によれば、遅延ロックループは、少なくとも、正の遅延ラインおよびクロックを受信するための入力部を有する第1の遅延素子、並びに負の遅延ラインおよびクロックを受信するための入力部を有する第2の遅延素子の2つの遅延素子と、前記2つの遅延ラインの1つからクロックを選択するクロックセレクタと、データを受信して、当該データの位相と前記クロックの1つの位相とを比較する入力部を有する位相検出器と、さらに、前記2つの遅延ラインが逆方向に反応するように当該2つの遅延ラインを制御する制御信号を生成する制御ブロックとを備える。  (もっと読む)

(もっと読む)

161 - 180 / 224

[ Back to top ]