Fターム[5J106LL01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 発振回路,VCO (115)

Fターム[5J106LL01]に分類される特許

61 - 80 / 115

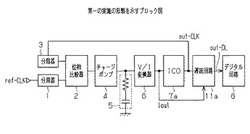

PLL回路

【課題】帰還ループに遅延回路を挿入することなく、出力信号でのジッタの発生を抑制し得るPLL回路を提供する。

【解決手段】基準信号ref−CLKと帰還信号の位相を比較する位相比較器2と、チャージポンプ4と、ループフィルター5と、電圧電流変換器6と、電流制御発振器7aと、電流制御発振器の出力信号を分周して帰還信号を生成する分周器3とを備えた帰還ループにより、出力信号out−CLKの周波数を基準信号で設定される周波数に収束させるPLL回路であって、電流制御発振器7aから負荷回路8に出力される出力信号out−DLと位相比較器2に入力される基準信号の位相をずらす遅延回路11aを帰還ループ外に備えた。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

PLL回路及び信号送受信システム

【課題】出力クロック信号のジッタ値に対するプロセスばらつきによる影響を抑える。

【解決手段】PLL回路として、基準クロック信号と出力クロック信号に基づくフィードバッククロック信号との間の位相差を検出する位相周波数比較回路と、前記位相差に応じて電流を出力するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑化し、制御電圧として出力するローパスフィルタと、前記制御電圧、ゲイン制御信号、及びオフセット制御信号に応じた周波数の信号を生成し、前記出力クロック信号として出力する電圧制御発振回路と、前記制御電圧の変化に対する前記出力クロック信号の周波数の変化の比が目標値になるように、前記ゲイン制御信号を求めるゲイン調整回路と、前記制御電圧が所定の値である時における前記出力クロック信号の周波数が目標値になるように、前記オフセット制御信号を求めるオフセット調整回路とを備える。

(もっと読む)

電圧生成回路及び発振装置

【課題】位相雑音特性が良好で、かつ低消費電力、小型化に適した発振装置を提供すること。

【解決手段】固定電圧Vrefが印加される第1の端子と、可変電圧Vcが印加される第2の端子と、前記第1の端子と前記第2の端子との間に直列接続された、抵抗値rのm個の抵抗器及び抵抗値RINの入力抵抗器と、前記m個の抵抗器のうちn個の抵抗器を選択するための複数のスイッチと、制御電圧を出力する第3の端子と、を有する抵抗切替部と、前記複数の抵抗器に流す定電流の電流値Ioffを設定し当該定電流を供給する電流供給部とから構成され、{Vref+n×r×[(VC−Vref)/(m×r+RIN)]}で与えられる第1の電圧と、{−(n×r×Ioff)}で与えられる第2の電圧との重ね合わせにより規定される第3の電圧を、前記第3の端子から制御電圧として出力する。

(もっと読む)

VCO回路

【課題】可変周波数範囲の広域化を可能にしつつ高い位相雑音特性を備えるVCO回路を提供する。

【解決手段】上記課題を解決するために、VCO回路100に、バッファ回路B11、P型MOSトランジスタQ11及びキャパシタC11からなるバイアス回路101と、アンプA11と、インダクタL11、可変キャパシタC12、及びスイッチ付きキャパシタC13、C14、・・・からなる共振回路102と、を備える。

(もっと読む)

電圧制御発振回路およびPLL回路

【課題】出力クロックの変動を抑えることができる電圧制御発振回路およびPLL回路を提供する。

【解決手段】この電圧制御発振回路によれば、第2の電源生成回路1−2が出力するゲート制御信号103,104によって、一部の反転回路10−nの遅延時間を変更制御するが、残りの反転回路10−1〜10−(n−1)の遅延時間は第1の電源生成回路1−1によって一定に制御する。したがって、第2の電源生成回路1−2が制御する電源電圧103−n,104−nが変化(変動)しても出力クロック100の周波数の変化(変動)は従来のように全ての反転回路の遅延時間を変更制御する場合に比べて小さい。

(もっと読む)

PLL回路を備えた半導体集積回路

【課題】製造条件によるデバイス特性のバラツキや使用温度、電源電圧などの使用環境によるデバイス特性のバラツキがある場合でも、未然にVCO6の発振停止を防止すると共に、安定的に起動を行うことができるPLL回路を備えた半導体集積回路を提供する。

【解決手段】PLL回路2の過渡応答時間とデバイス及び使用環境に応じたチャージポンプ4の電流値を、事前にメモリ10に保存しておき、マイコン9からの制御信号ICPctlに基き、チャージポンプ4は、PLL回路2起動時から発振安定時までの過渡応答期間中は、電流値をメモリ10の設定情報に従って低減させる。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

オシレータのデジタル調節

【課題】オシレータの振動周波数の調節を可能とさせ、それにより効率的な態様で且つ顕著なダンピング無しで振動周波数の選択的変更を達成する。

【解決手段】オシレータの振動周波数の調節、特に回路装置によるPLLオシレータのデジタル粗調節に関するものである。回路装置は少なくとも一対のコンデンサ(C,C′)を有しており、その第一端子はオシレータと接続しており、且つ第二端子は、コンデンサ対(C,C′)をオシレータの振動回路内に組込むためにスイッチング装置によって第一基準電位(vss)と選択的に接続させることが可能である。尚、回路装置は、第一基準電位(vss)との該第二端子の選択的接続のための第一FETs(T1,T1′)、互いに第二端子を接続するための第二FET(T2)、及び第一基準電位(vss)とは異なる第二基準電位(vdd)との第二端子の夫々の接続のための第三FETs(T3,T3′)を有している。

(もっと読む)

周波数シンセサイザ、および周波数シンセサイザの発振制御方法

【課題】 ロック状態を維持したまま発振周波数帯域の切り替え動作が可能な周波数シンセサイザを、小規模であって低消費電流な回路構成で実現する周波数シンセサイザ、および周波数シンセサイザの発振制御方法を提供すること

【解決手段】 発振周波数帯域の切り替えが可能な発振制御回路2を備える周波数シンセサイザ1は、発振周波数帯域の違いによる発振制御回路2へのバイアス信号IBの差を、差分バイアス信号ΔIBとして出力する差分バイアス部5と、発振周波数foが発振周波数帯域fbの限界値を越えて遷移したことを検出する帯域限界検出部3と、帯域限界検出部3による検出に応じて、発振周波数帯域fbの切り替えのために差分バイアス部5の動作が切り替えられる過渡期間において、差分バイアス部5に対して、出力されるバイアス信号IBを漸次遷移する制御を行なう過渡制御部4とを備えている。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

電圧制御発振回路、及び、その調整方法

【課題】電圧制御発振回路、及び、その調整方法に関し、制御電圧に対する周波数の変化量を精度よく調整できる電圧制御発振回路を提供することを目的とする。

【解決手段】本発明は、制御電圧に応じて容量成分が制御される可変容量素子と、可変容量素子に直列に接続された直列容量素子と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子とを有する電圧制御発振回路において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されていることを特徴とする。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

PLL回路及びPLL回路を構成する可変ディレイラインの制御方法

【課題】 任意の幅で重なり合う発振レンジの設定を行い、PLL回路でのジッタの発生を抑制する。

【解決手段】 デジタルPLL回路10の発振制御回路2には、カウンタ制御回路11、第1のアップダウンカウンタ12、及び第2のアップダウンカウンタ13が設けられ、カウンタ制御回路11は、制御信号Scmが、ある値M=Xである状態からM=X+1である状態に変化するときに、制御信号Scnが段階的にアップカウントせずに、例えばスキップしてアップカウントが可能となる制御信号Smupと、制御信号Scmが、ある値M=X+1である状態からM=Xである状態に変化するときに、制御信号Scnが段階的にダウンカウントせずに、例えばスキップしてダウンカウントが可能となる制御信号Smdnとを入力する。このため、可変ディレイラインから出力されるディレイ信号は製造バラツキ、温度、及び電源電圧などの変動によらず任意の幅で重なり合う。

(もっと読む)

PLL回路

【課題】ビデオ信号の垂直同期区間に位相ずれが発生しても高速引き込みを実現する。

【解決手段】位相比較回路1は、同期分離信号とVCO回路4の出力から帰還されてくる同期再生クロック信号の位相を比較して位相差を検出する。同期検出回路5は位相比較回路7の出力信号により該PLL回路が同期状態かを判定する。遅れ位相検出回路6は、同期した状態と判定され、且つ位相比較回路で検出された位相差が設定値を超えた時に同期再生クロック信号を遅延させるための制御信号をVCO回路4へ出力する。進み位相検出回路7は、同期した状態と判定され、且つ位相比較回路で検出された位相差が設定値を超えた時に同期再生クロック信号を反転させるための制御信号をVCO回路へ出力する。

(もっと読む)

周波数シンセサイザ

【課題】複数の発振周波数帯域から1つの周波数帯域を選択可能な集積化されたVCOを構成する素子に製造ばらつきがあっても、最適な周波数帯域で所望の周波数に位相ロックすることができ、しかもVCOの消費電流を低減できる周波数シンセサイザを提供する。

【解決手段】分周比格納部9aの分周比が更新されたらPLLを開ループ状態にして可変分周器2、3の出力信号と基準分周器5の出力信号の位相を比較し、その結果に応じて、電圧制御発振器1bの共振回路の共振周波数を変化させながら、所望の周波数の周波数帯域を選択し決定する。その後、可変分周器の出力信号と基準分周器5の出力信号の位相を比較し、その結果に応じて、電圧制御発振器1bの電流を変化させながら、最適電流値を決定する。その後、位相同期系を閉ループ状態にして位相ロックさせる。

(もっと読む)

PLL回路及びチャージポンプ回路の駆動方法

【課題】PLL回路のロック時のループフィルタの出力電圧の変動を抑えることである。

【解決手段】基準クロック信号と帰還クロック信号の位相が一致したとき、基準クロック信号と帰還クロック信号の立ち下がりのタイミングで、オン時間の短いUP信号とDOWN信号をチャージポンプ回路の2個のMOSトランジスタに供給する。これにより、チャージポンプ回路の貫通電流を少なくできるので、貫通電流によるループフィルタの出力電圧の変動を抑えることができる。

(もっと読む)

電圧制御発振器、動作電流調整装置、および、電圧制御発振器の動作電流調整方法

【課題】電圧制御発振器の動作電流を自動的に調整し位相雑音特性を向上することが可能な動作電流調整装置を提供する。

【解決手段】本発明に係る動作電流調整装置100は、電圧制御発振器1と、発振周波数制御電圧を出力する電圧発生部14と、発振信号の発振周波数を測定する周波数検出部15と、電圧発生部14が発振周波数制御電圧Vcontを制御するための電圧設定信号Svsetを出力するとともに、周波数検出部15で測定された発振周波数に基づいて電源回路5が動作電流Iccを制御するための動作電流制御信号Scontを出力する制御部16と、を備える。

(もっと読む)

通信用半導体集積回路

【課題】通信用半導体集積回路で、発振用の電界効果トランジスタ(FET)のしきい値電圧Vthのバラツキによる送信用電圧制御発振器TXVCOの発振振幅値のバラツキを補償すること。

【解決手段】位相変調ループ制御回路PM_LPは、しきい値電圧発生回路Vth_Genと、送信用電圧制御発振器TXVCOの出力と送信用RF電力増幅器RF_PAの入力との間の可変利得増幅器BFとを含む。しきい値電圧発生回路Vth_Genは、TXVCOの発振用FETQN1、QN2:QP1、QP2のVthと等しいVthのFETQn17、Qp17を含む。送信用電圧制御発振器TXVCOの発振電圧振幅値のバラツキをRF_PAの入力で補償するように、可変利得増幅器BFの可変増幅利得がVth_Genからの出力V1に応答して設定される。

(もっと読む)

発振回路

【課題】従来技術よりも正確な位相差を得ることができる発振回路を提供する。

【解決手段】複数のオペアンプ20−1〜20−4をループ状に直列に接続して構成されるリング発振回路202を含み、複数のオペアンプ20−1〜20−4における複数の出力信号を加算合成して第1の出力信号Vout1として出力すると共に、複数のオペアンプ20−1〜20−4における残りの総ての出力信号を加算合成して第2の出力信号Vout2として出力することによって上記課題を解決することができる。

(もっと読む)

61 - 80 / 115

[ Back to top ]