Fターム[5J106LL01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 発振回路,VCO (115)

Fターム[5J106LL01]に分類される特許

41 - 60 / 115

位相ロックループ回路

【課題】出力クロック信号の定常位相誤差を防止することを課題とする。

【解決手段】リファレンスクロック信号及びフィードバッククロック信号の位相差を検出する位相差検出器(101)と、前記検出された位相差に応じて、第1のコンデンサを電源電圧又は基準電位に接続する第1のチャージポンプ回路(102)と、前記検出された位相差に応じて、第2のコンデンサを前記電源電圧又は前記基準電位に接続する第2のチャージポンプ回路(122)と、前記第1及び第2のコンデンサの電圧を比較して比較結果信号を出力する比較器(141)と、前記比較結果信号に応じて、前記第1のコンデンサを前記電源電圧又は前記基準電位に接続する第1のスイッチ(142)と、前記第1のコンデンサに接続され、前記第1のコンデンサの電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振器(104)とを有する。

(もっと読む)

位相ロックループ回路

【課題】広周波数範囲で動作可能であり、電圧制御発振器のゲインを低減させることができる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号及びフィードバッククロック信号の位相差を検出する位相差検出器(101)と、制御電圧を保持するコンデンサ(117)と、前記検出された位相差に応じて、前記コンデンサを電源電圧又は基準電位に接続するチャージポンプ回路(102)と、前記制御電圧に応じた発振周波数の出力クロック信号を生成し、前記出力クロック信号又は前記出力クロック信号に応じた信号を前記フィードバッククロック信号として前記位相差検出器に出力する電圧制御発振器(104)とを有し、前記電圧制御発振器は、4段の差動リングオシレータ(131〜134)と、前記4段の差動リングオシレータの異なる段で出力されるクロック信号の排他的論理和信号を出力する第1の排他的論理和回路(127)とを有する。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

電圧制御発振器及びこれを用いた位相同期回路

【課題】インバータセルを構成するMOSトランジスタが飽和領域のみならず、線形領域で動作する場合にも位相雑音を低減する。

【解決手段】ダミーインバータセル110からの信号と、基準信号との電位差を増幅した増幅信号を出力する演算増幅器120と;第2MOSトランジスタ102に接続され、増幅信号を受ける第1MOSトランジスタ101と、インバータ入力部及びインバータ出力部として機能する第2MOSトランジスタ102及び第3MOSトランジスタ103と、第3MOSトランジスタ103に接続され、発振信号の周波数を制御するための制御信号を受ける第4MOSトランジスタ104とを含むインバータセル100を環状に接続したリング・オシレータと;インバータセル100と同一の構造を備え、インバータ出力部がインバータ入力部に短絡されたダミーインバータ110と;を具備する。

(もっと読む)

発振周波数制御方法及び発振器

【課題】温度によって変化する発振周波数を、応答性良く、正確に、所定の周波数に調整することができる発振周波数の制御方法及び発振器を提供する。

【解決手段】本発明の発振周波数制御方法は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器の発振周波数制御方法であって、振幅を測定する工程と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する工程を備える。また、本発明の発振器は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器であって、振幅を測定する振幅測定部と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する温度補償部を備える。

(もっと読む)

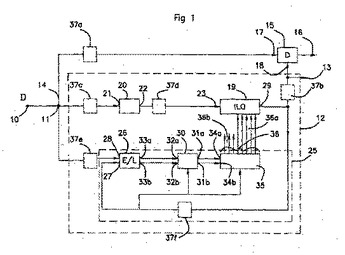

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

PLL回路の電圧制御発振器における漏洩電流を補償する回路構成

【課題】PLL回路の電圧制御発振器内の漏洩電流を補償する回路構成を得る。

【解決手段】ループフィルタ(20)により発振器へ加えられる制御電圧は、基準信号と電圧制御発振器(12)の出力信号との位相差の関数として位相検出器(16)により発生される。発振器(12)は、制御線(34)を介して制御電圧が加えられるバリキャップダイオード(28,30)を含み、同じ構成のバリキャップダイオード(36,38)を有する補償回路(K)が一方の出力(44)において制御電圧を再生して補償回路(K)内のバリキャップダイオード(36,38)へ加え他方の出力(46)からはバリキャップダイオード(36,38)の漏洩電流に等しい電流を供給する。電流分路分岐が制御線(34)から延びており、それを介して演算増幅器(40)により供給される電流に対応する電流が制御線(34)から流れる。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】より容易に広い制御電位の範囲にわたって発振周波数の線形性が高い電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路、n個の可変容量回路、及び負性抵抗回路と、電源電位からn個の基準電位を生成する基準電位発生部114とを備える。n個の可変容量回路の可変容量素子の一方端子には、n個の基準電位のいずれかがそれぞれ入力される。n個の可変容量回路の可変容量素子の他方端子には、発振周波数をフィードバック制御するための制御電位Vtが共通入力される。そして、第1〜第3の可変容量回路A〜Cの一方端子には、第1〜第3の基準電位Vref1〜3がそれぞれ入力される。この第1〜第3の基準電位Vref1〜3はそれぞれ固定で、かつ、第1の基準電位Vref1と第2の基準電位Vref2の電位差と、第2の基準電位Vref2と第3の基準電位Vref3との電位差が異なっている。

(もっと読む)

高周波発振回路、位相同期ループ回路、半導体装置及び通信装置

【課題】より大きなQのインダクタを必要とせず、従来技術に比較してより小さいサイズでかつより高い発振周波数で発振させることができる高周波発振回路を提供する。

【解決手段】帰還型高周波発振回路は、短絡スタブ用伝送線路に接続されたゲートと、発振出力端子に接続されたドレインとを有する電界効果トランジスタ1と、電界効果トランジスタ1のソースに接続されたドレインを有するソース接地の電界効果トランジスタ2とを含み構成され、短絡スタブ用伝送線路11及び電界効果トランジスタ2を帰還回路として発振する。また、電界効果トランジスタ2のゲートと、電界効果トランジスタ1のドレインとの間に帰還用キャパシタを接続する。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

クロック発生装置

【課題】PLL回路を使用し、より幅広い環境変動に適応して周波数を一定値にロックすることのできるクロック発生装置を得る。

【解決手段】クロック発生装置200は、基本的に同一構成で共にLC型VCOを備えた第1および第2のPLL回路201、202を備えている。マスタ側の第1のPLL回路201の第1のVCO2241に加わる第1の制御電圧2281は基準電圧検出回路212で3つの固定値と比較され、その結果に応じて第2のPLL回路202の容量スイッチ247、257の値を調整しておいて、出力セレクタ207で第1のPLL回路201から第2のPLL回路202にクロックの選択を切り替える。

(もっと読む)

位相同期回路

【課題】キャリブレーションを高速化する。

【解決手段】VCO16は、入力された制御電圧Vcntに応じた周波数foscで発振し、ある制御電圧Vcntに対する発振周波数foscを可変とするための調節用キャパシタ50a、50bを含む。分周器18は、VCO16の出力信号OUTを、所定の基準クロックREFの周波数と一致するように分周する。位相比較部2は、分周器18の出力信号OUT2と、基準クロックREFの位相を比較し、位相差に応じた電圧を制御電圧VcntとしてVCO16に出力する。容量調節部30は、所定のキャリブレーション期間中に、周波数がロック状態した状態で、制御電圧Vcntが所定の電圧範囲に含まれるように、調節用キャパシタ50の容量値を調節する。ループ制御部40は、キャリブレーション期間中と、通常動作期間中とで、当該位相同期回路100のループ特性を変化させる。

(もっと読む)

デジタル制御発振器、このデジタル制御発振器を備えた位相同期ループ及び通信機

【課題】スプリアスが生じにくい。

【解決手段】ADCから入力されたnビットのデジタル信号は、mビットが整数部41、且つ、n−mビットがデジタル制御値時間変化部43に入力される。そして、デジタル制御値時間変化部43から時間的に変化するデジタル制御値が小数部42に入力される。デジタル制御発振器4は、整数部41によってステップ周波数刻みで発振周波数を変化させる。また、小数部42によってステップ周波数よりも小さな周波数刻みで発振周波数を変化させる。このとき、小数部42によって変化させることができる周波数は、ステップ周波数よりも大きい。

(もっと読む)

電圧制御発振器および電圧制御発振器の発振周波数制御方法

【課題】電圧制御発振器で使用される可変容量において、回路のグラウンド電位から電源電位以上に広い可変容量の線形領域を使用することが可能な電圧制御発振器を提供する。

【解決手段】共振回路を構成するインダクタ2a、2bと可変容量10a、10b、11a、11b、12a、12bと、共振回路の共振周波数を制御するための周波数制御端子5とを備えた発振部200に加え、共振回路にバイアス電圧を与えるバイアス回路201と、周波数制御電圧に応じてバイアス回路201のバイアス電圧を切り替え制御するバイアス制御回路202を設ける。バイアス制御回路202は周波数制御電圧が変化してしきい値を超えたときに、周波数制御電圧を目的の制御電圧に近づける方向にバイアス電圧を切り替える。

(もっと読む)

電圧制御発振回路

【課題】電圧電流変換部の制御電圧入力用MOSトランジスタにデプレッション型を使用した際に発生する発振周波数(バイアス電流)オフセットの製造プロセスばらつきが補正された電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路1は、制御力電圧がゲートに入力される第1のデプレッション型MOSトランジスタ13と、その第1のデプレッション型MOSトランジスタ13のゲート・ソース間電圧が0Vのときのオフセットを補償する第2のデプレッション型MOSトランジスタ15を有し、制御電圧に応じたバイアス電流を発生する電圧電流変換回路3を備える。

(もっと読む)

電圧制御発振器、PLL回路

【課題】 低周波の発振信号であっても安定して出力することが可能な電圧制御発振器及びPLL回路を提供する。

【解決手段】 本発明に係る電圧制御発振器1は、インダクタ4及び可変キャパシタ5を有するLC共振回路2と、複数の負性抵抗回路NR1、NR2、…、NRnを備える。各負性抵抗回路NR1、NR2、…、NRnは、定電流源CG1、CG2、…、CGnを介して夫々接地線と接続される構成であり、各定電流源は、夫々個別に導通状態(一定電流を流す状態)と非導通状態(開放された状態)との間で切換制御が可能に構成されており、本発明に係る電圧制御発振器1は、これらの各定電流源の導通制御を行うための制御手段7を備える構成である。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【解決手段】プログラマブルバラクタ装置は、複数のデジタルバラクタビットによって制御される複数のバイナリ重み付けバラクタを含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。 (もっと読む)

41 - 60 / 115

[ Back to top ]