Fターム[5J106LL01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 発振回路,VCO (115)

Fターム[5J106LL01]に分類される特許

21 - 40 / 115

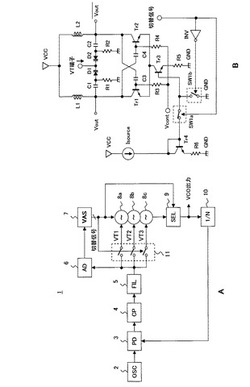

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

同期化システム用結晶ベース発振器

【課題】クロックの不具合の可能性を排除し、冗長性及び拡張性を備える同期化システムを提供するためのSXOモジュールを提供する。

【解決手段】第1のバスから調整済み信号を受信し、共振器信号をステージ維持増幅器に渡す結晶共振器を含む結晶発振器ベースのモジュール。同期化範囲拡大回路が利得制御ネットワークと共振器の間に接続される。トライステートバッファがバッファを介して共振器信号を受信するように接続された主入力を有する。トライステートバッファの出力は、必要に応じて整合ネットワークを介して、第2のバスに接続される。上記モジュールを交互に2つのバスに接続することによって同期クロックシステムが形成されうる。また、トライステートバッファは制御入力も有しており、制御入力はホットスワッピングおよび他の便益を可能にするようにVccとグラウンドの間の遅延回路に接続されてもよい。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

PLL回路

【課題】電圧制御発振器が発振信号出力動作を停止した場合、自動的に最適消費電流で電圧制御発振器の発振信号出力動作を復帰させることができるPLL回路を提供する。

【解決手段】リセット制御回路7は、電圧制御発振器5の発振信号出力動作の停止を検出し、電圧制御発振器5の発振信号出力動作の停止を検出している間、基準信号Ref_CKを分周してなるリセット信号RESETを生成する。カウンタ8は、リセット信号RESETの立ち上がり変化の回数をカウントする。ローパスフィルタ4は、前記リセット信号RESETがLレベルの間に周波数制御電圧Vcntを初期化する。電圧制御発振器5が有する出力アンプは、前記カウンタ8が出力するカウント値Cnt[1:0]が増加する毎に駆動電流を段階的に増加させることにより出力駆動能力を段階的に増加させ、周波数帯域を段階的に上げる。

(もっと読む)

オシレータ及びオシレーティング信号を生成する方法

【課題】位相同期ループクロック発生器等に好適に使用できるオシレータ及びオシレーティング信号を生成する方法を提供する。

【解決手段】オシレータであって、第1スターブドインバータ(current−starved inverter)と、前記第1スターブドインバータの内部インバータとクロスカップルされる内部インバータを含む第2スターブドインバータと、前記第1スターブドインバータの内部インバータの出力と接続される第1インバータと、前記第2スターブドインバータの内部インバータの出力と接続される第2インバータとを具備し、前記第1インバータの出力は、前記第2スターブドインバータの外部インバータの入力に供給され、前記第2インバータの出力は、前記第1スターブドインバータの外部インバータの入力に供給されることを特徴とする。

(もっと読む)

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

容量切り換え回路、VCO、およびPLL回路

【課題】 PLLおよびVCOの発振特性を改善できる容量切り換え回路を提供する。

【解決手段】 端子P1と端子P2との間に、コンデンサC1k(k=0〜n)と、FET(Q1k)と、コンデンサC2kとを直列接続する。FET(Q1k)のソースにFET(Q3k)のドレインを接続する。FET(Q1k)のドレインにFET(Q4k)のドレインを接続する。FET(Q3k、Q4k)のゲートは互いに接続し、それらのソースも互いに接続する。FET(Q1k)のゲートに、このFET(Q1k)をオンオフ制御する制御データbkを供給する。FET(Q4k)のソースに、少なくともFET(Q1k)がオフのときには、FET(Q3k、Q4k)をオフにするソースバイアス電圧VSkを供給する。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

位相ロックループ回路及び遅延ロックループ回路

【課題】ジッタの増加を防止し、カットオフ周波数の変動を防止することができる位相ロックループ回路及び遅延ロックループ回路を提供することを課題とする。

【解決手段】リファレンス信号とフィードバック信号との位相を比較し、その位相差を示す位相差信号を出力する位相比較器(101)と、前記位相差信号に応じたチャージポンプ電流を出力するチャージポンプ(102)と、抵抗及び容量を含み、前記チャージポンプ電流を平滑化して制御電圧に変換するローパスフィルタ(103)と、前記制御電圧に応じた周波数の発振信号を生成する電圧制御発振器(104)と、前記発振信号を分周した分周信号を生成し、前記分周信号を前記フィードバック信号として前記位相比較器に出力する分周器(105)とを有し、前記ローパスフィルタ内の抵抗は、前記制御電圧に応じて変化する可変抵抗であることを特徴とする位相ロックループ回路が提供される。

(もっと読む)

半導体素子、クロック同期化回路、及び、クロック同期化回路の駆動方法

【課題】クロック同期化回路は、インジェクションロッキング方式を使用してジッタピーキング現象と制御電圧にパターンジッタが大きくなる現象なく、所望の位相・周波数ロッキング動作を行う。

【解決手段】クロック同期化回路は、基準クロック信号とフィードバックされるフィードバッククロック信号の位相・周波数差を検出信号として出力する位相・周波数検出手段332と、検出信号に応答してチャージポンプ動作を行うチャージポンプ手段334と、チャージポンプ動作に応答して発振制御電圧を生成する制御電圧生成手段336と、発振制御電圧に対応してフィードバッククロック信号を生成する電圧制御発振手段338と、発振制御電圧に応答して自由発振周波数が設定され、基準クロック信号に同期化した内部クロック信号を生成するインジェクションロッキング発振手段310とを具備する。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

位相同期回路およびそれを用いた半導体集積回路装置

【課題】プロセスばらつき、環境変動によらず、所望の特性を満足する自動調整できる位相同期回路を提供すること。

【解決手段】位相同期回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ3、分周器6、セレクタ7、電圧制御発振器8を備えている。分周器6は、出力信号と基準信号を入力して出力信号を分周して帰還信号を出力するとともに出力信号から選択信号とトリミング信号とリミット信号を出力する。電圧制御発振器8は、制御電圧と基準電圧とトリミング信号とリミット信号を入力して制御電圧に応じて出力信号周波数を変え、出力信号の上限周波数を制限できるとともに、トリミング信号によって制御電圧に対して出力する出力信号の周波数感度と、リミット信号によって出力信号の上限周波数を変えることができる。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

スペクトラム拡散クロック生成器

【課題】その設計の困難性を低減することができるスペクトラム拡散クロック生成器を提供する。

【解決手段】スペクトラム拡散させたクロック信号CLKOを生成するスペクトラム拡散クロック生成器1において、クロック信号CLKOを所定の分周比で分周して、分周信号を出力する分周器14と、入力される基準クロック信号CLKRと分周信号CLKFの位相差に応じてレベルが変化させた位相差信号Spを出力する位相比較器10と、位相差信号Spに応じた発振制御信号Scを生成する発振制御信号生成器11と、発振部を有し、発振制御信号Scのレベルに応じた電流を発振部に供給して、発振制御信号Scのレベルに応じた発振周波数で発振部を発振させ、クロック信号CLKOを出力する電圧制御発振器12と、発振部に供給する電流を増減させる変調電流Imを生成し、電圧制御発振器12へ供給する変調電流生成器15とを備える。

(もっと読む)

21 - 40 / 115

[ Back to top ]