Fターム[5J106QQ07]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、機能 (379) | ノイズ除去、S/N比の向上 (154) | ジッタ除去 (35)

Fターム[5J106QQ07]に分類される特許

1 - 20 / 35

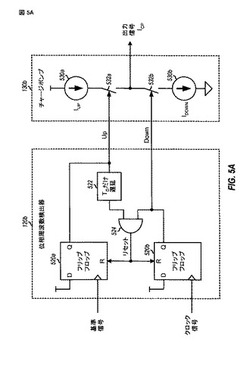

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を含むSSCG回路であって、出力クロック信号のジッタを低減する。

【解決手段】SSCG回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた第1の移相量で変化させるように、さらに、所定の範囲内で周期的に変化する第2の移相量を第1の移相量に加算するように、位相選択回路6を制御する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

発振回路

【課題】従来の発振回路では、出力信号のジッタを抑制できない問題があった。

【解決手段】本発明の発振回路は、発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成するフィルタコンデンサCpumpと、発振周波数制御電圧Vcpに応じて出力する発振信号Foutの周波数を変動させる発振器30と、発振信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路40と、タイミング制御信号に基づき発振信号Foutの周期の長さに応じて連続的に電圧レベルが変化する周波数検出電圧Vcapを生成する周波数検出回路10と、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流を連続的に可変してフィルタコンデンサCpumpに出力する差動増幅器20と、を有する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

シンセサイザと、これを用いたシンセサイザモジュール、受信装置、及び電子機器

【課題】位相雑音の劣化の少ないシンセサイザを提供すること。

【解決手段】シンセサイザ1の制御部7は、発振器5に電圧を出力するループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻すことなく、温度を検出する温度検出部8の出力信号に基づいて分周器6の分周比を変化させる。これにより、シンセサイザ1は、温度変化に対応して制御部7が分周器6の制御を行う場合、ループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻さないので、発振器5の発振周波数が大きく変動することを抑制し、これにより、シンセサイザ1における位相雑音を低減させることができる。

(もっと読む)

位相同期回路及び位相同期方法

【課題】低品質の入力光信号に対しても、安定して同期信号を発生するとともに、入力光信号が有するクロック信号に対する位相誤差検出感度を高くし、同期信号のタイミングジッタを低減し、製造コストを削減することである。

【解決手段】位相同期回路10は、基準信号を発生する基準信号発生部22と、入力光信号と電気信号とを位相比較して第1の位相誤差信号を生成する光位相比較部1と、第1の位相誤差信号と、基準信号と、を位相比較して第2の位相誤差信号を生成し、第2の位相誤差信号における入力光信号のクロック信号周波数に対応する周波数成分のみに応じて入力光信号の位相に同期した出力信号を発生して出力する位相同期部2と、基準信号の分周信号を用いて、位相同期部2から出力された同期信号をSSB変調して電気信号として光位相比較部1に出力する変調部3と、を備える。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

基準クロック信号生成装置

【課題】

デジタル映像信号処理で必要となる所定周波数の基準クロック信号を得る手法として、ジッター発生要因を有する手法を用いた場合でも、このジッターに起因する画質劣化や音質劣化を出来る限り目立たなくすることを可能とする装置を提供する。

【解決手段】

映像信号や音声信号の信号レベルが低い期間か否かを検出し、信号レベルが低くない期間は、クロック信号を生成するPLL回路の構成要素である帰還分周器5の分周比率を固定値とし、信号レベルが低い期間は、帰還分周器5の分周比率を可変して、これら各期間よりも十分に長い期間で積分すると、全体的にみれば所定周波数となる基準クロック信号を生成する。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

1 - 20 / 35

[ Back to top ]