Fターム[5J106RR14]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 記憶装置 (25)

Fターム[5J106RR14]に分類される特許

1 - 20 / 25

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

発振器

【課題】フロア雑音または位相雑音を抑えることができ、かつ分周器の分周比の設定に手間がかからない発振器を提供すること。

【解決手段】周波数シンセサイザの出力信号を順次分周する複数の分周器と、前記複数の分周器における最終段の分周器から目的とする周波数が得られるように、当該複数の分周器の各々について、入力周波数と分周比との組み合わせを複数設定すると共に各組み合わせ毎に、各段の分周器の出力信号のフロア雑音または位相雑音の大きさを記載した分周特性データを記憶する記憶部と、前記記憶部に記憶されている分周特性データに基づいて、各分周器の許容入力周波数の範囲内でありかつ最終段の分周器からの出力信号のフロア雑音または位相雑音が良好な入力周波数と分周比との組み合わせを判断して選択する選択部と、を備えるように発振器を構成する。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

PLL回路

【課題】 全てのチャンネルについてスプリアス特性が良好なVCO出力を得ることができ、温度変化による特性変動を抑えることができるPLL回路を提供する。

【解決手段】 制御回路3が、温度センサ31と、温度に応じてチャンネル番号毎に電圧制御発振器の出力におけるスプリアス特性が良好となる分周比を記憶した分周比テーブル32とを備え、温度センサ31で検出された温度及び入力されたチャンネル番号に対応する分周比を分周比テーブル32から読み取って、PLLIC2に設定すると共に、DDS回路(基準周波数生成回路)4にチャンネル番号と分周比とを設定し、DDS回路4が、チャンネル番号と分周比に基いて基準周波数の値を算出して、当該値に対応する基準周波数を生成するPLL回路としている。

(もっと読む)

周波数出力装置の内部基準信号源を校正する方法

【課題】簡便な手法で正確な校正を行うことが可能な周波数シンセサイザの内部基準信号を校正する方法を提供する。

【解決手段】基準クロック信号と周波数設定信号とに基づいて、設定された周波数信号を出力する周波数シンセサイザ1の、前記基準クロック信号を出力する内部基準信号源16を校正する手法において、前記周波数シンセサイザ1を周波数設定信号に基づいて動作させ、その出力周波数を周波数測定装置3により測定する工程と、測定された出力周波数と前記周波数設定信号により決定される周波数設定値との周波数差に基づいて、外部制御機器2により、周波数シンセサイザ1の不揮発性メモリ17に記憶されている指令値を増減して最適な指令値とする工程と、を含む。

(もっと読む)

周波数シンセサイザ装置及びその制御値決定方法

【課題】特性に優れた発振出力を得る。

【解決手段】 発振周波数の粗調整のための第1の可変容量部及び前記発振周波数の微調整のための第2の可変容量部によって前記発振周波数が可変の電圧制御発振器14と、前記第1及び第2の可変容量部を制御して前記電圧制御発振器の発振周波数を所望の周波数にするPLL回路14と、前記粗調整時において前記第2の可変容量部の容量を制御するための制御値を記憶するメモリ13と、を具備したことを特徴とする。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】周波数制御に起因したスプリアスの発生を抑え、受信特性の良好な受信装置を実現可能なシンセサイザと、これを用いた受信装置、及び電子機器を提供すること。

【解決手段】本発明のシンセサイザは、MEMS振動子14から出力された基準発振信号を基に局部発振信号を生成しこれを周波数変換器18に入力するシンセサイザ部16と、このシンセサイザ部16から出力される局部発振信号の周波数調整を行う制御部7とを備え、この制御部7による周波数調整時に、周波数変換器18からの出力信号の品質が品質限界閾値となる、シンセサイザ部16の周波数調整単位を所定値Fとすると、シンセサイザ部16の周波数調整単位Δfcontを所定値F以内とした構成である。

(もっと読む)

シンセサイザまたは発振器モジュールと、このシンセサイザを用いたシンセサイザモジュール、受信装置、及び電子機器、ならびに分周器の分周比の制御方法

【課題】制御部による分周器の制御に起因したノイズの発生を抑え、受信特性の良好な受信機を実現可能なシンセサイザを提供することを目的とする。

【解決手段】制御部7は、温度を検出する温度検出部8の出力信号に基づいて第2の分周器6へ適当な整数分周数Mや分数分周数Nの制御信号を送り、第2の分周器6の分周比を変化させる。つまり、第2の分周器6は、分周数Mが入力される整数部分と、分周数Nが入力される分数部分により構成される。制御部7は、温度を検出する温度検出部8の温度信号に基づいて第2分周器6の分周比を不均一な時間間隔で変化させる。これにより、第2分周器6の制御に伴い特定周波数に多数発生するノイズを抑圧することができ、シンセサイザの位相雑音を低減することができる。

(もっと読む)

マイクロプロセッサー用の位相ロックループの動的周波数スケーリングの方法と装置

複数個の発振器複合体を使用する位相ロックループが開示される。位相ロックループは、クロック出力と、出力信号を発生するように動作可能な複数個の発振器複合体を含んでいる。位相ロックループは、さらに、複数個の発振器複合体のうち1個の出力信号を選択して、クロック出力に結合するように構成された制御ロジックを含んでいる。  (もっと読む)

(もっと読む)

信号発生装置

【課題】本発明では、汎用DDSを使用した周波数可変の信号発生装置において、ジッター発生を抑制し、高精度の周波数可変の矩形パルス信号を発生する。

【解決手段】周波数可変の信号発生装置は、設定値に応じて変更される周波数のアナログ信号を出力するDDS1と、該アナログ信号から該周波数の第1矩形パルス信号を生成するコンパレータ3と、第1矩形パルス信号を設定される分周比で分周した第2矩形パルス信号を出力するプログラマブル分周器41と、制御部4とを備える。該周波数を高周波数領域側に変更の場合、該分周器に対し第1矩形パルス信号を出力信号Soとする。該周波数を低周波数領域側に変更の場合、DDSに対して設定値を分周比倍の値に変更制御して該分周比倍の周波数を有する第1矩形パルス信号を発生させ、分周器において当該分周比で分周した当該周波数の第2矩形パルス信号を出力信号Soとする。

(もっと読む)

複数の通信システムのための基準信号生成

【課題】複数の通信システムのための基準信号を生成する技術について説明する。

【解決手段】装置は基準発振器、周波数制御部及び複数の周波数シンセサイザを含む。基準発振器は、水晶発振器または他のある形式の発振器であり、主基準信号を生成する。周波数制御部は、主基準信号の周波数誤差を推定し、周波数誤差推定値を出力する。複数の周波数シンセサイザは、主基準信号を受け取り、複数のシステムのための複数のシステム基準信号を生成する。少なくとも一つの(例えば各々の)周波数シンセサイザは、周波数制御部からの周波数誤差推定値に基づいて主基準信号の周波数誤差を補正する。各周波数シンセサイザは、位相同期ループ(PLL)のための分周器制御信号を生成するために使用されるシグマ・デルタ変調器を含む。分周器制御信号は、主基準信号の周波数誤差を補正する。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

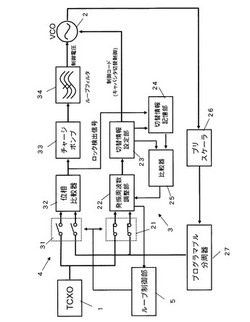

AM/FM受信機用PLLシンセサイザ回路とその切り替え方法

【課題】AM受信時とFM受信時の交差周波数を制御することでS/N特性を向上させるPLLシンセサイザ回路を提供する。

【解決手段】基準信号とPLLシンセサイザ回路の出力信号を分周した分周信号との間の位相差に応じた位相差信号を生成する位相比較回路と、位相差信号に基づいて電流制御をするとともに、AMで使用する場合とFMで使用する場合で電流制御を切替えてチャージポンプ信号を生成するチャージポンプ回路と、AMで使用する場合とFMで使用する場合で、チャージポンプ回路の電流制御を切り替えるためのレジスタ回路と、チャージポンプ信号を入力し平滑化して制御電圧として制御電圧信号に応じた周波数で発振して局部発振信号を出力するVCO回路と、局部発振信号を分周して分周信号として出力する分周回路と、を具備するAM/FM受信機用PLLシンセサイザ回路である。

(もっと読む)

周波数シンセサイザ、通信機、及び周波数シンセサイズ方法

【課題】高精度のクロックを高速に切り換えることの出来る周波数シンセサイザ、通信機、及び周波数シンセサイズ方法を提供する。

【解決手段】高精度に生成された基準クロックを元に、デジタル的な演算とD/Aコンバータ、ローパスフィルタを用いて所望の周波数の正弦波信号を発生させ、その正弦波信号を元の基準クロックとミキシングし、適切なフィルタを通す事で所望の周波数の正弦波を生成する事ができる。また、ミキシング後のバンドパスフィルタの中心周波数や、上記正弦波信号を発生させる演算処理、あるいは出力部のセレクタを変化させる事で、基準クロックの周波数を変更する事無く周波数切り換えを行うので、高速な周波数切り換えを実現する事ができる。周波数生成に用いる正弦波信号はデジタル的な演算によって生成されるので、周波数制御を精度良く行う事ができる。

(もっと読む)

多重周波数源システム及び動作方法

多重周波数源システムが、既定の目標周波数に同調可能な少なくとも1つの周波数源と、目標周波数より高い、又は低い周波数の第2の信号を生成するように動作する少なくとも1つの追加周波数源を含む。同調可能周波数源を、第2の信号の同時生成の間に目標周波数に同調させる方法は、(i)第2の信号の周波数が目標周波数より高いときに、同調可能周波数源を、目標周波数より低い少なくとも1つの周波数点周波数に同調するように制御し、その後、発振器を目標周波数に同調するように制御すること、又は(ii)第2の信号の周波数が目標周波数より低いときに、同調可能周波数源を、目標周波数より高い少なくとも1つの周波数点に同調するように制御し、その後、同調可能周波数源を、目標周波数に同調するように制御することを含む。 (もっと読む)

プログラム分周型分数PLL周波数シンセサイザの分周数列の計算機およびプログラム分周型分数PLL周波数シンセサイザ

【課題】分数PLL周波数シンセサイザにおいて、出力信号の位相雑音を小さくする。

【解決手段】分数PLLにおける分周器の一連の整数分周数を記憶装置に予め格納しておき、逐次読み出して設定するようにする。一連の整数分周数は、遺伝アルゴリズムを用いて、最適に近いものを計算しておく。一連の整数分周数の各値を遺伝アルゴリズムにおける遺伝子とすることにより、一連の整数分周数に対する拘束条件を満たしながら世代交代を行なうことができ、効率よく最適化計算を実行できる。

(もっと読む)

1 - 20 / 25

[ Back to top ]