Fターム[5J500AA41]の内容

Fターム[5J500AA41]に分類される特許

141 - 160 / 2,548

増幅回路および窒化物半導体装置

【課題】大電力入力時に、出力電力の低下またはゲインの低下を抑制し、かつドレインアイドル電流のドリフトが生じた場合に、ゲインの低下またはひずみ特性の劣化を抑制すること。

【解決手段】Si基板またはSiC基板と前記Si基板またはSiC基板上に形成された窒化物半導体層とを有し、かつ高周波信号がゲート端子に入力されるFET10からなるパワーアンプ11と、前記パワーアンプのドレインアイドル電流を検出する検出部12と、前記検出されたドレインアイドル電流が所定値より小さい場合は、前記ドレインアイドル電流に応じたゲートバイアス電圧を前記パワーアンプのゲート端子に出力し、前記検出されたドレインアイドル電流が所定値以上の場合は、固定値のゲートバイアス電圧を前記パワーアンプのゲート端子に出力する制御部14と、を具備する増幅回路

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】駆動用アンプのゲインが変動するのをなるべく抑えて差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、PWM回路22のランプ波発生回路61は、圧電スピーカー15の両端子間の電圧変化分ΔVn(V)に含まれる、インダクタ42にエネルギーをチャージする元のキャパシタ41の両端子間の電圧値Vlp(V)の成分と、圧電スピーカー15の両端子間の電圧値Vn−1(V)=Vspk(V)の成分とを打ち消すような傾きkをもち、かつ、その傾きkにチャージ時間t(μS)の二乗が乗じられた二次のランプ波を発生させる。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 蓄積手段に蓄積された電圧が無駄に放電されることを防止する。

【解決手段】 コンパレータCOMP1の出力がハイレベルのときに、コンデンサC3は、コンデンサC1の電圧によって充電される。次に、コンパレータCOMP1の出力がローレベルのときに、コンデンサC3の電圧が定電流Iの生成に使用される。同様に、コンパレータCOMP2の出力がハイレベルのときに、コンデンサC4は、コンデンサC2の電圧によって充電される。コンパレータCOMP2の出力がローレベルのときに、コンデンサC4の電圧が定電流Iの生成に使用される。従って、コンデンサC1、C2の電圧が無駄に放電されることが無く、定電流Iの生成に再度利用することができる。

(もっと読む)

電力増幅器

【課題】出力電力に応じて高電力モードおよび低電力モードを切り替え可能で、FETの製造ばらつきを両モードで補償可能な電力増幅器を提供する。

【解決手段】本発明の電力増幅器によれば、高電力モードおよび低電力モードで回路状態を切り替えることによって、バイアス回路部に供給される基準電圧を切り替え、トランジスタのばらつきを補償する。低電力モードでは電源電圧が基準電圧の1/2となるように調整し、高電力モードでは基準電圧をバイアス回路部に伝達する抵抗の値を調整することでアイドル電流の調整を実現する。

(もっと読む)

電力増幅器および電力増幅方法

【課題】ACLRが劣化しないTDD方式用の無線送信用電力増幅器および電力増幅方法を提供する。

【解決手段】終段増幅器5は、受信タイミングにはDCオフセット信号が入力され、送信タイミングには、入力される前記デジタル変調信号を電力増幅してアンテナへ向けて出力し、制御電源部23は、TDD送信タイミングに合わせて終段増幅器5のFETのドレインへ最大ピーク電圧のハイレベルのドレイン電圧およびそのFETがONとなるバイアス電圧と、TDD受信タイミングに合わせて前記FETのドレインへ低電圧のローレベルのドレイン電圧とそのFETがONとなるバイアス電圧とを供給する。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

衛星信号生成ユニットによって生成された信号を増幅するためのシステム

【課題】スペクトル占有を制限できる増幅するシステムを提供する。

【解決手段】−有限インパルス応答を伴う第1の帯域通過デジタルフィルタF1および第1のデジタル/アナログコンバータCNA1を備える第1の経路V1と、−周波数置換手段MTFと、−増幅装置DAと、を備えるシステムにおいて、−有限インパルス応答を伴う第2の帯域通過デジタルフィルタF2、前記第2のデジタルフィルタF2の出力側に配置されたゲイン手段G、位相従属型の数値制御式発振器NCO、および第2のデジタル/アナログコンバータCNA2を備える第2の経路V2と、−前記第1および第2の経路V1、V2の信号を合計するための再結合装置Sと、をさらに備える。

(もっと読む)

電力増幅器および増幅制御方法

【課題】 バックオフが最小化されC/Nの良い電力増幅器とその信号ピークレベル調整方法を提供する。

【解決手段】。CFR部1の入出力と、DPD部2の出力とアンテナへ出力される信号のループバック信号とのCCDFをCCDFモニタ部11、13、22、24でそれぞれ測定し、CCDFモニタ部24で測定したCCDFのPAPRがCCDFモニタ部13のそれよりも狭くならないようにピーク設定部14と、ピーク調整部12を制御する。

(もっと読む)

スイッチングアンプ

【課題】 簡単な回路構成であり、かつ、正確に、電源電圧のパンピング現象、および、出力電圧の直流成分を検出すること。

【解決手段】 トランジスタQ1は、スイッチングアンプの出力電圧に正の直流電圧が含まれることを検出する機能と、正側電源電圧+VBにパンピング現象が生じていることを検出する機能とを兼有する。トランジスタQ2は、スイッチングアンプの出力電圧に負の直流電圧が含まれることを検出する機能と、負側電源電圧−VBにパンピング現象が生じていることを検出する機能とを兼有する。パンピング現象が生じていない場合、ツェナーダイオードD1、D2は共にオフ状態である。従って、抵抗R4、R5が、直流電圧検出の精度の低下を防止できる。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

可変出力増幅器

【課題】低出力時の回路損失を低減し、低出力時の効率を高める可変出力増幅器を得る。

【解決手段】トランジスタ5と共に並列接続されたトランジスタ11と、信号出力される平均電力レベルを所定の値よりも小さくするときには、トランジスタ5のみ動作するようにバイアス電圧を印加し、信号出力される平均電力レベルを所定の値よりも大きくするときには、トランジスタ5,11の両方が動作するようにバイアス電圧を印加するバイアス制御回路12とを備えた。

このように構成したことにより、低出力時および高出力時に関わらずバイパス経路を用いずに、トランジスタ5,11の信号出力をそのまま出力するため、低出力時の回路損失を低減し、低出力時の効率を高めることができる。

(もっと読む)

ドライバ集積化回路

【課題】プロセスの耐圧を超える電圧が出力でき、要求される装置性能(高速・高電圧)を満足するドライバ集積化回路の構成を提供する。

【解決手段】差動入力回路と、レベルシフト回路と、出力回路が、同一のプロセスで製造され、基板電位(サブ電位)が異なる、3つ以上のチップに分割配置されており、それぞれのチップの基板印加電圧が異なるように設定することにより、プロセス耐圧よりも大きい出力電圧を提供する。

(もっと読む)

半導体集積回路およびその試験方法

【課題】 半導体試験装置を利用して、短い所要時間でD級増幅器の出力パルスの周波数に関する判定を行うことが可能な半導体集積回路を提供する。

【解決手段】 半導体集積回路1は、D級増幅器100と、セレクタ140と、カウンタ150とを有する。カウンタ150は、セレクタ140によって選択された出力信号OUTPまたはOUTMをモニタ対象パルスとし、リセット信号RSTの解除後、所定個数のモニタ対象パルスをカウントしたときに出力端子からカウント終了信号COを出力する。従って、リセット信号RSTの解除から所定時間経過した後の所定期間内にカウント終了信号COが出力されるか否かを判定することにより、D級増幅器100の出力信号の周波数が適正範囲内にあるか否かを判定することができる。

(もっと読む)

増幅回路ならびにそれを用いた送信装置および通信装置

【課題】 デューティ比が変化する入力信号を高効率で増幅することが可能な増幅回路ならびにそれを用いた送信装置および通信装置を提供する。

【解決手段】 デューティ比が変化するパルス波状の第1信号が入力されて、第1信号を増幅した第2信号を出力するトランジスタ回路10と、第2信号が入力されて、第1信号の基本波と周波数が等しい第3信号を出力する出力回路30とを有しており、出力回路30は、第1信号の基本波の周波数を含む通過帯域を有するとともに、第1信号のデューティ比が小さくなるにつれて通過帯域の幅が大きくなる帯域通過フィルタ31と、帯域通過フィルタ31とトランジスタ回路10とのインピーダンスを整合させる整合回路とを有する増幅回路ならびにそれを用いた送信装置および通信装置とする。デューティ比が変化する入力信号を高効率で増幅できる増幅回路ならびに消費電力が小さい送信装置および通信装置を得ることができる。

(もっと読む)

増幅装置、送信機、及び増幅装置制御方法

【課題】電流が規定値を維持する増幅装置、送信機、及び増幅装置制御方法を提供する。

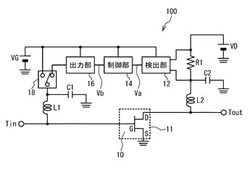

【解決手段】電力増幅装置100は、RF増幅用GaNデバイス118と、モニタ用GaNデバイス106と、Idq検出回路112と、ゲートバイアス制御(GBC)回路119とを有する。RF増幅用GaNデバイス118は、入力信号を増幅して出力する。モニタ用GaNデバイス106は、RF増幅用GaNデバイス118の入出力信号をモニタするための増幅デバイスである。Idq検出回路112は、RF増幅用GaNデバイス118に入力される入力信号から分岐してモニタ用GaNデバイス106に入力される入力信号に対応し、モニタ用GaNデバイス106が出力する出力信号を、検出する。ゲートバイアス制御回路119は、Idq検出回路112により検出された出力信号に応じて、RF増幅用GaNデバイス118に印加するゲート電圧を制御する。

(もっと読む)

電力増幅器

【課題】中低出力動作時でも動作効率を十分に向上させることができる電力増幅器を得る。

【解決手段】増幅素子Tr1,Tr2のベースには入力信号が入力され、コレクタにはコレクタ電圧が印加され、エミッタは接地されている。バイアス回路Bias1,Bias2は、バイアス電流を増幅素子Tr1,Tr2のベースに供給する。バイアス回路Bias1,Bias2は、コレクタ電圧が所定の閾値より低くなるとバイアス電流を低減させるバイアス電流低減回路12を有する。

(もっと読む)

電力増幅器の故障検出回路

【課題】増幅素子が4つ以上であっても予め定められた数の増幅素子が故障したときに、故障として検知する電力増幅器の故障検出回路を提供する。

【解決手段】4つ以上の増幅素子に対してこの増幅素子ごとに設けられる増幅素子故障検出回路の出力信号の加算電圧を反転して出力する反転加算回路と、この反転加算回路の出力電圧が閾値電圧より高い場合に信号を出力する比較回路と、を備える。故障した増幅素子の個数が故障増幅素子数閾値を超えた時、故障検出回路はLow信号を出力する。

(もっと読む)

周波数特性補正送信機

【課題】帯域内および帯域外を含む所望の帯域の周波数特性を瞬時に精度良く測定し、これを補正することで、EVMおよび周波数歪みを精度良く改善する周波数特性補正送信機を得る。

【解決手段】変調波信号源1に加えて、マルチキャリア信号源2を備え、さらに、変調波信号源1より発生される変調波信号またはマルチキャリア信号源2より発生されるマルチキャリア信号を選択する入力信号切替部4を備えた。

周波数特性測定モードでは、入力信号切替部4によりマルチキャリア信号を選択し、各構成要素にマルチキャリア信号が流れる。

ここで、マルチキャリア信号は、帯域内および帯域外を含む広帯域に渡って信号レベルが均一であることから、周波数特性比較部13および周波数特性補正部5では、該マルチキャリア信号に対応した広帯域に渡る周波数特性を瞬時に精度良く測定し補正することができる。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

バイアス回路を備えたパワーアンプ装置

【課題】ゲート電圧固定バイアス制御方式の歪み特性に優れている利点と、オートバイアス制御方式の個体差や温度変化によらずオペレーションのセット電流値を一定にすることが出来る利点を兼ね備えたパワーアンプ装置を提供する。

【解決手段】FETによる初段アンプ、後段アンプを含むパワーアンプと、入力段に第1のモニター抵抗を接続したオートバイアス回路とを備える。前記オートバイアス回路は前記初段アンプにだけオートバイアスを組み込むために、前記初段アンプ、後段アンプにそれぞれ、前記初段アンプのドレイン電流が一定になるようにセットされたゲート電圧がかかるように接続構成すると共に、主電源の電圧から前記初段アンプには前記第1のモニター抵抗を経由してドレイン電圧がかかり、かつ前記後段アンプには前記主電源の電圧を前記第1のモニター抵抗で分圧したドレイン電圧がかかるように接続構成した。

(もっと読む)

141 - 160 / 2,548

[ Back to top ]