Fターム[5J500AK01]の内容

Fターム[5J500AK01]に分類される特許

81 - 100 / 1,028

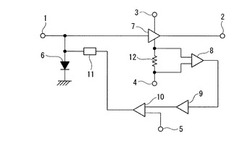

送信電力制御回路

【課題】低消費電力を実現する低コストの送信電力制御回路を提供する。

【解決手段】入力された入力信号を減衰させる利得調整手段(PINダイオード6)と、前記利得調整手段の出力信号を増幅する増幅手段(増幅器7)とからなる送信電力制御回路において、前記増幅手段のドレインバイアス供給端子(ドレインバイアス供給端子4)へ供給するドレイン電流に応じて前記利得調整手段の減衰量を制御することを特徴とする。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】 仮想接地ノードの電位に誤差が生じた場合でも制御性良く動作する低消費電力のスイッチトキャパシタ型積分器を提供する。

【解決手段】 入力信号の電荷をサンプリングするサンプリングキャパシタC1と、サンプリングキャパシタC1の電荷を仮想接地ノード4を介して蓄積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1、MN1と、そのゲート端子と仮想接地ノード4との間に挿入された校正キャパシタC3,C4と、校正キャパシタC3,C4に対して、仮想接地ノード4が基準電位Vcmとなる電位差が生じるように電荷を供給する校正装置12と、仮想接地ノードの電位を増幅した電位を主トランジスタMP1,MN1に出力する増幅器とを備える。

(もっと読む)

入れ子状のトランスインピーダンス増幅器

【課題】光ファイバ受信器やハードディスクドライブ向けに、大きい帯域幅及び高利得TIAを提供する。

【解決手段】入れ子状のトランスインピーダンス増幅器(TIA)回路は、入力及び出力を有する0次のTIAと、第1の演算増幅器(オペアンプ)と、を備えている。オペアンプは、0次のTIAの出力に接続する入力と、該入力によって駆動される第1のトランジスタと、第1のバイアス電圧によって駆動され且つ上記第1のトランジスタに接続する第2のトランジスタと、第2のトランジスタに接続する第1の電流源と、第1のトランジスタと第2のトランジスタの間のノードに存在する出力と、を備えている。

(もっと読む)

D級増幅回路

【課題】入力信号を適切に減衰させるとともに減衰時にも音量を変化させる

【解決手段】増幅部20は、入力端12pおよび12nの各々に互いに逆相で供給される入力信号SpおよびSnに応じてパルス幅変調された出力信号QpおよびQnを生成する。第1減衰部30は、トランジスタTR1と電圧印加回路32とを含む。トランジスタTR1は、入力端12pから増幅部20に至る入力経路16aと入力端12nから増幅部20に至る入力経路16bとの間に介挿される。電圧印加回路32は、入力信号SpおよびSnのレベルが所定値を上回る範囲で増加するほどトランジスタTR1の両端間に流れる電流が増加するように、所定値に対応する制御電圧VCをトランジスタTR1の制御端子に印加する。

(もっと読む)

双方向駆動回路

【課題】

PWM制御を行うことなく、簡単な構成でHブリッジ回路を駆動する。

【解決手段】

制御信号Vsが与えられ、前記制御信号Vsを前記基準値refに対して非反転増幅するアンプ11および反転増幅するアンプ12を備えるHブリッジ制御部10と、Hブリッジ回路20とを備え、前記非反転増幅された制御信号Vsが、第1トランジスタ21、第4トランジスタ24に入力され、前記反転増幅された制御信号Vsが、第2トランジスタ22、第3トランジスタ23に入力される。第1トランジスタ21と第4トランジスタ24のうち、一方がリニア動作するとき他方が飽和動作し、また、前記第2トランジスタ22と第3トランジスタ23のうち、一方がリニア動作するとき他方が飽和動作するように構成する。

(もっと読む)

電源回路

【課題】電力変換効率を改善する電源回路を提供する。

【解決手段】出力端子(ノードA)から電源電圧を出力する電源回路で、スイッチ131〜134と直流電圧源121〜124とダイオード141〜144が直列に接続されダイオードの一端が出力端子側と接続された回路部を1つのブロックとして、複数のブロックが、隣接する異なるブロックのうちの出力端子側のブロックのダイオードの他端ともう一方のブロックとが接続されるように、接続されて構成された電源電圧生成回路を備え、電源電圧制御手段161が、所定の参照信号の信号レベルに応じて、電源電圧生成回路を構成する複数のブロックのスイッチについてオン/オフを制御することで、電源電圧生成回路から出力される電源電圧を制御する。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

アンプ回路とそれを備える充電または放電制御回路とその制御方法

【課題】制御開始のタイムラグを低減したアンプ回路とそれを備える充電または放電制御回路とその制御方法とを提供することを目的とする。

【解決手段】誤差アンプと、誤差アンプの出力にベースが接続されたトランジスタと、トランジスタのコレクタとエミッタとの間に接続された負荷と、誤差アンプの出力と誤差アンプのマイナス側入力との間に接続された位相補償コンデンサと、を備えるアンプ回路において、位相補償コンデンサと直列に接続されたフォトモススイッチを備え、フォトモススイッチは、トランジスタのベース電流の有無に対応してオン・オフが制御されるアンプ回路とする。

(もっと読む)

音声増幅回路およびそれを具備する撮像装置または撮像装置の周辺機器

【課題】MIC増幅回路における雑音と歪とを低減する。

【課題を解決するための手段】基板実装型MICコネクタを実装した第一の基板に、電源重畳回路と信号入力結合回路と入力音声増幅回路とを、表面実装部品の第一の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記信号入力結合回路は、前記第一の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記第一の基板と接続された第二の基板に電源発生部と平衡出力音声増幅回路とを第二の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記第二の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記平衡出力音声増幅回路の共通帰還回路がタンタル電解コンデンサの逆極性の直列接続または低歪率セラミックコンデンサで容量結合されたことを特徴とする音声増幅回路。

(もっと読む)

パワーアンプ回路と充放電制御装置

【課題】効率をさらに高めて損失を低減することが可能なパワーアンプ回路と充放電制御装置とを提供することを目的とする。

【解決手段】負荷に供給する電圧を制御するパワーアンプ回路において、負荷の状態に対応して正電圧を出力するとともに負荷の他の状態に対応して負電圧を出力する内部電源と、負荷の電圧を検出する負荷電圧検出部とを備え、負荷電圧検出部で検出した負荷電圧に基づいて、負荷に供給する内部電源の出力電圧をフィードバック制御するパワーアンプ回路とする。さらに好ましくは、負荷に供給する電圧を、負荷に流れる電流が一定になるように制御するパワーアンプ回路とする。

(もっと読む)

基準電流出力装置及び基準電流出力方法

【課題】基準電流の大きさを温度勾配を維持したまま調整することができる基準電流出力装置を提供する。

【解決手段】基準電圧・電流出力回路12により基準電流i3’を出力し、変換出力回路14により、基準電圧・電流出力回路12から出力された基準電圧を調整用電流i4に変換して出力し、重畳出力部16により、基準電流i3’に調整用電流i4を重畳して重畳電流i6を出力する。

(もっと読む)

信号増幅回路

【課題】入力電圧に比例した電流を出力するOTAの製造ばらつきおよび周囲温度の変化による利得の変化を抑制することが可能な信号増幅回路を提供する。

【解決手段】入力電圧Vinが入力される第1のOTA1、第1のコンデンサC1を有する第1の積分器10と、第1のコンデンサC1に並列接続された第1のアナログスイッチSW1と、入力電圧Vinの積分時間を調整する積分時間調整回路3とを備える。積分時間調整回路3は、第1の参照電圧Vref1が入力される第2のOTA2、第2のコンデンサC2を有する第2の積分器20と、第2のコンデンサC2に並列接続された第2のアナログスイッチSW2と、第2の積分器20の出力電圧と第2の参照電圧Vref2とを比較するコンパレータCP2とを備え、コンパレータCP2の出力に基づいて第1のアナログスイッチSW1、第2のアナログスイッチSW2それぞれを制御する第1の制御信号、第2の制御信号を出力する。

(もっと読む)

定電流回路

【課題】外付け抵抗の接続に不良が発生しても、正常な出力電流を得ることのできる定電流回路を提供する。

【解決手段】実施形態の定電流回路は、半導体集積回路に搭載され、出力電流を生成するカレントミラー回路103を備え、外部端子102に外付け抵抗Rextを接続することにより、カレントミラー回路103へ供給する基準電流Isが生成される定電流回路であって、オープン状態検出回路1が、外部端子102がオープン状態となったことを検出すると、代替回路2が、基準電流Isに相当する代替電流Iaをカレントミラー回路103へ供給する。

(もっと読む)

電圧発生装置、電流発生装置

【課題】出力電流の制限の精度を劣化させないでより高い電圧を発生させる。

【解決手段】本発明の電圧発生装置は、第1、第2、第3の入力増幅部と、第1、第2、第3の入力増幅部にそれぞれ設けられた飽和防止回路と、電流帰還手段と、電圧帰還手段と、出力増幅部と、ダイオードスイッチと、出力制御部を具備する。電流帰還手段は、電位が接地に近い方の負荷の端子に負荷と直列に接続された電流検出用抵抗の電圧を検出し、その検出した電圧を第1、第3の入力増幅部の入力側に帰還する。出力増幅部は、逆方向に電流が流れるように負荷に電圧を印加する第1の出力増幅器と、所定方向に電流が流れるように負荷に電圧を印加する第2の出力増幅器とを有する。出力制御部は、正出力端子と負出力端子の出力に応じて、第1の出力増幅器または第2の出力増幅器を選択し、制御する。

(もっと読む)

映像信号出力回路

【課題】 電源電圧や周囲温度が変動した場合にも、出力DCレベルがずれるのを回避するとともに、動作電源電圧範囲が広く電源リップルリジェクション特性の優れた映像ドライバを提供する。

【解決手段】 映像信号が入力される入力端子の電位をクランプするクランプ回路と、入力された映像信号および所定の基準電圧を入力とし映像信号を増幅して出力する差動増幅回路と、クランプ回路に供給するバイアス電圧および差動増幅回路に供給する基準電圧を生成する分圧回路と、分圧回路により生成されたバイアス電圧または基準電圧に所定のオフセット電圧を付加または減算してクランプ回路または差動増幅回路に供給するオフセット回路と、を備えた映像信号出力回路において、オフセット回路は、pnpバイポーラトランジスタおよびnpnバイポーラトランジスタを備え、2つのトランジスタのベース・エミッタ間電圧の差に応じた電圧を出力するように構成した。

(もっと読む)

電流電圧変換回路、物理量測定装置

【課題】 回路規模の増加を抑えつつ、高い精度の電流電圧変換を行い、低ノイズの電圧信号を出力する電流電圧変換回路等を提供する。

【解決手段】 電流電圧変換回路10であって、電圧信号101P、101Nを出力するオペアンプ20と、入力された電流信号100P、100NのDCオフセット電流に応じた電荷を充放電する第1のキャパシタ40P、40Nと、オペアンプのオフセット電圧に応じた電荷を充放電する第2のキャパシタ41P、41Nと、第1の期間においてオン状態となり第2の期間においてオフ状態となる第1のスイッチ30P、30Nおよび第3のスイッチ32P、32Nと、第1の期間においてオフ状態となり第2の期間においてオン状態となる第2のスイッチ31P、31Nとを含む。

(もっと読む)

パルス駆動回路

【課題】高周波増幅用のFETのドレインに印加されるパルス電圧の安定化を図る。

【解決手段】駆動用電源11の出力電圧に基づきMOS−FETQ1を駆動する。Q1はパルス信号源12から出力される基準パルス信号bでスイッチングさせ、Q1オン時は、コンデンサC1の電荷を移行させて得られる電圧でQ1を非飽和状態で駆動する。Q1のスイッチングによりソース電極に得られるパルス電圧を、ゲート電極に供給される高周波信号を増幅する高周波電力FETQ2の駆動電圧としてドレイン電極に印加する。Q2のドレイン電極に発生するパルス電圧dと基準パルス信号bの電圧をオペアンプOP2で比較し、Q1のゲート電極にフィードバックする。非飽和状態で駆動されるQ1にフィードバックさせたことで、Q1に印加されるパルス内ドレイン電圧の低下を防止することができる。

(もっと読む)

半導体装置及びこれを用いた電子機器

【課題】電源電圧のばらつきに依ることなく、入力信号を適切に電力増幅して出力信号を生成することが可能な半導体装置、及び、これを用いた電子機器を提供する。

【解決手段】半導体装置100は、VDDとGNDとの間でパルス駆動される入力信号Sinを増幅し、VCC(>VDD)とGNDとの間でパルス駆動される出力信号Soutを生成するドライバZ20と、VCCからVDDを生成するVDD生成部Z30と、を有するものであって、ドライバZ20は、VDDの入力を受けて動作し出力信号Soutの帰還経路となる1次積分器(AMP、R1、R2、C1)を含み、VDD生成部Z30は、VCCを分圧してVDDを生成する分圧器(R3、R4)を含む。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

利得切換型増幅器およびそれを用いたオーディオ機器

【課題】ポップノイズの発生を、再生時の音声品質を維持しつつ、防ぐ。

【解決手段】オペアンプ回路1の出力端子からの出力信号を、オペアンプ回路1の反転入力端子にフィードバックするフィードバック回路2を具備し、フィードバック回路2でフィードバックする帰還電圧を減衰することにより利得切換を行い、オペアンプ回路1に入力された入力信号の出力レベル調整を行う利得切換型増幅器において、オペアンプ回路1の非反転入力端子に、入力信号を減衰して入力するアッテネータ回路3を設け、このアッテネータ回路3の減衰率の設定とフィードバック回路2の減衰率の設定の組み合わせにより、信号出力レベルの切換分解能を上げることで、例えば音声出力レベルを連続的に変化させることを可能とし、ポップノイズの発生を防ぐ。

(もっと読む)

81 - 100 / 1,028

[ Back to top ]