Fターム[5J500AK29]の内容

Fターム[5J500AK29]に分類される特許

61 - 80 / 603

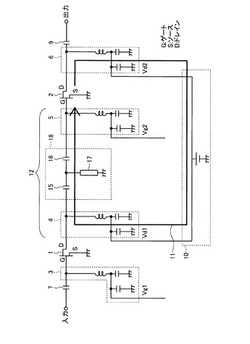

多段増幅器

【課題】低周波数帯域の利得を効果的に抑圧して発振の発生を抑制すると共に、回路の高密度実装を可能とする多段増幅器を提供する。

【解決手段】FET1,2に、ゲートバイアス電圧を印加する入力整合回路3,5と、FET1,2に、ドレインバイアス電圧を印加する出力整合回路4,6と、出力整合回路4と入力整合回路5との間に直列接続されたコンデンサ15,16、および、一端がコンデンサ15,16間の接続点に接続され他端が接地された誘導性の線路17を含み構成されたハイパスフィルタ18と、を備え、コンデンサ15,16のキャパシタンス値および線路17のインダクタンス値は、増幅素子の動作周波数よりも低い周波数帯域において、出力整合回路6と出力整合回路4とハイパスフィルタ18とを介して形成されるドレインバイアスループ11の損失が、FET2の利得よりも大きくなるように設定する。

(もっと読む)

AB級増幅器

【課題】広い帯域に亘って高線形性でかつ高効率なAB級増幅器を提供することにある。

【解決手段】本実施の形態に係るAB級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)を超えて2・π(rad)未満のAB増幅器において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

C級増幅器

【課題】高効率でかつ広帯域化されたC級増幅器を提供する。

【解決手段】本実施の形態に係るC級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)未満において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

AB級増幅器

【課題】広い帯域に亘って高線形性でかつ高効率なAB級増幅器を提供することにある。

【解決手段】本実施の形態に係るAB級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)を超えて2・π(rad)未満のAB増幅器において、増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2、3倍波の負荷インピーダンスをZ3=R3+j・X3とし、X1とR1の関係を−0.5・R1≦X1≦0.5・R1、R1をR1=Vdc/Imax・{1−cos(θo/2)}・π/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−2・{θo−sin(θo)}/{sin(θo/2)−sin(1.5・θo)/3}に、X3/X1をX3/X1={θo−sin(θo)}/{sin(θo)/3−sin(2・θo)/6}に、あるいはそれぞれの近傍にする。

(もっと読む)

増幅装置及び増幅装置の故障監視方法

【課題】増幅器の故障を確実に検出できる増幅装置及び増幅装置の故障監視方法を提供すること。

【解決手段】本発明の実施態様に係る増幅装置は、入力信号を分割する分配手段と、分配手段により分割された入力信号の一方を増幅するキャリア増幅器と、分配手段により分割された入力信号の他方を増幅するピーク増幅器と、キャリア増幅器からの出力信号とピーク増幅器からの出力信号を合成する合成器と、を有するドハティ増幅回路と、ピーク増幅器のゲートバイアス電圧を参照電圧と比較し、該比較結果に応じて信号を出力する第1の比較器と、第1の比較器から信号が出力されると、ピーク増幅器のドレインへの電力供給を遮断する第1のスイッチと、を具備する。

(もっと読む)

高周波用3ステージ窒化ガリウム系高電子移動度トランジスタ(GaNHEMT)ドハティ電力増幅器

【課題】窒化ガリウム系高電子移動度トランジスタ(GaN HEMT)電力素子を用いて広い範囲で高い効率を持つようにした高周波用3ステージ(Three−Stage)GaN HEMTドハティ電力増幅器を提供する。

【解決手段】そのための本発明は、キャリア増幅器及び第1及び第2のピーク増幅器を含む高周波用3ステージ窒化ガリウム系高電子移動度トランジスタドハティ電力増幅器において、前記キャリア増幅器と第1及び第2のピーク増幅器に入力信号を分配するための10dB電力分配器;前記キャリア増幅器の入力電力を調整するための第1の経路部;及び広い出力電力範囲で高い効率を維持させるための第2の経路部を含むことを特徴とする。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

高周波電力供給装置、プラズマ処理装置、及び半導体薄膜の製造方法

【課題】電力利用効率を向上できる高周波電力供給装置、プラズマ処理装置、及び半導体薄膜の製造方法を得ること。

【解決手段】高周波電力供給装置は、変動負荷に高周波電力を供給する高周波電力供給装置であって、高周波電源と、前記高周波電源と前記変動負荷との間に配され、前記変動負荷からの反射電力を分離するサーキュレータと、前記サーキュレータにより分離された反射電力の位相及び振幅を調整する調整部と、前記高周波電源から出力された電力と前記調整部により調整された反射電力とを合成して前記サーキュレータへ出力する電力合成部とを備えている。

(もっと読む)

2段のマイクロ波のE級電力増幅器

【課題】より広い周波数範囲で同時的な高電力と高電力付加効率(PAE)をもたらす改良されたE級増幅器を提供する。

【解決手段】2段のE級の高電力増幅器100は駆動装置段102、E級段間整合ネットワーク(ISMN)104、負荷回路を使用する高電力段106を含んでいる。負荷回路はスイッチングモード回路の出力に結合されている直列の誘導性−容量性ネットワークと、スイッチングモード回路の出力に結合されているキャパシタンスを提供するための回路を含んでいる。

(もっと読む)

インピーダンス整合回路、電力増幅器、低雑音増幅器及び無線通信機器

【課題】面積の増加を抑制しつつ、複数の周波数帯域の信号を対象としたインピーダンス整合が可能なインピーダンス整合回路を提供する。

【解決手段】本発明のインピーダンス整合回路1は、入出力端である一端2と他端3との間に直列に接続されるように構成された整合素子ブロック51及びスイッチ54と、一端2と他端3との間で、整合素子ブロック51及びスイッチ54に並列に接続されるように構成されたスイッチ55と、整合素子ブロック51とスイッチ54とを互いに接続するノードとグランドとの間に設けられるように構成されたスイッチ56と、を備える。

(もっと読む)

地上放送波受信用アンテナ装置及びその構成部品

【課題】FM帯以下の周波数帯域において、アンテナ素子長を55[mm]程度まで短縮しても、従来と同等以上の性能を有する地上放送波受信用アンテナ装置を提供する。

【解決手段】アンテナ素子10の受信波のうち当該アンテナ素子10の共振点以下の周波数の受信波を増幅する、受信周波数に対して等価雑音抵抗が2Ω以下となる化合物半導体HEMTとを含んで増幅器12−Aを構成し、雑音指数(NF)をFM帯以下の広い周波数帯域にわたってほぼ一定になるようにした。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

高周波半導体モジュール

【課題】段間の整合状態を観測して整合回路の調整を行うことのできる高周波半導体モジュールを提供する。

【解決手段】複数の半導体増幅素子7、8を直列に接続して増幅を行う多段型の高周波半導体モジュールであって、パッケージ3内に配置される回路基板4、5,6に、半導体増幅素子7、8間の段間における高周波信号をモニタするためのモニタ回路を具備する。

(もっと読む)

クロック入力インターフェース回路

【課題】低消費電力なクロック入力インターフェース回路を提供する。

【解決手段】クロック入力インターフェース回路1は、インピーダンス整合・出力電圧調整抵抗R11,R13と、出力電圧調整抵抗R12,R14と、電流安定化抵抗R15,R16と、反射防止終端抵抗R17と、DCレベル阻止容量C1,C2と、RFバイパス容量C3,C4と、電流源トランジスタQ1,Q2とから成る。クロック入力端子CKにクロック信号を入力する伝送線路とインピーダンス整合し、かつ次段の回路の入力端子で必要とされるDCバイアス電圧を出力端子OT,OCに与えることができるように、抵抗R11〜R14,R17の値および容量C1〜C4の値が設定される。

(もっと読む)

電力増幅合成回路ならびにそれを用いた電力増幅回路,送信装置および通信装置

【課題】 電源効率の高い電力増幅合成回路ならびにそれを用いた電力増幅回路,送信装置および通信装置を提供する。

【解決手段】 ソース端子に第1入力信号が、ゲート端子に第2入力信号と同相の信号が入力されるトランジスタ33と、ソース端子に第2入力信号が、ゲート端子に第1入力信号と同相の信号が入力されるトランジスタ34と、ゲート端子が第1のトランジスタのドレイン端子に接続され、ソース端子が定電流源6を介してグランド電位に接続されるトランジスタ4と、トランジスタ4のドレイン端子および電源電位を接続する低域通過フィルタ回路8と、トランジスタ4のドレイン端子に接続された出力整合回路16と、第1入力信号および第2入力信号の位相差が増加すると定電流源を流れる電流が減少するように定電流源を制御する電流制御信号を出力する電流制御回路19とを備える電力増幅合成回路とする。

(もっと読む)

高周波電力増幅器

【課題】従来よりも高効率で消費電力を抑えることが可能な高周波電力増幅器を提供する。

【解決手段】ソース接地され、ゲート端子が、信号が入力される入力ノードに接続された入力側トランジスタ10と、ゲート接地され、ソース端子が、入力側トランジスタ10のドレイン端子に共通に接続され、且つドレイン端子が、出力信号が出力される出力ノードに接続された複数の出力側トランジスタ20,30とを備え、各出力側トランジスタ20,30は、それぞれが異なるゲート・ソース間電圧によりバイアスされている構成とする。

(もっと読む)

高周波電力増幅器

【課題】高出力、高効率および広ダイナミックレンジを有する低歪みな高周波信号を出力する高周波電力増幅器を提供する。

【解決手段】高周波電力増幅器100であって、増幅用トランジスタ3と、増幅用トランジスタ3の後段に配置された増幅用トランジスタ4と、増幅用トランジスタ3のベースにバイアス電流I1を供給するバイアス回路11と、増幅用トランジスタ4のベースにバイアス電流I2を供給するバイアス回路12とを備え、バイアス回路11は、高周波出力信号の出力電力値が第1電力値のとき第1電流値の電流をバイアス電流I1とし、第1電力値よりも大きい第2電力値のとき第1電流値よりも小さい第2電流値の電流をバイアス電流I1とし、バイアス回路12は、高周波出力信号の出力電力値が第1電力値であるとき第3電流値の電流をバイアス電流I2とし、第2電力値であるとき第3電流値よりも大きい第4電流値の電流をバイアス電流I2とする。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

増幅回路

【課題】広い入力レベル範囲にわたって高い効率を実現することが可能な増幅回路を提供する。

【解決手段】増幅回路101において、入力側高調波整合回路3および出力側高調波整合回路4により、トランジスタTRの制御電極から前段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスと、トランジスタTRの導通電極から後段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスとが、それぞれ、対象信号のレベルが異なる条件下において整合されている。

(もっと読む)

電力増幅器

【課題】 段間に減衰器を設けた構成において、利得切換前後での入力反射損失の劣化を抑制しつつ利得を切り換えることができる電力増幅器を提供する。また、段間に減衰器を設けた構成において、利得切換前後での通過位相差の増大を抑制しつつ利得を切り換えることができる電力増幅器を提供する。

【解決手段】 IN、OUTはRF入力・出力端子であり、Tr1、Tr2はHBT(ヘテロ接合バイポーラトランジスタ)である。Fa1、Fa2はFET(電界効果トランジスタ)である。Cc1、Cc2はデカップリング容量であり、Vc1、Vc2はパワー段Tr1、Tr2のコレクタ電源端子であり、Ra1、Ra2、Raa2、Rg1、Rg2は抵抗であり、Cs1は段間整合容量であり、Cp1は減衰器の並列容量であり、Vg1、Vg2は減衰器の制御端子である。抵抗Ra1に直列に容量Ca1が設けられている。

(もっと読む)

61 - 80 / 603

[ Back to top ]