Fターム[5J500AK29]の内容

Fターム[5J500AK29]に分類される特許

41 - 60 / 603

バイアス回路を一体化した金属酸化膜半導体デバイス

【課題】デバイスの温度変動および/またはプロセス変動に起因するMOSデバイスのバイアス条件の変動を正確に補償できる技術を提供する。

【解決手段】ICデバイスがゲート端子、ソース端子およびドレイン端子を有するMOSデバイスを備え、ゲート端子はICデバイスの入力部に動作可能に結合され、ドレイン端子はICデバイスの出力部に動作可能に結合され、ソース端子は負電圧供給源に結合している。ICデバイスは、さらに、MOSデバイスのゲート端子に動作可能に結合されているバイアス発生器を備え、このバイアス発生器は、MOSデバイスにほぼ一定の静止動作点でバイアスをかけるバイアス電圧および/またはバイアス電流を発生する。バイアス発生器は、バイアス電圧および/またはバイアス電流がMOSデバイスの接合温度の関数として変化するように構成されている。このようにして、バイアス発生器が、MOSデバイスの1つまたは複数の動作条件を正確にたどり、それによってデバイスの性能を向上させる。

(もっと読む)

電力増幅回路

【課題】F級増幅器における効率を改善することができる電力増幅回路を提供する。

【解決手段】電力増幅回路は、予め定められた周波数の基本波を含む信号を増幅する増幅素子と、増幅素子が増幅した信号に含まれる基本波と、基本波の2倍波と、基本波の3倍波とそれぞれの特性インピーダンスとのインピーダンス整合をとる出力整合回路と、2倍波の反射位相を変化させる2倍波用チューナーと、3倍波の反射位相を変化させる3倍波用チューナーと、出力整合回路が出力する信号に含まれる基本波を通過させるとともに、信号に含まれる2倍波及び3倍波を反射する高調波反射フィルタであって、2倍波用チューナー及び3倍波用チューナーが接続され、2倍波用チューナー及び3倍波用チューナーを用いて2倍波及び3倍波の反射位相を独立に変化させる高調波反射フィルタとを備える。

(もっと読む)

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3a,M3bが接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M3a,M3bは、増幅素子Tr2の出力と接地点との間に直列に接続されたインダクタL5及びキャパシタC1を有する。インダクタL5とキャパシタC1を接続する接続点Xに、スイッチSW2の他端が接続されている。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

可変出力増幅器

【課題】低出力時の回路損失を低減し、低出力時の効率を高める可変出力増幅器を得る。

【解決手段】トランジスタ5と共に並列接続されたトランジスタ11と、信号出力される平均電力レベルを所定の値よりも小さくするときには、トランジスタ5のみ動作するようにバイアス電圧を印加し、信号出力される平均電力レベルを所定の値よりも大きくするときには、トランジスタ5,11の両方が動作するようにバイアス電圧を印加するバイアス制御回路12とを備えた。

このように構成したことにより、低出力時および高出力時に関わらずバイパス経路を用いずに、トランジスタ5,11の信号出力をそのまま出力するため、低出力時の回路損失を低減し、低出力時の効率を高めることができる。

(もっと読む)

増幅回路ならびにそれを用いた送信装置および通信装置

【課題】 デューティ比が変化する入力信号を高効率で増幅することが可能な増幅回路ならびにそれを用いた送信装置および通信装置を提供する。

【解決手段】 デューティ比が変化するパルス波状の第1信号が入力されて、第1信号を増幅した第2信号を出力するトランジスタ回路10と、第2信号が入力されて、第1信号の基本波と周波数が等しい第3信号を出力する出力回路30とを有しており、出力回路30は、第1信号の基本波の周波数を含む通過帯域を有するとともに、第1信号のデューティ比が小さくなるにつれて通過帯域の幅が大きくなる帯域通過フィルタ31と、帯域通過フィルタ31とトランジスタ回路10とのインピーダンスを整合させる整合回路とを有する増幅回路ならびにそれを用いた送信装置および通信装置とする。デューティ比が変化する入力信号を高効率で増幅できる増幅回路ならびに消費電力が小さい送信装置および通信装置を得ることができる。

(もっと読む)

高周波電力増幅器

【課題】インピーダンス整合の切り替えと経路の切り替えを同時に行うことができ、回路設計の自由度を向上させることができる高周波電力増幅器を得る。

【解決手段】トランジスタTr1は、外部から入力された高周波信号を増幅する。トランジスタTr2は、トランジスタTr1の出力信号を増幅する。トランジスタTr3は、トランジスタTr1と並列に接続され、外部から入力された高周波信号を増幅する。トランジスタTr1の出力とトランジスタTr2の入力との間に切り替え素子SW1が接続されている。トランジスタTr3の出力と切り替え素子SW1との間に切り替え素子SW2が接続されている。トランジスタTr1の出力及び切り替え素子SW2とトランジスタTr2の出力との間に切り替え素子SW3,SW4が直列に接続されている。切り替え素子SW3と切り替え素子SW4との間にキャパシタC1が接続されている。

(もっと読む)

リニアライザ

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

低雑音増幅器及び無線通信機

【課題】ゲインの切替えを行っても入力インピーダンスが変化することがなく安定した受信性能を得ることができる低雑音増幅器及び無線通信機を得る。

【解決手段】受信側のローノイズアンプ20を、ゲイン切替え機能を備えたアンプ部201と、アンプ部201をローゲインに設定したときのローノイズアンプ20の入力インピーダンスがハイゲインに設定したときの入力インピーダンスに合うようなインピーダンス素子202と、インピーダンス素子202のアンプ部201の入力端への接続/切り離しを行うスイッチ203とで構成し、アンプ部201をローゲインに設定したときにインピーダンス素子202をアンプ部201の入力端に接続するようにした。これにより、アンプ部201のゲインの切替えを行ってもローノイズアンプ20の入力インピーダンスを一定に保つことができる。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

電力増幅器

【課題】高調波信号が基本波増幅器に効率よく注入され、高効率化を図る電力増幅器を得る。

【解決手段】基本波増幅器3と、基本波増幅器3から発生する高調波信号を基本波信号から分波する第1分波回路と、第1分波回路から出力された高調波信号を基本波増幅器3の入力側又は出力側に注入するための高調波伝達回路15と、高調波伝達回路15から出力された高調波信号を基本波増幅器3に注入する第2分波回路とを備え、高調波信号を基本波増幅器3に注入し、基本波増幅器3の効率を高めるようにしたものである。

(もっと読む)

電力増幅器および通信装置

【課題】 温度変動や製造ばらつきに伴う利得変動を抑制する。

【解決手段】 電力増幅器は、信号を増幅する複数の増幅部が多段接続された増幅回路と、各増幅部にバイアス電圧を供給するバイアス供給回路とを有し、バイアス供給回路は、増幅部のトランスコンダクタンスを安定させるための第1モードでバイアス電圧を制御する第1バイアス回路と、増幅部のバイアス電流を安定させるための第2モードでバイアス電圧を制御する第2バイアス回路とを有し、複数の増幅部の少なくとも1つの増幅部のバイアス電圧は、第1モードで制御可能であり、複数の増幅部の残りの少なくとも1つの増幅部のバイアス電圧は、第2モードで制御可能である。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

ドハティ増幅器

【課題】2つのピーク増幅器のデバイス特性差による出力電流の違いから生ずる負荷変動の影響を低減して、相互変調歪み特性を改善すること。

【解決手段】分配回路により分配された第1の信号を増幅するキャリア増幅器と、キャリア増幅器の出力電力が飽和状態に近づいた場合に、上記分配された第2の信号を増幅する第1のピーク増幅器と、同分配された第3の信号を増幅する第2のピーク増幅器と、第1のピーク増幅器と第2のピーク増幅器との各出力信号を合成する第1の合成回路と、キャリア増幅器と第1の合成回路との各出力側のそれぞれから合成点に向かって整合を取ってキャリア増幅器と第1の合成回路との各出力信号を合成して出力する第2の合成回路とを具備し、第1の合成回路は、キャリア増幅器の出力の飽和時から所定の値だけバックオフしたバックオフ時に、合成点から第1及び第2のピーク増幅器側を見たインピーダンスを無限大に調整可能とする。

(もっと読む)

高出力電力増幅器

【課題】入力信号を4分配した分配信号をそれぞれ増幅させた後、これらの全ての分配信号を合成することにより高出力信号を出力するができるとともに、高出力電力増幅器を構成する回路全体の大きさを小型化することが可能な高出力電力増幅器を提供する。

【解決手段】高出力電力増幅器10は、1つの4合成型電力増幅回路11によって構成されている。4合成型電力増幅回路11は、位相差90°で2分配/2合成するハイブリッド回路22及び26と、位相差180°で2分配/2合成する平衡不平衡回路23(23a、23b)及び25(25a及び25b)と、電力増幅器24(24a〜24d)と、を備えている。

(もっと読む)

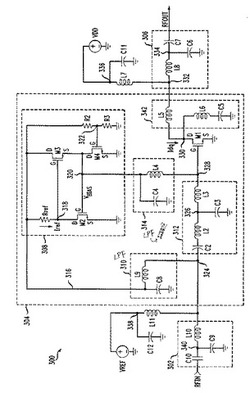

高周波電力増幅装置

【課題】トークカレントの低減または出力における位相偏差の低減を実現可能な高周波電力増幅装置を提供する。

【解決手段】例えば、トランジスタサイズが異なる複数の電力増幅用トランジスタQ1〜Q5と、複数のインピーダンス整合回路IMN14,IMN2i,IMN3i,IMN5i,IMN2o,IMN3o,IMN5o,IMNoを備え、電力指示信号Vrmpに応じて使用する信号経路を切り替える。高パワー時にはQ1→Q2の経路が使用され、中パワー時にはQ1→Q3の経路が使用され、低パワー時にはQ4→Q5の経路が使用される。ここで、当該高周波電力増幅装置は、各信号経路で経由する電力増幅用トランジスタの段数とインピーダンス整合回路の個数が等しくなるように構成される。

(もっと読む)

増幅回路

【課題】単相信号を高利得で増幅することができる小型の増幅回路を提供することを課題とする。

【解決手段】増幅回路は、第1のインダクタ(303)及び第2のインダクタ(304)が磁気結合されている第1のトランスフォーマ(306)と、ゲートが前記第1のインダクタ(303)を介して第1の入力ノード(N1)に接続され、ドレインが前記第2のインダクタ(304)を介してドレインバイアス電位ノード(Vd)に接続され、ソースが基準電位ノードに接続される第1の電界効果トランジスタ(305)と、前記第1の電界効果トランジスタ(305)のドレインに接続される第1の出力ノード(OUT)とを有する。

(もっと読む)

多段増幅器

【課題】低周波数帯域の利得を効果的に抑圧して発振の発生を抑制すると共に、回路の高密度実装を可能とする多段増幅器を提供する。

【解決手段】FET1,2に、ゲートバイアス電圧を印加する入力整合回路3,5と、FET1,2に、ドレインバイアス電圧を印加する出力整合回路4,6と、出力整合回路4と入力整合回路5との間に直列接続されたコンデンサ15,16、および、一端がコンデンサ15,16間の接続点に接続され他端が接地された誘導性の線路17を含み構成されたハイパスフィルタ18と、を備え、コンデンサ15,16のキャパシタンス値および線路17のインダクタンス値は、増幅素子の動作周波数よりも低い周波数帯域において、出力整合回路6と出力整合回路4とハイパスフィルタ18とを介して形成されるドレインバイアスループ11の損失が、FET2の利得よりも大きくなるように設定する。

(もっと読む)

41 - 60 / 603

[ Back to top ]