Fターム[5J500AK47]の内容

Fターム[5J500AK47]に分類される特許

141 - 160 / 565

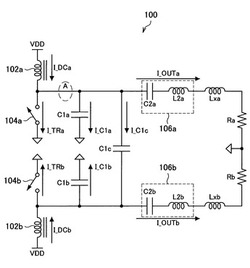

増幅器および通信装置。

【課題】ピーク電流を削減することで、スイッチング素子にかかるストレスを軽減させて、増幅器としての信頼性を向上させることが可能な増幅器を提供すること。

【解決手段】所定の電流を出力する電流源と接地電位との間に接続される第1スイッチング素子と、第1スイッチング素子と並列に接続され、電流源と接地電位との間に接続される第1キャパシタと、を含む第1増幅回路と、所定の電流を出力する電流源と接地電位との間に接続される第2スイッチング素子と、第2スイッチング素子と並列に接続され、電流源と接地電位との間に接続される第2キャパシタと、を含む第2増幅回路と、第1増幅回路と第2増幅回路との間に設けられる第3キャパシタと、を備え、第1スイッチング素子は、第2スイッチング素子がオフの場合にオンとなり、第2スイッチング素子がオンの場合にオフとなる、増幅器が提供される。

(もっと読む)

増幅器および通信装置。

【課題】高効率性を損なうことなく、従来のE級増幅器で用いられていたチョークコイルを用いないことで小型化することが可能な増幅器を提供すること。

【解決手段】電源からの供給電流に含まれる基本波成分および2次高調波成分を遮断するフィルタ回路と、フィルタ回路と接地電位との間に接続されるスイッチング素子と、スイッチング素子と並列に接続され、フィルタ回路と接地電位との間に接続されるキャパシタと、を備える、増幅器が提供される。

(もっと読む)

容量性負荷の充放電回路

【課題】ブートストラップ型の容量性負荷充放電回路における動作を安定させること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、基準電位設定部と、電荷放出部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。基準電位設定部は、アナログ信号の電位が閾値よりも高い場合に、蓄電素子が有する低電位側端子の電位を、第1基準電位から第1基準電位よりも高い第2基準電位に設定する。電荷放出部は、容量性負荷から充放電部を通じて流れ出た電荷を、低電位側端子を介さずに放出する。

(もっと読む)

増幅器の線形性を改善するための技術

【解決手段】増幅器の線形性を改善するための技術。補助増幅器(M5)は、主分岐(M2)と並列に設けられる。補助増幅器(M5)は主分岐(M2)におけるノード(X1)をサンプリングする。補助増幅器(M5)は、主分岐によって生成される電流と組み合わされる時、線形特性が改善された出力電流を生成するため歪み成分を打ち消す電流を生成する。ネットワーク(310)は、ノード(X1)と補助増幅器(M5)とを結合し、インダクタに結合されるキャパシタを含み得る。増幅器の線形性を改善する技術。補助増幅器(M5)は、主分岐(M2)と並列に設けられる。補助増幅器(M5)は、主分岐(M2)におけるノード(X1)をサンプリングする。補助増幅器(M5)は、主分岐(M2)によって生成される電流と組み合わされる時、線形特性が改善された出力電流を生成するため歪み成分を打ち消す電流を生成する。 (もっと読む)

改良された指数関数電流発生器と方法

【課題】ImがIbleedより小さいときでさえ、比率が制御信号に指数関数的に関連する電流対を発生させる。

【解決手段】対の比率が制御信号に指数関数的に関係する電流対Ip、Imを発生する装置および方法であって、ここにIpまたはImのいずれかは最小値より大きいかまたは最大値より小さい。装置はImまたはIpの値を感知するために使用される帰還修正回路を含む。感知されたImまたはIpの値が最小値より小さいかまたは最大値より大きいとき、修正回路はブースト電流Iboostを供給する。Iboostは好ましくは所望値およびIpまたはImの差に比例するよう維持される。

(もっと読む)

オーディオ信号処理回路およびチャージポンプ回路の制御方法

【課題】メインアンプの電源電圧を、オーディオ信号の振幅に関わらず固定すると、電力が無駄に消費される。

【解決手段】チャージポンプ回路2は、正の電源電圧Vddを反転し、負の電源電圧Vssを生成する。メインアンプ4は、正の電源電圧Vddと負の電源電圧Vssを電源電圧として受け、入力されたオーディオ信号S1を増幅する。レベル検出回路7は、メインアンプ4へ入力されるオーディオ信号S1またはメインアンプ4により増幅されたオーディオ信号Voutの少なくとも一方のレベルを検出する。チャージポンプ回路2は、負の電源電圧Vssの電圧値を、レベル検出回路7によって検出されたオーディオ信号のレベルに応じて変化させる。

(もっと読む)

フォロワ回路

【課題】レベルシフト量がソースフォロワ回路に対して反対の符号となるようなレベルシフタを可能にするフォロワ回路を提供すること。

【解決手段】MOSトランジスタ1,11はPMOSトランジスタで、MOSトランジスタ2はNMOSトランジスタである。MOSトランジスタ1のソース1Sは、正の電源端子8に接続され、ゲート1Gは、第1のバイアス電圧が供給される第1のバイアス端子6に接続され、ドレイン1Dは、入力端子4に接続されているとともに、MOSトランジスタ11のソース11Sに接続される。MOSトランジスタ11のゲート11Gとドレイン11Dは、共通接続されているとともに、MOSトランジスタ2のドレイン2D及び出力端子5に接続される。MOSトランジスタ2のソース2Sは、負の電源端子9に接続され、ゲート2Gは、第2のバイアス電圧が供給される第2のバイアス端子7に接続される。

(もっと読む)

FETバイアス回路

【課題】温度変動における複数の高周波増幅器間のバイアス変動特性のばらつきを低減することのできるFETバイアス回路を提供する。

【解決手段】高周波増幅器1は、第1段増幅器10と、第1段増幅器10の後段に接続される第2段増幅器20と、第2段増幅器20の後段に並列接続される第3段A増幅器31及び第3段B増幅器41(A,Bを第3段増幅器30と呼ぶ)と、第3段増幅器30を制御するA/D変換器13,CPU12,D/A変換器11と、を有している。ここで、第3段A増幅器31には、FET32と、ドレイン電流Vdsdcを測定するための抵抗Rdと、温度センサ34と、ゲート電圧Vgsを制御するための演算増幅器33と、コンデンサC1,C2と、を有している。

(もっと読む)

ドライバ回路及びドライバIC

【課題】クロスポイントが50%からずれた電気波形を出力する際も、良好な出力波形を維持することができるドライバ回路を得る。

【解決手段】初段増幅段A1、2段目増幅段A2及び最終増幅段A3の3段の差動増幅段が直列に接続されている。初段増幅段A1及び2段目増幅段A2に、クロスポイント調整回路CP1,CP2がそれぞれ接続されている。クロスポイント調整回路CP1は、初段増幅段A1の正相と逆相のDCレベルの少なくとも一方を制御して、初段増幅段A1の出力信号のクロスポイントを調整する。また、クロスポイント調整回路CP2は、2段目増幅段A2の正相と逆相のDCレベルの少なくとも一方を制御して、2段目増幅段A2の出力信号のクロスポイントを調整する。

(もっと読む)

温度補償回路及び電流源回路

【課題】 簡単な構成で電流源回路を温度補償することができる温度補償回路及び電流源回路を提供する。

【解決手段】 温度補償回路1は、第1トランジスタM1と同チャネル型のMOSFETにて構成した第2トランジスタM2を設けて構成してあり、ゲート電圧生成手段たる第2トランジスタM2のソースは前記第1トランジスタM1のゲートに接続してある。また、温度補償回路1にはスイッチング素子として動作させる第3トランジスタM3が設けてあり、第3トランジスタM3のドレインと第2トランジスタM2のソースとを直列接続してある。

(もっと読む)

差動増幅回路、高速シリアルインターフェース回路、集積回路装置及び電子機器

【課題】出力信号のデューティ比のばらつきを低減できる差動増幅回路、高速シリアルインターフェース回路、集積回路装置及び電子機器を提供すること。

【解決手段】差動増幅回路は差動入力信号を構成する第1、第2の入力信号が入力され、第1、第2の入力信号に対応する第1、第2の差動出力信号を出力する差動増幅部10と、第1、第2の差動出力信号に応じてシングルエンドの出力信号を出力する出力部20を含む。出力部20は、高電位側電源と出力ノードとの間に設けられた第1のトランスミッションゲート21と、低電位側電源と出力ノードとの間に設けられた第2のトランスミッションゲート22を含む。第1、第2の差動出力信号に応じて、第1、第2のトランスミッションゲート21、22がオン・オフされる。

(もっと読む)

コンデンサ型電気音響変換器を駆動する方法及び電子装置

【課題】コンデンサ型電気音響変換器を駆動する方法及び電子装置を提供し、コンデンサ型電気音響変換器の低電力消費の物理的特性を利用して電力を節約する。

【解決手段】電子装置は、コンデンサ型電気音響変換器と、コンデンサ型電気音響変換器に結合され、高電圧増幅器を含み、入力音声信号を受信して出力音声信号に変換し、これでコンデンサ型電気音響変換器を駆動する音声ドライバーとを含む。入力音声信号の電圧の絶対値は出力音声信号の電圧の絶対値より小さい。コンデンサ型電気音響変換器はエレクトレットスピーカーまたはエレクトレットイヤホンである。コンデンサ型電気音響変換器はエレクトレット振動板と穴開き電極板を含む。

(もっと読む)

差動出力バッファ

【課題】 広範囲な電源電圧仕様に対して、安定した出力振幅およびその出力振幅の中心電圧を出力することができる差動出力バッファを提供する。

【解決手段】 ドレインが電源電圧VDDに接続されるとともにゲートに出力差動信号OUTP,OUTNの出力コモンモード(VOC)を規定する第1の基準信号VREF1が入力されるデプレッション型NMOSトランジスタ11と、ソース双方がデプレッション型NMOSトランジスタ11のソースに接続されるとともに各ゲートに各差動信号INN,INPが入力されるPMOSトランジスタ12,14と、各ゲートおよび各ドレインが各PMOSトランジスタ12,14の各ゲートおよび各ドレインにそれぞれ接続されるとともに各ゲートに各差動信号INN,INPが入力されるNMOSトランジスタ13,15と、NMOSトランジスタ13,15双方のドレインとグランドGNDとの間に接続されたNMOSトランジスタ16とを備えた。

(もっと読む)

電流供給回路及び電流供給回路を備えた半導体集積回路

【課題】電流供給回路の余分な消費電流を削減し、消費電力の低下改善を図る。

【解決手段】高圧側電源と低圧側電源との間に、一端及び他端が接続される電流供給用の出力トランジスタと、互いに並列に接続され、前記出力トランジスタの制御端子に電流を流す、複数の定電流源と、前記各定電流源に接続され、前記各定電流源が流す電流をオンオフする、スイッチと、前記出力トランジスタの前記他端に接続された出力端子と、前記出力トランジスタの前記他端と、前記低圧側電源と、の間に挿入接続され、前記出力端子に流れる電流値を決める駆動回路と、前記出力トランジスタに流れる電流値をモニタする電流モニタ回路と、前記電流モニタ回路でモニタした電流値に基づき、前記スイッチのうちの任意数のものをオンする、制御回路と、を備える。

(もっと読む)

BTL増幅器保護回路

【課題】BTL増幅器にて使用する電源電圧が低い場合、地絡・天絡時の出力トランジスタの電流も少なくなり、保護回路が起動しにくくなり、ASO破壊が生じやすい。

【解決手段】モニタ電流生成回路32−1は、出力トランジスタQ1の導通電流に応じたモニタ電流IMO1を生成する。保護動作部28はモニタ電流を閾値と比較して地絡を判定する。バイアス電流生成回路34−1は、電源電圧VCCが閾値以上の状態では、バイアス電流IMB1を0とし、閾値未満の状態では非零とする。IMO1にIMB1を合成した修正モニタ電流IM1を異常判定の基準値との比較対象とする。VCCが閾値未満の状態では、IM1は上側にバイアスされ、異常状態での実質的な判定基準値が低下する。これにより、VCCの高低によらず、異常状態でのQ1の電流増加を検知して保護動作を実行できる。

(もっと読む)

音声出力装置

【課題】音声出力装置においてボツ音を低減をシンプルな構成で実現する。

【解決手段】音声出力装置10は、ハイサイドトランジスタ22及びローサイドトランジスタ24からなる増幅回路20と並列に、ボツ音対策用のハイサイドトランジスタ62及びローサイドトランジスタ64からなるスイッチング制御回路60を設けた。そして、出力コンデンサ40の容量C20との時定数が、負荷であるスピーカSPの再生帯域低域限界周波数、あるいは可聴帯域の下限である概ね20Hz以下となるノイズ低減抵抗70を介して、増幅回路20の出力に接続している。そして、増幅回路20を動作状態にする前に徐々に入力電圧の平均値に出力コンデンサ40を充電する。これにより、ボツ音の発生が回避される。

(もっと読む)

制御電流生成回路

【解決手段】電流制御されたバイアス電流のための電流である制御電流(Icontrol)が、抵抗(a、b)によって形成される分圧器の両端の電圧降下により生成される。電圧供給電源の変動に依存する補正電流(Isink)を吸い出すことによって制御電流を補正し、電圧供給電源(Vsupply)の変動に影響されない制御電流を生成する。当該制御電流の補正は、少なくとも1つの基準トランジスタ(c、d)、及び電流吸い込み用トランジスタ(e)の組み合わせによって達成される。 (もっと読む)

利得調整回路およびD級電力増幅器

【課題】利得調整および広範囲な電圧源にも安定して適用することができる利得調整回路およびD級電力増幅回路を提供する。

【課題を解決するための手段】

利得調整回路100はアナログ入力信号が入力される信号入力端子102、アナログ信号を増幅し電圧源E1が供給される演算増幅器108、演算増幅器108の反転入力端子108aと出力端子108cとの間に接続される第1のT型抵抗回路T123を備える。信号入力端子102と反転入力端子108aとの間に利得調整するための第1の可変抵抗RV1を接続する。演算増幅器108の非反転入力端子108bにはバイアス電圧供給回路130から直流バイアス電圧が供給される。バイアス電圧供給回路130は第1の電圧生成回路132および第2のバイアス電圧生成回路138を備える。第1のバイアス電圧生成回路132は第2の電圧源E2および第2のT型抵抗回路T123aを備え、第2のバイアス電圧生成回路138は第3の電圧源E3および第2の可変抵抗RV2を備える。

(もっと読む)

可変バイアス回路

【課題】入力電圧の変化に対するバイアス電圧のダイナミックレンジ及びその傾きを可変とした可変バイアス回路を提供する。

【解決手段】レイルツーレイルアンプを構成する第1のアンプ4及び第2のアンプ5を設ける。PMOSトランジスタMP6とPMOSトランジスタMP7とでカレントミラー回路を構成する。PMOSトランジスタMP6のドレインとVSS電源線2との間に、基本電流生成回路12と、選択により基本電流生成回路12に並列接続される選択電流生成回路14〜17とを接続する。基本電流生成回路12に並列接続させる選択電流生成回路の数を制御することにより、NMOSトランジスタMP6に流れる電流I3及びPMOSトランジスタMP7に流れる電流I4のダイナミックレンジ及びその傾きを変化させる。

(もっと読む)

バイアス電流供給回路

【課題】配線抵抗の影響が小さく、ノイズの混入の影響が小さく、簡便に配線でき、LSIに好適なバイアス電流供給回路を提供する。

【解決手段】ドレインが電流源に接続され、ゲートが所定の電圧に接続される第1のNチャネルトランジスタと、ドレインが共通電位に接続され、ソースが前記第1のNチャネルトランジスタのソースに接続され、ゲートが共通電位に接続される第1のPチャネルトランジスタと、ドレインがバイアス電流を供給し、ゲートが前記第1のNチャネルトランジスタのゲートに接続される第2のNチャネルトランジスタと、ドレインが前記第1のPチャネルトランジスタのドレインに接続され、ソースが前記第2のNチャネルトランジスタのソースに接続され、ゲートが前記第1のPチャネルトランジスタのゲートに接続される第2のPチャネルトランジスタとを備える。

(もっと読む)

141 - 160 / 565

[ Back to top ]