Fターム[5J500DN24]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | エミッタ(ソース)回路構成 (671) | 定電流源を具備するもの (401) | 定電流源がカレントミラー構成 (85)

Fターム[5J500DN24]に分類される特許

21 - 40 / 85

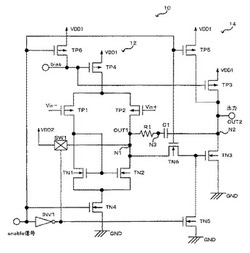

オペアンプ回路及びオペアンプ回路の駆動方法

【課題】CMOSオペアンプ回路において、パワーダウン状態の解除後に定常状態に安定するまでの動作速度を高速化することができるオペアンプ回路及びオペアンプ回路の制御方法を提供する。

【解決手段】パワーダウン時はSW1により電圧VDD2をノードN1に印加し、出力端OUT1から電圧VDD2が出力されるため、位相補償用コンデンサC1の両電極に電位差が生じ、電荷が蓄積され、定常状態に切り替わると蓄積されていた電荷が放電され、Nチャネル型MOSトランジスタTN3のゲートがONするため、瞬時に出力端OUT2の出力値が引き下げられた後、安定状態に落ち着く。

(もっと読む)

検出回路

【課題】プロセス変動等によるサンプルごとのしきい値のばらつきを低減させることができ、高速動作を行うことができる、入力検出及び/又は切断検出を行う検出回路を得る。

【解決手段】1対のシリアルデータ信号が対応する入力端に入力される差動増幅回路で構成された第1検出用レシーバ2と、1対のシリアルデータ信号が対応する入力端に入力される差動増幅回路で構成された第2検出用レシーバ3と、対応する入力端に入力された各基準電圧Vrp及びVrmにそれぞれオフセットを加えて出力する差動増幅回路で構成されたリファレンスレシーバ7の各差動増幅回路は、前記各シリアルデータ信号が対応してゲートに入力されるMOSトランジスタからなる1対の入力トランジスタを有し、該各入力トランジスタのサブストレートゲートに電圧差を設けてそれぞれオフセットが設けられるようにした。

(もっと読む)

コンパレータ

【課題】低電源電圧駆動、低消費電流、高速動作を実現することが可能なコンパレータを提供することを目的とする。

【解決手段】コンパレータの有するカレントミラー回路を、直列に接続された2つのトランジスタから構成される2組の回路により構成し、直列に接続された2つのトランジスタのうち電源側又は接地側に接続されたトランジスタのゲート長を、直列に接続された2つのトランジスタのうち他方のトランジスタのゲート長よりも長くする。

(もっと読む)

差動増幅回路

【課題】差動増幅回路のオフセット電圧を小さくする。

【解決手段】本発明の差動増幅回路は、差動入力信号を受け取るNMOSトランジスタ対を備えるN型入力段2と、N型入力段2に接続された出力段4と、前記差動入力信号を受け取るPMOSトランジスタ対を備えるP型入力段3と、P型入力段3に接続された出力段5と、出力端子OUTとを備えている。出力段5は、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、PMOSトランジスタをNMOSトランジスタに置き換え、接地端子を電源端子に置き換え、電源端子を接地端子に置き換えた構成を有している。出力端子OUTは、出力段4の出力と出力段5の出力に共通に接続されている。

(もっと読む)

演算増幅器及び積分回路

【課題】高速にリセット動作を行うことができるとともに、低消費電力である演算増幅器を提供すること。

【解決手段】本発明に係る演算増幅器130は、基準電位Vbiasに対して入力信号の差動増幅を行う差動増幅回路132と、差動増幅回路132により増幅された信号を出力する出力回路133と、差動増幅回路132の出力と出力回路133の出力の間に接続され、出力回路133から出力される信号の位相を補償する位相補償容量106と、位相補償容量106と並列に接続されたダイオード112とを備えるものである。

(もっと読む)

デジタル−アナログ変換器における電流セル回路

【課題】電流セル回路から検出される電圧を電流に変換し、出力電圧の範囲を広げることで、出力電圧が高くなるにつれて減少する電流量を補償し、一定の出力電圧で電流変化量を最小化できるデジタル−アナログ変換器における電流セル回路を提供する。

【解決手段】電源電圧端に連結されて一定の大きさの電流を生成する電流源と、前記電流源から提供される電流を第1出力端に伝達する第1電流スイッチと、前記第1出力端の出力電圧を検出し、検出された電圧から減少する電流量を生成する第1電流生成部と、前記第1電流生成部から生成された前記電流量を前記第1電流スイッチに供給する第1電流供給部とを含んでデジタル−アナログ変換器における電流セル回路を構成する。

(もっと読む)

半導体集積回路

【課題】回路を複雑化させずに、カレントミラー回路のミラー精度を向上させることが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、カレントミラー回路に流す基準電流を生成する基準電流生成回路1と、ドレイン−ソース間に基準電流を流すミラー元の第1のトランジスタM1と、M1とともにカレントミラー回路を構成するミラー先の第2のトランジスタM2と、M2を電流源として用いる差動増幅器2と、M1のドレイン電圧とM2のドレイン電圧とを一致させるミラーずれ調整回路3とを備えている。M1のドレイン側に第5のトランジスタM5からなるミラーずれ調整回路3を接続し、M5のゲート電圧を、M2のドレイン側に接続される第3および第4のトランジスタM3、M4の両ゲート電圧の平均値と一致させるため、M1のドレイン電圧とM2のドレイン電圧とのずれがなくなる。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能な増幅回路を提供する。

【解決手段】本発明による増幅回路3bは、差動入力部81A及び81Bと、該差動入力部81A及び81Bのうちのいずれか一方を選択するスイッチ79A及び79Bと、を備え、該スイッチ79A及び79Bにより選択された差動入力部を用いた増幅処理を行うオペアンプ70bと、オペアンプ70bの出力端と差動入力部81Aの入力端との間に設けられ、所定抵抗値の抵抗を有する第1の帰還回路と、オペアンプ70bの出力端と差動入力部81Bの入力端との間に設けられ、上記所定抵抗値とは異なる抵抗値の抵抗を有する第2の帰還回路と、を備えることを特徴とする。差動入力部の選択により電圧増幅度を切り替え可能であるので、帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能となっている。

(もっと読む)

コンパレータ

【課題】 電源電圧VDDが低い状態においても、正確に入力電圧の比較を行うことができるコンパレータを提供する。

【解決手段】 差動増幅回路10の後段のソース接地増幅回路20Aにおいて、差動増幅回路10の出力信号V2がゲートに与えられるNチャネル電界効果トランジスタ21と、その定電流負荷としてのPチャネル電界効果トランジスタ22との間にはPチャネル電界効果トランジスタ23が介挿されている。Pチャネル電界効果トランジスタ23のゲートには、電圧B=VDD/2が与えられる。Pチャネル電界効果トランジスタ23は、電源電圧VDDが低い状態において、差動増幅回路10に対する入力電圧VrefおよびVinが一致したときに、Pチャネル電界効果トランジスタ22の動作点を差動増幅回路10のPチャネル電界効果トランジスタ13の動作点に近づける。

(もっと読む)

誤差増幅回路およびスイッチング電源回路

【課題】簡単な構成で出力電圧の下限を制限することが可能な誤差増幅回路を提供する。

【解決手段】バイアス段110から差動段120のPMOSFET M3(124)、PMOSFET M4(125)のソースに定電流が供給される。PMOSFET M3(124)及びPMOSFET M4(125)のドレインに接続されたNMOSFET M5A(128)及びNMOSFET M6A(129)は第1のカレントミラー回路を、またNMOSFET M5A(128)及びNMOSFET M6A(129)のソースに接続されたNMOSFET M5(126)及びNMOSFET M6(127)は第2のカレントミラー回路を構成する。ダイオード接続されたNMOSFET M6(127)及びこれにカスケード接続するNMOSFET M6A(129)は能動負荷を構成し、NMOSFET M6A(129)のドレインから出力端123に信号を出力する。

(もっと読む)

半導体装置および半導体装置の設計方法

【課題】設計期間の短縮を実現可能な半導体装置の設計方法を提供する。

【解決手段】例えば、2ステージCMOSオペアンプ回路の電気的特性を算出する回路シミュレータ部SIMと、オペアンプ回路内の回路定数を変更しながらSIMを動作させ、予め定めた設計仕様SPECを満足する回路定数を自動探索する最適化制御部OPTを設ける。OPTでは、予め定めた複数のパラメータの関数となる制約式に基づいて、各パラメータ値を逐次変更しながら各トランジスタおよび位相補償容量の回路定数を算出し、それをSIMに反映させる。位相補償容量の制約式は、オペアンプ回路の1ステージ目および2ステージ目の出力容量と、予め定めた位相余裕と、パラメータkb’の関数で規定され、この出力容量は各トランジスタの回路定数で定められる。このような制約式を用いることで、回路定数の探索範囲を狭めることが可能となる。

(もっと読む)

バイアス電流発生回路およびそれを用いた差動回路

【課題】半導体プロセスに起因する遅延時間および消費電力のばらつきを小さくすることができるバイアス電流発生回路およびそれを用いた差動回路を提供する。

【解決手段】バイアス電流発生回路は、半導体プロセスによって出力電流がばらつく第1の電流発生回路14と第2の抵抗21a〜21n、第3の抵抗22を直列接続し、半導体プロセスによって出力電流がばらつかない第2の電流発生回路16と第1の抵抗20a〜20mを直列接続して、第1の電流発生回路と第3の抵抗の接続点の電圧と、第1の抵抗と第2の電流発生回路の接続点の電圧を増幅器に入力して、この増幅器の出力によって第2の抵抗と第3の抵抗の接続点から電流を引き出すと共に、この電流に関連する電流を出力する。また、このバイアス電流発生回路の出力電流で差動回路の出力段の駆動電流を決める。

(もっと読む)

演算増幅回路

【課題】広い出力電圧範囲において、一定のオフセットを実現する演算増幅回路を提供する。

【解決手段】従来の演算増幅回路30に対し、オフセット一定化回路200を設ける。オフセット一定化回路は、演算増幅回路の入力段が備えるPMOS差動電流源MP1のオン、オフを切換える第1のスイッチと、入力段が備えるNMOS差動電流源MN1のオン、オフを切換える第2のスイッチと、第1、2スイッチを切換えるタイミングを決定する電圧生成部23と、第1、2スイッチを制御する制御信号を出力する電圧比較器21を備え、入力電圧に応じPMOS差動電流源MP1とNMOS差動電流源MN1の電流を制御する。

(もっと読む)

ミクサ回路

【課題】入力される信号が大信号でも信号入力用バイポーラトランジスタのコレクタ電流の降下を抑制し高飽和特性を実現するミクサ回路を提供する。

【解決手段】中間周波又は高周波の差動信号を入力する入力用トランジスタ対4a,4b、局部発振波の差動信号を用い入力用トランジスタ対により入力された中間周波又は高周波の差動信号を高周波又は中間周波の差動信号に変換する信号変換回路5a〜5d、入力用トランジスタ対のエミッタ端子に接続されたトランジスタ7、トランジスタ7とカレントミラーを構成するバイアス用トランジスタ8、信号変換回路の出力差動信号又は入力差動信号を入力電力としてモニタする電力モニタ用回路11、電力モニタ用回路の出力電流を基準電流とするP型カレントミラー回路10a,10bを備え、P型カレントミラー回路の出力電流がバイアス用バイポーラトランジスタの基準電流であるミクサ回路。

(もっと読む)

差動増幅器

【課題】大振幅入力に対応するため、入力差動対を高耐圧素子を用いて構成する必要があった。

【解決手段】カスコードカレントミラー回路20は、入力差動対10に能動負荷として接続される。テール電流源30は、入力差動対10にテール電流Itを供給する。定電流源40は、入力差動対10と並列に接続され、テール電流源30に定電流Icを供給する。定電流源40により供給される定電流IcはトランジスタM7がカットオフしない値に設定される。

(もっと読む)

バイアシング入力ステージ及びそれを含む増幅器

【課題】適応的バイアシング入力ステージとそれを含む増幅器を提供する。

【解決手段】本発明による適応的入力ステージは、ゲートに差動入力が供給される一対の差動結合増幅FET及び一対の差動検出FETを含む。また、静的電流源は、既定のノードで増幅及び検出FETのソースに結合される。さらに、電流ミラーは、ループメカニズム(Loop Mechnisms)を形成するために、検出FETに結合されて差動入力の差がゼロ(zero)ではない時、既定のモードを通じる電流を増加させる。

(もっと読む)

半導体装置

【課題】電圧依存性のあるMOS容量を、例えばオペアンプの位相補償用回路素子として使用する際に、オペアンプの入力あるいは出力電圧が如何なる電圧領域でも、MOS容量値が減少して位相余裕が減少することがない構成を実現する。

【解決手段】半導体基板上に形成されたゲート電極と拡散層間に絶縁膜を有する構造のMOS容量を用いた位相補償用回路6を備え、位相補償用回路は第1および第2のMOS容量14、15により構成される。第1のMOS容量のゲート電極端子と、第2のMOS容量の拡散層側端子(ゲート電極端子とは反対の端子)が等価的に接続され、第1のMOS容量の拡散層側端子と第2のMOS容量のゲート電極端子の間に、電流が流れることにより電位差を発生する電位差発生素子16が接続される。

(もっと読む)

カスコード増幅器

【課題】 温度変動やプロセスのバラツキによる動作点及び特性の変動を抑えることが可能なカスコード増幅器を実現する。

【解決手段】 カスコード増幅器において、前段増幅回路の差動出力を増幅して出力するカスコード増幅回路と、バイアス電流に基づきカスコード増幅回路にバイアス電圧を供給すると共にバイアス電流及び前段増幅回路のバイアス電流を加算してカスコード電圧を決定しカスコード増幅回路のカスコードトランジスタのベースに印加するバイアス回路とを設ける。

(もっと読む)

レールトゥレール型増幅回路及び半導体装置

【課題】レールトゥレール増幅回路の消費電力の低下と小面積化の実現。

【解決手段】DACからのアナログ信号を増幅するレールトゥレール型増幅回路100であり、nチャネル型トランジスタ対を備える差動入力Ninと、pチャネル型トランジスタ対を備える差動入力Pinを備え、差動入力Pinと高電圧側の電源Vccとの間に電流源Csp1が設けられ、電流源Csp1と差動入力Pinとの間に、DACへの入力デジタルデータの所定ビット位置のデータに応じて、差動入力Pinへの電流供給を制御するPin用電流制御部Swp1を備える。低電圧側の電源Vssと差動入力Ninとの間に、電流源Csn1が設けられ、電流源Csn1と差動入力Ninとの間に、DACへの入力デジタルデータの所定ビット位置のデータに応じて、差動入力Ninへの電流供給を制御するNin用電流制御部Swn1を備える。

(もっと読む)

全差動増幅装置

【課題】差動増幅器において、電源立ち上げ時や、モード切替時などの過渡的状態に、出力コモン電圧を所定の電圧に安定に収束させることを可能にする。

【解決手段】差動増幅器3の出力部に補助電流を流すMOSトランジスタM6、M7を設け、かつ補助電流に対応した補正電流をコモンモードフィードバック用比較器7に流すMOSトランジスタM12を設けることにより、差動増幅器3の入力が初期においてダイナミックレンジ外になっても出力コモン電圧を所定の電圧に制御する制御ループを正しくスタートアップさせ、出力コモン電圧を所望の電圧で安定させる。

(もっと読む)

21 - 40 / 85

[ Back to top ]