Fターム[5K029CC01]の内容

直流方式デジタル伝送 (8,390) | 伝送媒体 (648) | メタリック有線伝送路 (541)

Fターム[5K029CC01]の下位に属するFターム

同軸ケーブル (1)

Fターム[5K029CC01]に分類される特許

121 - 140 / 540

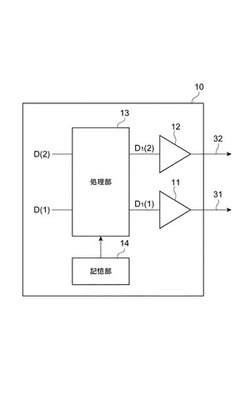

送信装置および送受信システム

【課題】受信装置において受信エラーが生じる頻度を更に低減することができる送信装置および送受信システムを提供する。

【解決手段】送信装置10は、第1出力部11、第2出力部12、処理部13および記憶部14を備える。処理部13は、送出すべき第1データD(1)および第2データD(2)を受け取るとともに、記憶部14により記憶されている信号線路31,32の線路間干渉特性をも受け取る。処理部13は、信号線路31,32の線路間干渉特性に基づいて、第1データD(1)の値を補正したデータD1(2)を求めるとともに、第2データD(2)の値を補正したデータD1(1)を求める。第1出力部11は、処理部13により求められたデータD1(1)を第1信号線路31へ送出する。第2出力部12は、処理部13により求められたデータD1(2)を第2信号線路32へ送出する。

(もっと読む)

ドライバ回路

【課題】差動入力信号の振幅中心電圧が高い場合でも、差動出力信号の振幅変動やジッタを抑制することができるドライバ回路を提供することである。

【解決手段】本発明にかかるドライバ回路は、トランジスタM1と、トランジスタM1のソースと電源端子との間に接続された負荷素子R1と、トランジスタM1とカレントミラー回路を構成するトランジスタM2と、入力された差動入力信号に応じた差動出力信号を出力すると共に、トランジスタM2によりソースにバイアス電流が供給される一対のトランジスタを備える差動対と、トランジスタM2のソースと電源端子との間に接続された負荷素子R2と、非反転入力端子がトランジスタM1のソースと接続され、反転入力端子がトランジスタM2のソースと接続され、出力が差動対を構成する一対のトランジスタのバックゲートに接続されたオペアンプAMP1と、を有する。

(もっと読む)

第1のステーションと第2のステーションとの間の通信を確立する方法および装置

本発明は、第1のステーションと第2のステーションとの間にコミュニケーションを確立する方法および装置に関する。ここで第1のステーションと第2のステーションとの間の第1の部分接続上で識別子が伝送される。この識別子は、第1のステーションと第2のステーションを、コミュニケーションのコミュニケーションパートナーとして同定する。この識別子を得た後、コミュニケーション接続を介して、第1のステーションと第2のステーションとの間でコミュニケーションが開始される。ここで第1の部分接続を介した識別子の伝送とコミュニケーション接続は、物理的に異なる接続に基づく。本発明は、電気車両の充電過程または放電過程時に使用可能である。これは例えば病院の領域における独立したシステムである。または個人搬送用の車両である。本発明の利点は、第1のステーションと第2のステーションとの間の確実かつ低コストなコミュニケーションが保証される、ということである。  (もっと読む)

(もっと読む)

RS−232C信号遠隔伝送システム及び伝送中継装置

【課題】遠隔位置にあるRS-232C機器間で中継機器を介在させてRS-232C信号を伝送するシステムであって、一方側の回線セグメントに何らかの通信障害が生た場合、他方側で回線セグメントの信号状態の情報を取得できる遠隔伝送システムを提供する。

【解決手段】監視側の伝送中継装置は、RS-232C信号とRS-422信号を相互に変換する信号変換部と、監視モード信号を伝送する監視状態通知部と、下位側機器側のセグメントの信号状態を表示する信号状態表示部とを備えており、被監視側の伝送中継装置は、信号変換部と、監視モード信号を検知した時に下位側機器側のセグメントの信号状態の情報を監視側の伝送中継装置へ送る信号情報通知部とを備えており、下位側機器側のセグメントの通信障害時に信号状態表示部で下位側機器側のセグメントの信号状態の情報が得られるようにしたRS-232C信号遠隔伝送システム。

(もっと読む)

信号入力回路及びそれを含む半導体装置

【課題】差動信号と単一信号をともに受信できる信号入力回路を提供する。

【解決手段】信号入力回路は、第1入力信号を受信して出力ノードに出力信号を出力する入力部と、出力ノードと連結され、第2入力信号に応じて出力ノードをディスチャージする第1補償回路と、出力ノードと連結され、第2入力信号に応じて出力ノードに電流を供給する第2補償回路と、少なくとも1つの動作モード選択信号に応じて入力部、第1補償回路及び第2補償回路を動作状態に転換するためのイネーブル回路とを含む。

(もっと読む)

マンチェスタ符号を用いた調歩同期通信に基づく受信器及び半導体装置

【課題】マンチェスタ符号を用いた調歩同期通信において物理層の誤り検出手段を提供し、クロックが安定しない環境(システム)での使用が可能となる通信方法を提案する。

【解決手段】調歩同期通信の受信データの決定を1ビット長単位だけでなく、2ビット長単位でも行う。第1の2ビットデータカウント6−1と第2の2ビットデータカウント6−2をタイムスロット1ビット分ずらして動作させ、交互にデータの確定を行う。この第1の2ビットデータカウント6−1と第2の2ビットデータカウント6−2の出力するタイミング信号によって出力されたデータを通常の1ビット長単位で出力されるデータと対比することで、データの誤検出を行う。

(もっと読む)

クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法

【課題】クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法を提供する。

【解決手段】クロック情報及びデータ情報を含む差動信号対を受信するにおいて、差動信号対の共通電圧レベルの変化を利用してクロック信号及びデータを復元できる、クロック情報及びデータ情報を含む信号を受信する受信器及びクロック埋め込みインターフェース方法である。

(もっと読む)

高分解能出力ドライバ

それぞれ、量子化ステップより実質的に大きい、公称インピーダンスを有し、量子化ステップより実質的に小さい、インピーダンスステップだけ、相互にインクリメント的に異なる、比較的に少数のサブドライバブランチまたはスライスを有する、高分解能出力ドライバ。一実装では、かかる「差動」または「非一様」サブドライバスライスは、n choose k等化器の個別の要素を実装し、各かかる差動サブドライバスライスは、一様要素インピーダンス較正DACによって実装される。別の実装では、一様スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装され、さらに別の実装では、差動スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装される。付加的セットの実装の実装では、等化およびインピーダンス較正機能は、階層的実装のネスト化された「DAC内のDAC」配設においてではなく、個別の並列セットのドライバブランチにおいて、双方向に実装される。かかる双方向配設を通して、等化器および較正器量子化の倍増が回避され、それによって、規定の範囲および分解能を満たすために要求されるサブドライバスライスの総数を減少させる。 (もっと読む)

データ送信回路及びデータ通信装置

【課題】SYNCパターンを送信することなくDCバランスを調整する期間を不要にすることによりアイドル状態から通信を開始するまでの時間を短縮し、さらには、消費電力を低減するデータ送信回路及びデータ通信装置を提供する。

【解決手段】本発明の一実施の形態に係るデータ送信回路は、ACカップリングされた単数又は複数の線路を有する伝送路を介してデータを送信するデータ送信部を備えるデータ送信回路であって、前記データ送信部は、データ送信の際には前記データに対応する第1の電位又は前記第1の電位とは異なる第2の電位を順次設定することにより前記伝送路を介してデータを送信し、前記データ送信からアイドル状態に移行した際には前記第1の電位及び第2の電位の中間電位に設定する。

(もっと読む)

信号伝送システム

【課題】安定した映像信号を送信及び再生することができる信号伝送システムを提供する。

【解決手段】信号伝送システムは、水平同期信号を差動信号に変換し、第1コンソール信号をコモンモード信号に変換し、当該差動信号及び当該コモンモード信号を1対の信号線を介して受信装置に送信する差動ドライバ34、及び受信装置からコモンモード信号に変換された第2コンソール信号を受信するコンソール信号受信回路35を有する送信装置1と、送信装置1から差動信号及びコモンモード信号を上記1対の信号線を介して受信し、当該差動信号を水平同期信号に復元する差動レシーバ54、受信されたコモンモード信号を第1コンソール信号に復元するコンソール信号受信回路56、及び第2コンソール信号をコモンモード信号に変換し、上記1対の信号線を介して送信装置1に送信する差動ドライバ34を有する受信装置2を含む。

(もっと読む)

画像表示装置及び該画像表示装置に用いられる映像信号処理方法

【課題】映像信号が映像信号線を経て差動伝送方式で伝送されるときに、配線クロストークによる伝送エラーが回避される画像表示装置を提供する。

【解決手段】表示制御手段(たとえば、タイミングコントローラ24)で生成された入力信号vaに基づいて、データ信号伝送線(映像信号線15)を構成する各信号線の間の配線クロストークによる影響の度合いが所定のタイミング(たとえば、1フレーム期間、1クロック期間、又は1水平期間)毎に判定され、この判定結果に基づいて、データ信号vjの電圧振幅が、データ線駆動回路(データドライバ131 ,132 ,…,13M ,13M+1 )入力振幅規格よりも所定の値だけ上回るように調整される。

(もっと読む)

データ信号断検出回路

【課題】AC結合とDC結合の何れによっても入力可能なデータ信号の遮断を検出するのにクロック信号を不要とする。

【解決手段】リミットアンプ1は入力差動アンプ20の正相側出力を入力し、リファレンス電圧Ref1でリミッティングして整流回路2へ出力する。コンパレータ3は、整流回路2の出力電圧とリファレンス電圧Ref2を比較して、論理値をインバータ5へ出力する。また、コンパレータ4は、整流回路2の出力電圧とリファレンス電圧Ref3を比較して、論理値をNAND回路6へ出力する。NAND回路6は、インバータ5から出力される論理値と、コンパレータ4から出力される論理値との否定論理積演算を行ない、その結果を信号断検出信号として出力する。

(もっと読む)

情報処理装置、及び信号伝送方法

【課題】2つの伝送路を利用して効率的にデータを伝送することが可能な情報処理装置を提供すること。

【解決手段】クロックにデータ信号を加算して加算信号を生成する信号加算部と、前記クロックから前記データ信号を減算して減算信号を生成する信号減算部と、第1の伝送路を通じて前記加算信号を伝送する第1信号伝送部と、第2の伝送路を通じて前記減算信号を伝送する第2信号伝送部と、を有する、第1のモジュールと、前記第1の伝送路を通じて受信した加算信号から前記第2の伝送路を通じて受信した減算信号を減算して前記データ信号の成分を抽出するデータ成分抽出部と、前記第1の伝送路を通じて受信した加算信号に前記第2の伝送路を通じて受信した減算信号を加算して前記クロックの成分を抽出するクロック成分抽出部と、を有する、第2のモジュールと、を備える、情報処理装置が提供される。

(もっと読む)

プリント配線基板及びプリント配線方法

【課題】送信側LSIから受信側LSIに高速信号を伝送するプリント配線の配線パターンを形成する際に、プリント配線に設けられたスルーホールやパッド、コネクタ等による容量性反射の影響を低減し、波形歪みの低減や伝送性能の向上を図ることができるようにする。

【解決手段】送信側LSIチップ21から受信側LSIチップ22に信号を伝送する伝送路をプリント配線13a、13bで形成する際に、そのインピーダンスを一定に保ちつつ、送信側LSIチップ21の近傍の線幅が太く、受信側LSIチップ22の近傍の線幅が細くなるようにプリント配線13a、13bの配線パターンを形成している。これにより、プリント配線13a、13bに設けられたスルーホール14a、14bによる容量性反射の影響を低減させ、波形歪みの低減や伝送性能の向上を図ることができる。

(もっと読む)

ボーレートエラー検出回路、ボーレートエラー検出方法

【課題】シリアル通信におけるシンクフィールドの異常波形を検出すること。

【解決手段】ボーレートエラー検出回路は、エッジディテクタと、スタートビットサンプリング回路と、異常波形検出回路とを備える。エッジディテクタは、シリアル通信のボーレートを調整するためのシンクフィールドを受け取り、シンクフィールド中のエッジに応答してエッジ検出信号を生成する。スタートビットサンプリング回路は、エッジ検出信号及び内部クロック信号に基づいてシンクフィールドのスタートビットのビット幅を計測し、計測されたビット幅を期待値として示す期待値信号を生成する。異常波形検出回路は、エッジ検出信号及び内部クロック信号に基づいてスタートビット以降のエッジ間の幅を計測し、エッジ間幅と期待値信号で示される期待値との間の誤差が所定の許容誤差範囲を超える場合に異常波形検出信号を生成する。

(もっと読む)

通信システム

【課題】ノイズ等に影響されるビット化けによるデジタル信号の誤認識を回避することができる通信システムを提供する。

【解決手段】通信システムを構成するマスタの通信装置の通信部は、フレーム中の各フィールド間に、デジタル信号の2値(0/1)に対応するロー(L)又はハイ(H)の電圧レベルとは異なる電圧レベルのインターバル信号を出力する。受信側のスレーブの通信装置では、通信線における電圧レベルをロー(L)か、又はハイ(H)かのみならず、ハイ(H)よりも高いV1以上であるか否かを判定し、インターバル信号を区別する。

(もっと読む)

送信回路

【課題】プリエンファシスと非プリエンファシスの2状態のデータを出力する送信回路において、データ変化点の波形のエッジに起因する電源変動、及びプリエンファシスと非プリエンファシスに起因する電源変動を抑制する。

【解決手段】図Aに示す第1回路、図Bに示す第2回路からなる。第1回路の第1回路の入力回路601g〜jには第1信号601n,601qと第1プリエンファシス信号601p,601rが入力される。第2回路の入力回路602g〜jには第2信号602n,602qと第2プリエンファシス信号602p,602rが入力される。第2信号は第1信号が変化するときは変化せずに、第1信号が変化しない時は変化する。第1回路の出力回路601a,601bと第2回路の出力回路602a,602bのどちらかがプリエンファシス状態となるので、出力回路全体で流れる電流値は一定となる。

(もっと読む)

クリッピング制御方法および装置

クリッピング制御方法および装置を提供するものであり、この方法は、現在のフレーム信号内の最大絶対値FrameLevに基づいてクリッピング要素を更新する段階と、クリッピング係数に従ってクリッピング回復フィルタを取得する段階と、クリッピング回復フィルタに従って現在のフレーム信号をフィルタリングする段階と、フィルタリング後のクリッピング回復信号を取得する段階と含む。クリッピング制御方法および装置は、クリッピング現象が発生したかどうかを自動的に検出してクリッピング回復を実行することができ、その結果、出力信号の主観的品質が向上する。  (もっと読む)

(もっと読む)

シリアル通信システム及びシリアル通信方法

【課題】MDライン及びSDラインの両方を同時にデータ送信に使用することができるシリアル通信システムを提供する。

【解決手段】本発明のシリアル通信システム1は、第1のデバイス2と第2のデバイス3とを有し、第1のデバイス2と第2のデバイス3とは、第2のデバイス3が生成したシリアルクロックに基づいて、相互通信を開始するシリアル通信システムである。第1のデバイス2から第2のデバイス3への出力が、前フェーズにおいて受信したデータの最終ビット値と反転していると、第2のデバイス3は第1のデバイス2の通信準備状態が完了状態であると判断し、相互通信を開始する。

(もっと読む)

周波数応答バス符号化

データシステムは、バスの周波数およびバスにおけるスイッチング周波数に基づいて、バスの符号化を行うことで、共振状態等の好ましくない周波数状態または他の電気装置との干渉を回避することができる。1つまたは複数のバスに沿った伝送周波数を監視および使用し、データバス反転(DBI)に基づいた符号化処理等の符号化処理を制御する。論理レベルの絶対数の尺度(「DBI_DC」)と前の信号に対する論理レベル遷移数の尺度(「DBI_AC」)の両方を使用することで、主およびプレドライバのスイッチングノイズの補正に使用可能な制御の尺度が提供される。 (もっと読む)

121 - 140 / 540

[ Back to top ]