Fターム[5K047GG23]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 受信信号よりタイミングの抽出 (1,089) | 抽出手段、原理 (419) | 受信信号特異点を利用 (164)

Fターム[5K047GG23]の下位に属するFターム

Fターム[5K047GG23]に分類される特許

1 - 20 / 32

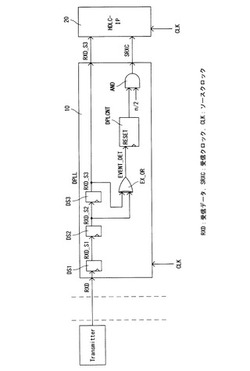

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

受信回路及びエラー検出方法

【課題】設計時のタイミング調整を容易とする受信回路及びエラー検出方法を提供すること

【解決手段】本発明にかかる受信回路は、位相の異なる複数のクロックを用いて、矩形波としてデータが遷移する受信シリアルデータビット列をサンプリングして、前記サンプリングされた受信シリアルデータビットを用いて受信データビット列を生成するDL回路部1と、前記サンプリングされた前記受信シリアルデータビットのうち、所定期間内に位相の異なるクロックを用いてサンプリングされた前記受信シリアルデータビットの値が一致するか否かを比較した結果に基づいて前記受信データビット列のエラー区間を検出するPD回路部2と、を備えるものである。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

シンボルクロック再生装置、復調装置、ナイキスト点判別装置、ナイキスト点判別方法、シンボルクロック生成方法、及びシンボル再生方法。

【課題】多値変調された変調波についても、正確にナイキスト点を検出する。

【解決手段】4値FSKで変調された変調波に対し、検波部11は各シンボル毎にn回サンプリングしてアイパターン上で隣接する収束点との距離を示す距離データを生成する処理を、Nシンボルに対して行う。クロック再生部20は、Nシンボル期間についてそれぞれ第iのサンプリング点の距離データを累算加算した累算値を算出する。クロック再生部20は、n個の累算値間の傾きを求め、その傾きからナイキスト点を抽出し、ナイキスト点のタイミングでシンボルクロックを発生する。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

復調装置

【課題】フルディジタル化による回路規模の増大を抑える。

【解決手段】フィルタ部3に入力する信号の同期点(ベースバンド信号波形の振幅が最大となる点)がタイミング同期部5で決定するシンボル同期タイミングによって予め判っているから、そのシンボル同期タイミングに同期したサンプル点のみを選択してフィルタ部3でフィルタ処理することができる。故に、フィルタ部3のダウンサンプラ31におけるダウンサンプリング数を源信号のビットレートと同程度まで下げることができ、その結果、フィルタ部3の演算量を減少させることができてフルディジタル化による回路規模の増大を抑えることができる。

(もっと読む)

位相補正方法及び位相補正装置

【課題】 大容量のシリアルデータ信号を比較的短い時間で転送でき、且つ、ジッタの影響を十分に抑えることができる位相補正方法及び位相補正装置を提供する。

【解決手段】 IrDA規格のFIRモードの赤外線通信可能な通信制御システムにおいて、受信したシリアルデータ信号をサンプリングタイミングに同期してサンプリングし、サンプリングで検出された補正対象パルス信号が、直前に検出された基準パルス信号の検出タイミングを基準とした2つのパルス開始タイミングの2等分点で検出された場合に、直前のパルス信号とのパルス間隔を求め、パルス間隔が第1基準間隔より短い場合は、補正対象パルス信号が直前の最も近いパルス開始タイミングのパルス信号であると判定し、パルス間隔が第2基準間隔より長い場合は、補正対象パルス信号が後の最も近いパルス開始タイミングのパルス信号であると判定する。

(もっと読む)

伝送システム、送信装置、受信装置、及び、伝送方法

【課題】受信装置で受信するデータに発生したビットエラーを低減させる回路を、小規模で簡易な論理ゲートの回路で提供する。

【解決手段】受信装置で受信するデータ列に発生したビットエラーを低減させる回路を、小規模で簡易な論理ゲートの回路で提供する。データ列を伝送する伝送システムであって、データに含まれるデータを取得すべきタイミングを示す第1タイミングエッジと、当該データの値に応じた信号レベルのレベル信号とを有するエッジ有データ波形に成形した第1伝送信号を送信する送信装置と、エッジ有データ波形の第1タイミングエッジにより指定されたタイミングで検出した信号レベルに応じたデータ値を出力する受信装置とを備える伝送システムを提供する。

(もっと読む)

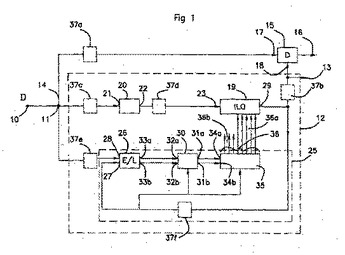

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

クロックリカバリ回路

【課題】シリアル伝送されるデータにノイズが混入しても、そのノイズの影響を少なくすることができるクロックリカバリ回路を提供する。

【解決手段】基準クロックから多相クロック生成部5で生成された多位相クロックのうち、入力されたシリアルデータの変化点の中間(真中)に立ち上がりがあるクロックを選択して出力するクロックリカバリ回路1において、入力データのエッジを検出した後に、所定以下の信号幅のノイズ成分を除去するノイズキャンセル部3を設け、ノイズ成分によるクロックの切替えが起らないようにしてクロック選択部4へ出力する。

(もっと読む)

ビット同期回路

【課題】受信機と送信側の間にタイミング誤差が残るような状況で長いデータを受信する場合でも、正しいビット同期点を表す信号を発生し続けることができるビット同期回路を提供する。

【解決手段】FSK復調回路に用いるビット同期回路において、サンプリング・極性判定回路の出力とデータの変化点付近の信号との相関を計算する相関回路12と、該相関回路12の出力の絶対値を出力する絶対値回路13と、該絶対値回路13の出力を予め決められた数のデータ周期分だけデータ周期内の時間位置を合わせて積分する積分回路14と、該積分回路14の出力のピーク位置からビット同期点を求めるピーク判定回路15と、リセット時にビット同期信号を出力するビット同期カウンタ16とを有し、該ビット同期カウンタ16はサンプリングクロックをカウントし、ピーク判定回路15から出力するピーク判定信号によりリセットされる。

(もっと読む)

非同期シリアル通信方法及び非同期シリアル通信装置

【課題】ある程度の高速性を得ながら、信号線数が少なく、回路規模を小さくする事の出来る非同期シリアル通信方法及び非同期シリアル通信装置を提供する。

【解決手段】送信側において、信号レベルを所定のレベルへ変化させた後、所定の第1時間T1の経過後から別に定めた第2時間T2以内に1ビットの送出データを送出するステップと、受信側において、信号レベルの変化を検出してから更に別に定めた第3時間T3(但し、T3>T1+T2)の経過後、または該第3時間T3の経過時点の何れかに、前記1ビットの送出データを取り込むステップとを含む。

(もっと読む)

クロック再生回路

【課題】レジスタのメモリサイズを増大させることなく、クロック再生処理を確実に行うことを可能とする。

【解決手段】送信信号から抽出されたPCRをバッファリングするレジスタを含むPCRバッファ22と、受信側基準クロックCKrをカウントするカウンタ24と、カウンタ24のカウント値をバッファリングするレジスタを含むSTCバッファ26と、PCRバッファ22及びSTCバッファ26に保持されている値に基づいて、送信側基準クロックと受信側基準クロックCKrとの誤差を示す信号を生成するCPU20と、を備える。このとき、PCRバッファ22及びSTCバッファ26に保持されている値がCPU20によって読み出される前に新たなPCRが入力された場合、PCRバッファ22及びSTCバッファ26を更新しない。

(もっと読む)

クロックデータ復元装置

【課題】トランスミッタ・クロック・ジッタや符号間干渉が大きい場合であっても安定してクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、サンプラ部10、検出部20、オフセット決定部30、クロック出力部40およびDA変換部50を備える。クロック信号CK,CKXの位相は、入力デジタル信号の位相と一致するよう調整される。サンプラ部10におけるオフセット付与量(±Voff)は、値D(n-1)がハイレベルである場合の第1信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整され、値D(n-1)がローレベルである場合の第2信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整される。復元されたクロック信号として、クロック信号CK,CKXの何れかが出力される。復元されたデータとして、デジタル値D(n)の時系列データが出力される。

(もっと読む)

シンボルタイミング検出装置及び無線端末装置

【課題】受信された変調信号のシンボルタイミングを検出して当該変調信号を復調する無線端末装置で、無線通信を行う無線周波数に周波数偏差が生じても、安定してシンボルタイミングを制御する。

【解決手段】サンプリング手段103がシンボル周期より短い周期で変調信号の信号値をサンプリングする。抽出手段117が複数のサンプリング点における信号値の中からシンボルタイミングの位置にあるとみなされる信号値を抽出し、復調手段107が抽出された信号値について復調を行う。サンプリング点復調手段110が各サンプリング点における信号値について復調を行い、値検出手段201が各サンプリング点における復調結果の電力値を検出し、シンボルタイミング制御手段113〜116が各サンプリング点における電力値に基づいて抽出手段117によりシンボルタイミングであるとみなすタイミングを制御する。

(もっと読む)

検証回路

【課題】クロック周波数が高くてもクロック復元回路(検証回路)を作る回路素子の最大動作速度の境界で幾つかの設計上の問題の克服を図る。

【解決手段】検証回路80は,循環制御レジスタ(32)の2個以上連続する記憶素子の第1セットに接続され,第1セット記憶素子のいずれかが第1値のときに第1状態を持ち,第1セット記憶素子の全てが第2値のときに第2状態を持つ第1チェック信号を生成する第1チェック手段82と、レジスタの2個以上の連続する記憶素子の第2セットを形成する残りの記憶素子に接続され,第2セット記憶素子のいずれかが第1値のときに第1状態を持ち,第2セット記憶素子の全てが第2値のときに第2状態を持つ第2チェック信号を生成する第2チェック手段84と、第1および第2チェック手段に接続され第1および第2チェック信号が同じ状態を持つとき制御パターンが不正であることを示す検出信号を生成する同一状態検出手段86とを備えるように構成する。

(もっと読む)

1 - 20 / 32

[ Back to top ]