国際特許分類[B81C3/00]の内容

処理操作;運輸 (1,245,546) | マイクロ構造技術 (6,196) | マイクロ構造装置またはシステムの製造または処理に,特に適合した方法または装置 (1,969) | 個別に処理された構成部品からの,装置またはシステムの組立 (639)

国際特許分類[B81C3/00]に分類される特許

21 - 30 / 639

アクチュエータ素子の駆動方法及び製造方法

【課題】変位の保持特性と繰り返し耐久性に優れたアクチュエータの創出。

【解決手段】イオン液体とポリマーからなる電解質膜の表面に、炭素含有導電性ナノ材料とイオン液体、およびポリマーとのゲル状組成物から構成されるアクチュエータ用導電性薄膜が相互に絶縁状態で少なくとも2個形成され、該層に電位差を与えることにより湾曲および変形を生じさせ得るアクチュエータ素子の駆動方法であって、前記アクチュエータ素子の作製及び/又は駆動を低水分及び/又は低酸素雰囲気中で行うことを特徴とするアクチュエータ素子の駆動方法。

(もっと読む)

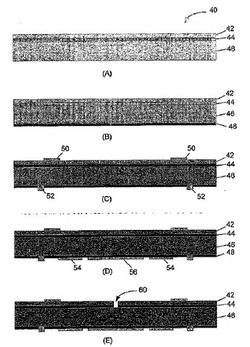

MEMSデバイス、及び介在物、並びにMEMSデバイス、及び介在物を統合するための方法

【課題】MEMSデバイスとの熱膨張の整合がよくとれた基板を有する構造の製造方法を提供する。

【解決手段】ボンディングされたエッチ・バック絶縁体上シリコン(以降は、BESOIと称する)方法に基づく。BESOI方法はSOIウェハ40を含み、該SOIウェハ40は、ハンドル・レイヤ46、二酸化ケイ素からなる誘電体レイヤ44、及びデバイスレイヤ42を有する。SOIウェハ40のデバイスレイヤ42をメサ・エッチングによってパターン形成した後、該SOIウェハ40を、パターン形成されたデバイスレイヤを有する別の基板にボンディングする。その後、SOIウェハ40のハンドル・レイヤ46、及び誘電体レイヤ44をエッチングによって除去される。さらに、デバイスレイヤ42をエッチングしてMEMS装置を形成する。このBESOI方法では、二酸化ケイ素誘電体レイヤ44が除去された後に構造エッチングが実行される。

(もっと読む)

密閉キャビティ形成のためのフリップチップハイブリダイゼーション方法、およびこのような方法によって得られるシステム

【課題】密閉キャビティ形成のためのフリップチップハイブリダイゼーション方法、およびこのような方法によって得られるシステムを提供する。

【解決手段】一方が他方の上に置かれ、その間に充填材料に埋め込まれた少なくとも1つの密閉キャビティが形成される、少なくとも1つの第1および第2マイクロ電子部品を含むマイクロ電子アセンブリの製造方法であって、側壁を用いてキャビティを規定する段階と、側壁と共同して充填材料に対するバイパスダクトを形成できる妨害物を形成する段階と、前記第1部品および前記第2部品のフリップチップハイブリダイゼーションを実施する段階と、前記2つのハイブリッド化部品の間に液体形態の充填材料を注入する段階と、を含む、マイクロ電子アセンブリの製造方法を提供する。

(もっと読む)

集積回路チップ上にセンサを垂直に積み重ねるためのシステムおよび方法

【課題】サイズが縮小され、熱検知性能が改善された検知装置パッケージ(20)を提供すること。

【解決手段】例示的パッケージは、複数のパターン、特定用途向け集積回路(アナログASIC)チップ(26)、および微小電気機械システム(MEMS)のダイ上に形成された微細機械加工されたセンサ(28)を有するプリント回路板(24)を含む。アナログASICチップは、プリント回路板に電気的かつ機械的に取り付けられる。MEMSのダイは、プリント回路板のパターンの一部分とのみ直接的に電気通信し、アナログASICチップに機械的かつ熱的に直接取り付けられる。MEMSのダイとアナログASICチップの間に熱伝導化合物(36)が配置される。1つまたは複数のはんだボール(32)が、アナログASICチップをプリント回路板に電気的に取り付け、1つまたは複数のはんだパターンが、MEMSのダイをプリント回路板に電気的に取り付ける。

(もっと読む)

マイクロ流路デバイスの製造方法及びマイクロ流路チップ

【課題】射出成形で得られる樹脂基板をマイクロ流路デバイスとして用いる場合であって、電極部を有するマイクロ流路デバイスの製造方法、及びそれを用いて製造したマイクロ流路チップを提供する。

【解決手段】第1基板2が流路を有し、第2基板3が電極部4を有する基板同士の接着が熱圧着であって、その熱圧着が、低温および高温の二温度の二段階で行い、二温度間の温度差が20度以上、50度未満であることを特徴として得られる。

(もっと読む)

磁気的に駆動されるマイクロポンプ

【課題】 小さい流体体積を取り扱うための磁気的に駆動されるマイクロポンプの提供。

【解決手段】 第一のチャンバ及び第二のチャンバを含むマイクロポンプであって、可撓性膜が第一のチャンバと第二のチャンバの間に配列され、可撓性膜は、膜を変位させるためのアクチュエータに磁気的に連結される。

(もっと読む)

電子デバイスの製造方法

【課題】比較的簡単な方法で、電子デバイスを構成する部材間の接合強度をより高めることが可能な電子デバイスの製造方法を提供する。

【解決手段】半導体基体2と、半導体基体2を実装する基体1と、半導体基体2を基体1側に接合する接合部3とを備えた電子デバイス10の製造方法であって、接合部3がAuを含む接合材料からなり、半導体基体2の接合部3側が接合材料を構成する元素以外から構成される母材材料からなり、基体1に設けた接合部3を溶融する温度以上に加熱して液相状態にした接合材料と固相状態の母材材料とを接触させる接触工程と、接触工程後に、Auと母材材料を構成する元素との合金の融点の温度以上に加熱して、半導体基体2を基体1側に接合する接合工程とを有する。

(もっと読む)

センサーデバイス、およびその製造方法

【課題】小型で信頼性の高いセンサーデバイス、及び、その製造方法を提供する。

【解決手段】センサーデバイス1は、第1の面10aに第1の電極11を有する半導体装置としてのICチップ10と、基部21、前記基部21から延伸された振動部を有し、第1の面10aと対向する第2の面20aに第2の電極としての引き出し電極29を有する振動片としての振動ジャイロ素子20と、を備えている。第1の面10aには、絶縁樹脂からなり第1の電極11と配線36を介して電気的に接続された第3の電極37の少なくとも一部を露出させる開口部32aを有する筒状支持部32が設けられ、第1の面10aおよび開口部32aにより形成された凹部に導電性接着剤98が埋設され、引き出し電極29に設けられたバンプ12が凹部内に配置されている。

(もっと読む)

貼り合せ構造体及び貼り合せ構造体の製造方法、並びに被処理基板の構造体の製造方法

【課題】被処理基板における凹凸形状を備えた面と下地基板の表面とを仮接着した後に減圧下において処理する際の、加工精度、処理効率、及び/又は処理の安全性を高める。

【解決手段】本発明の1つの貼り合せ構造体40の製造方法は、凹部42A及び凸部42Bが形成された第1表面を備える被処理基板41の第1表面42上に、25℃における粘度が0.02Pa・s以上0.1Pa・s以下である溶液状仮接着材を供給する溶液状仮接着材供給工程と、その溶液状仮接着材を加熱することにより、第1表面42の凸部42Bを10μm超20μm以下の厚みの仮接着材46Bによって覆う仮接着材形成工程と、その仮接着材46Bを介して、第1表面42と平板状の下地基板48とを一時的に貼り合わせる貼り合せ工程とを含む。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

21 - 30 / 639

[ Back to top ]