国際特許分類[C23C14/34]の内容

化学;冶金 (1,075,549) | 金属質材料への被覆;金属質材料による材料への被覆;化学的表面処理;金属質材料の拡散処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般;金属質材料の防食または鉱皮の抑制一般 (47,648) | 金属質への被覆;金属材料による材料への被覆;表面への拡散,化学的変換または置換による,金属材料の表面処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般 (43,865) | 被覆形成材料の真空蒸着,スパッタリングまたはイオン注入法による被覆 (14,491) | 被覆の方法に特徴のあるもの (7,808) | スパッタリング (3,573)

国際特許分類[C23C14/34]の下位に属する分類

磁界の適用によるもの,例.マグネトロンスパッタリング (349)

ダイオードスパッタリング (26)

トリオードスパッタリング (18)

外部のイオン源により作られたイオンビームによるもの (69)

国際特許分類[C23C14/34]に分類される特許

141 - 150 / 3,111

フッ化膜形成方法及び光学素子の製造方法

【課題】 スパッタリングを用いて安全・安価な方法で、可視領域において低吸収なフッ化膜を作成する方法を提供すること。

【解決手段】 本願発明は、金属ターゲットと反応性ガスを含む混合ガスを用いて、反応性スパッタにより基板上にフッ化膜を形成するフッ化膜形成方法において、前記混合ガスはO2ガス及び前記反応性ガスを含み、前記反応性ガスはフルオロカーボン系ガスであることを特徴とするフッ化膜形成方法である。

(もっと読む)

成膜装置

【課題】放電電圧を低下させることで、スパッタリング成膜時における下地層へのダメージを減少させることが可能な成膜装置を提供する。

【解決手段】一対のターゲット21A,21Bへの電圧を交互に供給する交流電源ユニット50を備える構成とし、ACデュアルカソードスパッタリング法において、フィラメント41から熱電子を放出させる。プラズマが形成された領域に、熱電子を供給することで、プラズマの放電電圧を低下させて、スパッタリング成膜時に下地層へ与えるダメージを低減する。

(もっと読む)

スパッタリング装置

【課題】ターゲット下方空間へのスパッタ粒子の飛散やプラズマの回り込み等を防止するといった機能を損なうことなく、ターゲットの外周縁部まで効率よく侵食領域とできてターゲットの利用効率が一層向上したスパッタリング装置を提供する。

【解決手段】スパッタ室1aで基板Wと共に配置されるターゲット31〜34のスパッタ面3a側を上として、ターゲットの下側に配置されてこのターゲットの上方にトンネル状の漏洩磁場M1,M2を形成する磁石ユニット41〜44と、ターゲットの長手方向をX方向、このX方向に直交する方向をY方向とし、磁石ユニットをX方向及びY方向の少なくとも1方向にターゲットに対して相対移動させる移動手段6とを備える。ターゲットの外周縁部から所定の隙間を存してターゲットの周囲を囲うように配置される、電気的に絶縁されたフローティングシールド5を更に有する。

(もっと読む)

In2O3−ZnO系スパッタリングターゲット及び酸化物導電膜

【課題】従来よりも抵抗値の低いIn2O3−ZnO系酸化物導電膜を形成することができるスパッタリングターゲットを提供する。

【解決手段】インジウム元素(In)、亜鉛元素(Zn)及び下記のA群から選択される少なくとも1つの元素(A)を含有し、In、Zn及びAの金属元素の組成(原子比)がInxZn(1-x)Ayで表わされる酸化物からなり、x及びyが下記式(1)及び(2)を満たすスパッタリングターゲット。

A群:Al、Mg、Ca、Sr、Ba、Sc、Y、Ti、Zr、Hf、Ga、B、Si、Ge、ランタノイド

0.68≦ x ≦0.95 (1)

0.0001≦ y ≦0.0045 (2)

(もっと読む)

物理気相成長中に加工物を支持する方法

【課題】物理気相成長中に加工物を支持する方法及び関連する装置を提供する。

【解決手段】吸熱性コーティング(15)でコートされた支持面を有するアルミニウム製支持体(11)が提供される。冷却によって、加工物が350℃〜450℃の温度になるように、支持体は約100℃に冷却されPVDプロセスが実施される。コーティングは、不活性であり及び/または超高電圧に適合できる。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

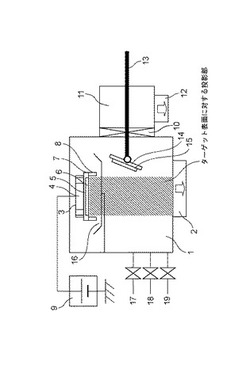

ロータリースパッタリングカソード、及びロータリースパッタリングカソードを備えた成膜装置

【課題】スパッタリングによるターゲットの消耗を抑えつつ、ターゲット表面に付着する付着物の除去を行うことが可能なロータリースパッタリングカソード、およびロータリースパッタリングカソードを備えた成膜装置を提供すること。

【解決手段】ターゲット21の外表面に付着した付着物を加熱して昇華させて除去する除去手段51、又は、付着物を機械的に除去する除去手段を備える構成とする。これにより、従前のような付着物除去のためのスパッタリングを不要とする。付着物を加熱して昇華させる除去手段としては、例えばフィラメント51を用い、付着物を機械的に除去する除去手段としては、例えばブラシ53を用いることができる。これにより、ターゲットの消耗を抑えつつ、付着物を取り除くことができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

141 - 150 / 3,111

[ Back to top ]