国際特許分類[G06F1/04]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875)

国際特許分類[G06F1/04]の下位に属する分類

複数のクロック信号を発生するクロック発生装置 (271)

クロック周波数が可変またはプログラマブルであるクロック発生装置 (148)

クロック信号の分配 (273)

異なるクロック信号の同期 (147)

時間監視装置,例.リアルタイムクロック (141)

国際特許分類[G06F1/04]に分類される特許

81 - 90 / 895

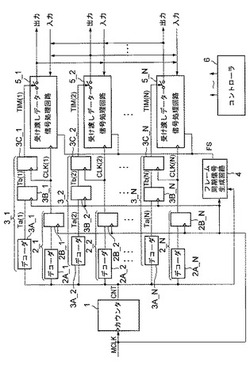

デジタル信号処理装置

【課題】フレーム同期式のDSPにおいて、動作クロックの異なる信号処理回路間のデータの受け渡しを簡便に実現する。

【解決手段】各々の動作クロックの異なる複数の信号処理回路のうちから送信側回路と受信側回路を定め、各信号処理回路の動作クロックの全ての立ち上がりエッジが揃うタイミングをデータ受け渡しタイミングとする。送信側回路には、当該送信側回路に与えられるタイミング信号がアクティブレベルであることを条件にデータを出力させる一方、受信側回路には、各動作クロックの周波数の約数を周波数とし、かつデータ受け渡しタイミングを跨ぐ所定期間に亘ってアクティブレベルとなるフレーム同期信号がアクティブレベルであることを条件に、送信側回路から出力されるデータを取り込む処理を実行させる。

(もっと読む)

通信装置及びクロック制御方法

【課題】データ送信部に送信データが保留されている間の消費電力を低減することができる通信装置及びクロック制御方法を提供すること

【解決手段】本発明にかかる通信装置は、供給されたクロックにより駆動し、対向装置に対してデータの送信を行う送信処理部34と、送信処理部34に対してクロックを供給する送信クロック制御部20と、対向装置に対するデータ送信の停止を指示するポーズフレームを受信する受信処理部31と、を備え、受信処理部31がポーズフレームを受信した場合、送信処理部34は、対向装置に対するデータ送信を停止し、送信クロック制御部20は、ポーズフレームにおいて指定される送信停止期間中の送信処理部34に対するクロック供給を停止するものである。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

電子情報機器、CPUクロック周波数設定方法およびプログラム

【課題】電子情報機器が、CPUに供給されるクロック信号の周波数を、より適切に設定できるようにする。

【解決手段】動作率算出部240が、例えばタスクの起動や停止から一定時間経過するまでなど、予め定められた一定時間におけるCPUの動作率を算出する。ここで、動作率は、CPUが動作状態にある時間的割合であり、動作状態は、CPUが何らかの処理を行っている状態である。そして、クロック設定部250は、動作率算出部240が算出した動作率に基づいて、CPUに供給されるクロック信号の周波数を設定する。

(もっと読む)

クロック発生器、電子機器、及びクロックを発生するための制御方法

【課題】周波数変調機能をオフした際のロックアップタイムを短縮することが可能なクロック発生器、及びクロック発生器の制御方法、並びに電子機器を提供すること。

【解決手段】周波数変調機能を有するクロック発生器で、リファレンスクロックを元にフィードバック制御を加えて、位相の同期した出力クロックを出力する位相同期ループと、出力クロックの周波数を変動させる変調制御回路と、を備え、変調制御回路は、周波数変調機能がオフされた際に、出力クロックの周波数を所望の周波数へ収束させるタイミングを速くする構成とする。

(もっと読む)

情報処理装置

【課題】PCの利用状況に適した電力制御を行える情報処理装置を提供する。

【解決手段】情報処理装置本体の稼働中のアプリを監視するアプリ監視手段と、情報処理装置本体の電力状況を監視する状況監視手段と、電力状況を記憶する記憶手段と、情報処理装置本体の動作状況及び電力状況に基づいて情報処理装置本体のハードウエアリソースの消費電力量の制限量を制御する制御手段と、を備えた。

(もっと読む)

マルチコアプロセッサにおける電力管理調整

【課題】マルチコアプロセッサにおける電力管理動作を調整するのに好適な技術を提供する。

【解決手段】各コアが対応する独立リソース設定を有し、第1コアと第2コアとを含む複数のコアにより共有される共有リソースに対して互いに異なる動作要求をする複数のコアと、複数の整合しない動作要求と、電力セービングポリシーと高パフォーマンスポリシーとの何れが重要である方に基づき共有リソースの設定を調整する調整ロジックとを有するプロセッサであって、調整ロジックは、電力状態遷移テーブルに基づき第1動作要求を第1目標値に、第2動作要求を第2目標値に変換し、第1目標値と第2目標値とを比較することによって第1動作要求と第2動作要求とを比較し、第2目標値が第1目標値より大きい場合、第2目標値を共有リソース設定として選択することによって、複数の整合しない動作要求に基づき前記共有リソース設定を調整する。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

プロセッサ、半導体集積回路装置及びプロセッサシステム

【課題】複数の周辺回路を備えたプロセッサ、半導体集積回路装置及びプロセッサシステムの処理能力を低下させることなく、消費電流を低減するプロセッサ、半導体集積回路装置及びプロセッサシステムを提供する。

【解決手段】プロセッサコア2と、プロセッサコア2からの命令に応答して所定の処理を実行する周辺回路3−1,3−2とを備えるプロセッサ7において、各周辺回路3−1,3−2は、プロセッサコア2からの命令に基づいて第1の全処理サイクル数を算出する算出部100と、比較部300からの分周比に基づいて、クロック信号を分周して出力するクロック発生部400と、第1の全処理サイクル数を、他の周辺回路の算出部100によって算出される上記他の周辺回路の第2の全処理サイクル数と比較して、当該比較結果に基づいて、当該周辺回路の処理終了時刻が上記他の周辺回路の処理終了時刻に近づくように上記分周比を発生する比較部300とを備えて構成される。

(もっと読む)

81 - 90 / 895

[ Back to top ]