国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

91 - 100 / 6,637

導電材料およびこれを用いた電気素子

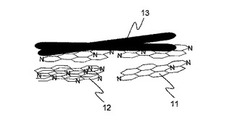

【課題】 フレキシブルで、軽く、安定で高導電性の導電材料およびこれを用いた電気素

子を提供する。

【解決手段】

本発明の導電材料は、少なくとも一つの次元方向が200nm以下であり、かつ炭素原

子の一部が少なくとも窒素原子に置換された単層グラフェン及び多層グラフェンの少なく

とも1種よりなるカーボン材料と、金属の粒子及び線材の少なくとも1種よりなる金属材

料とが、混合及び/又は積層されてなることを特徴とする。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

エッチング方法、エッチング装置、および記憶媒体

【課題】工程および装置構成を煩雑にすることなく、高エッチングレートで銅を異方性エッチングする装置、及びその方法を実施するプログラムを記憶した媒体を提供する。

【解決手段】チャンバ内に表面に銅膜104を有する基板101を配置し、チャンバ内を真空状態としつつ、チャンバ内に有機化合物106を供給し、銅膜に酸素ガスクラスターイオンビームを照射し、酸素ガスクラスターイオンビーム中の酸素ガスクラスターイオン107により、銅膜の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅膜を異方的にエッチングする。

(もっと読む)

半導体装置

【課題】高温環境下で使用することができる半導体装置を提供する。

【解決手段】第1インナー電極と第2インナー電極との積層からなるワイヤー接続領域を合金化防止溝によって第1アウター電極および第2アウター電極と分離することでワイヤーボンディング界面から成長したAu−Al合金層の進行を抑制し、半導体装置表面のパッシベーション膜のクラックを防止する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】中間層の形成時に、第2コイル46および第3コイル61によってターゲット53と基体11との間に磁力線M1が通るように磁場を発生させることによって、溝部12の内壁面に均一な厚みで中間層を成膜することが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

91 - 100 / 6,637

[ Back to top ]