国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

1,011 - 1,020 / 3,239

情報記憶素子、及び、情報記憶素子における情報書込み・読出し方法

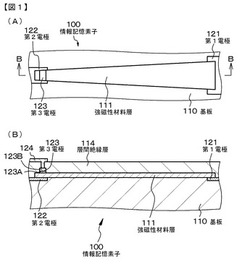

【課題】安定した磁壁の移動を可能とし、確実に情報の書き込み、保持、読み出しを行い得る磁壁移動型の磁気メモリから成る情報記憶素子を提供する。

【解決手段】情報記憶素子100は、帯状の強磁性材料層111を備えており、強磁性材料層の一端及び他端には第1電極121、第2電極122が設けられており、第1電極121と第2電極122との間に電流を流すことで電流誘起磁壁移動が生じ、強磁性材料層111において、磁化領域に磁化状態が情報として書き込まれ、若しくは、磁化状態が情報として読み出され、各磁化領域における磁化方向は、強磁性材料層111の厚さ方向に平行であり、情報の書込み若しくは情報の読出し時、強磁性材料層111の他端から一端に亙り単調に低下する温度分布を強磁性材料層111に生じさせる。

(もっと読む)

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

半導体集積回路装置

【課題】複数のMTJメモリセルアレイを同一チップ内に含む半導体集積回路装置の製造工程を効率化する。

【解決手段】システムLSI100は、複数のMRAM回路ブロック110a〜110fを備える。MRAM回路ブロック110a〜110fは、MTJメモリセルが行列状に配置されるMTJメモリセルアレイ10a〜10fをそれぞれ含む。MTJメモリセルアレイ10a〜10fの各々には、書込データに応じて双方向のデータ書込電流を流すためのビット線BLが配置される。MTJメモリセルアレイ10a〜10fのそれぞれにおけるビット線BLの延在方向は、システムLSI100上で同一方向である。

(もっと読む)

磁気メモリ、磁気メモリアレイおよび磁気メモリアレイへの情報書込み方法

【課題】 読出し時に熱的に安定で、かつ書き込み時の電流を低減した、スピントルク磁化反転応用の磁気ランダムアクセスメモリを提供する。

【解決手段】 強磁性体からなる固定層、非磁性障壁層、強磁性体からなる記録層、記録層と磁気的に結合した強磁性体からなる強磁性付加層が順次積層されたメモリ素子を備え、前記記録層の磁化方向と前記固定層の磁化方向が、略平行か、略反平行かによって情報の検出を行い、さらに前記記録層の磁化の方向を、前記記録層の膜面に垂直な方向に通電するスピン偏極した電流でスイッチングする磁気メモリにおいて、前記強磁性付加層の磁化方向が前記記録層と略平行とし、前記強磁性付加層の磁化の大きさが、150℃から250℃の温度範囲で消失する材料で、前記強磁性付加層を構成する。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】減圧されるチャンバ62と、チャンバ62内において、露出するレジスト膜49を有する半導体基板1を複数支持する基板ホルダ64と、基板ホルダ64の配置領域の外側に設けられ、チャンバ62内に酸素ガスを供給する供給孔72が複数箇所に形成されたガス供給管71と、チャンバ62内の流体を吸い込む排気孔が設けられた排気管74と、レジスト膜49をアッシングさせるための酸素ガスを活性化する高周波電源66と、を有する。

(もっと読む)

半導体記憶装置

【課題】磁気抵抗変化を利用したメモリセルによって構成された不揮発性メモリを有する半導体記憶装置において、メモリセルのスケーリングが進んでも読み出しディスターブを回避し、かつ高速に読み出し動作を行うことができる技術を提供する。

【解決手段】固定層、トンネル障壁膜および自由層が積層されてなるトンネル磁気抵抗素子とMISトランジスタとからなるメモリセルにおいて、メモリセルの情報の書き込み動作は、所望する第1電流値および第1時間によって行い、メモリセルの情報の読み出し動作は、メモリセルの温度を検知する温度センサを含むパルス発生回路によってメモリセルの動作温度に応じて設定される第2電流値および第2時間によって行う。

(もっと読む)

磁気抵抗効果素子および磁気メモリ

【課題】スピン注入書き込みに要する電流を低くすることを可能にする磁気抵抗効果素子及び磁気メモリの提供。

【解決手段】磁化の方向が固着された第1磁化固着層4と、磁化の方向が可変な磁化自由層6と、第1磁化固着層と磁化自由層との間に設けられたトンネルバリア層5と、磁化自由層のトンネルバリア層とは反対側に設けられ磁化が固着された第2磁化固着層8と、磁化自由層と第2磁化固着層の間に設けられた非磁性層7とを備え、第1磁化固着層と第2磁化固着層間に電流を流すことにより磁化自由層の磁化の方向が可変となり、第2磁化固着層が、Coを含む場合には、非磁性層にMn、V、Rhから選ばれた少なくとも1種の元素を含む金属であり、第2磁化固着層が、Feを含む場合には、非磁性層にIr、Rhから選ばれた少なくとも1種の元素を含む金属であり、第2磁化固着層が、Niを含む場合には、非磁性層にMnを含む金属である。

(もっと読む)

磁気抵抗効果素子とその製造方法および情報記憶装置

【課題】RA値を低く抑えつつ、MR比およびBDVの向上と、Hinの低減が可能な磁気抵抗効果素子を提供する。

【解決手段】磁気抵抗効果素子1は、磁化固定層14の上に絶縁層15が積層され、絶縁層15の上に自由磁性層16が積層される構造を有する磁気抵抗効果素子であって、磁化固定層14は、上面に酸素原子2原子分の厚さ以下の酸素結合層が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置にクラックの発生を防止する絶縁性応力緩和膜を用いながらも、下方からの水素の進入を阻止して容量絶縁膜の還元を防止できるようにする。

【解決手段】半導体装置は、第1の絶縁性水素バリア膜18と、その上に形成された第2の絶縁性水素バリア膜19と、第1の層間絶縁膜17、第1の絶縁性水素バリア膜18及び第2の絶縁性水素バリア膜19を貫通するコンタクトプラグ20と、第2の絶縁性水素バリア膜の上に順次形成され、下部電極23、容量絶縁膜25及び上部電極26よりなり、下部電極がコンタクトプラグと電気的に接続される容量素子27を備えている。第1の絶縁性水素バリア膜と第2の絶縁性水素バリア膜は、互いの組成比が異なる窒化シリコンよりなり、第2の絶縁性水素バリア膜のシリコン原子数に対する窒素原子数の比の値は、第1の絶縁性水素バリア膜のシリコン原子数に対する窒素原子数の比の値よりも小さい。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

1,011 - 1,020 / 3,239

[ Back to top ]