国際特許分類[H01L23/52]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

国際特許分類[H01L23/52]の下位に属する分類

半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

内部の相互接続を含むもの,例.クロスアンダ構造

絶縁基板の上または中に形成される複数の半導体チップ間の相互接続構造 (17)

国際特許分類[H01L23/52]に分類される特許

11 - 20 / 4,946

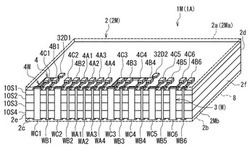

積層チップパッケージおよびその製造方法

【課題】正常に動作しない半導体チップを含んでいても、正常に動作しない半導体チップを含んでいない場合と同等の機能を有するパッケージを容易に実現できるようにする。

【解決手段】積層チップパッケージ1Mは、本体2と配線3を備えている。本体2は、積層された複数の階層部分を含む主要部分2Mと、主要部分2Mの上面と下面に配置された複数の端子を有している。配線3は複数の端子に接続された複数のライン(ワイヤW)を含んでいる。複数のラインは、複数の共通ラインと複数の階層依存ラインを含んでいる。各階層部分は、複数の共通ラインに接続された複数の共通電極と、複数の階層依存ラインに接続され、階層部分内の半導体チップに接触しない複数の非接触電極と、複数の階層依存ラインのうち、その階層部分が利用する階層依存ラインにのみ選択的に接続された選択的接続電極を含んでいる。階層依存ラインは、共通ラインに比べて最大の幅が大きい。

(もっと読む)

電子装置の製造方法及び電子装置

【課題】モールド樹脂の硬化時に、樹脂基板とベアチップとの相対位置が変動することにより、ベアチップの電極パッドと貫通電極とを再配線で接続する際の歩留まりが低下してしまうことのない電子装置の製造方法及び電子装置を提供する。

【解決手段】機能素子が形成されたチップ15を支持体に仮固定するとともに、絶縁部材17を前記支持体に仮固定する。支持体に仮固定したチップ15及び絶縁部材17を、樹脂層16で被覆する。チップ15、絶縁部材17、及び樹脂層16を、支持体から引き離す。絶縁部材17が露出するまで樹脂層16を研磨することにより、チップ15、絶縁部材17、及び樹脂層16からなる再構築ウエハ10を得る。再構築ウエハ10の絶縁部材17に貫通孔を形成し、貫通孔内に貫通電極18を形成するとともに、再構築ウエハ10の上に、チップ15と貫通電極18とを接続する配線21を含む再配線層20を形成する。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン層又はシリコン基板に補償ドープのために不純物を注入する必要がなく、安定的に高調波歪を低減する。

【解決手段】第1絶縁層20は、シリコン基板10上に形成されており、当該シリコン基板10に接している。また、配線40は、第1絶縁層20上に形成されている。ここで、第1絶縁層20下の不純物濃度は、2.0×1014cm−3以下である。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

貫通配線基板

【課題】高周波信号等の電気信号の伝送損失を低減し、貫通孔から導電物質が剥離することによる導通不良を抑制する貫通配線基板およびその製造方法の提供。

【解決手段】第1面と第2面とを有する基板2と;前記第1面と前記第2面との間を貫通する貫通孔24内に、導電性物質26を充填又は成膜することにより形成された貫通配線22と;を備える貫通配線基板20であって、前記貫通孔24は、変曲部22cと、該変曲部の両端に、該変曲部と接続する直線部22a、22bとを有し、前記変曲部の中心線に沿った断面の外周および内周のうち、少なくとも内周が円弧状であり、前記直線部のうち少なくとも一方の直線部は前記第1面又は第2面に対して垂直に開口する貫通配線基板。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の品質及び製造歩留まりを向上させる。

【解決手段】半導体装置の製造方法は、SOQウェハ等の貼り合せウェハに複数の半導体チップ部を形成する工程と、絶縁膜を含む下部層(611,621)とメタル配線(メタル層)を含む上部層(612,622)とを有する配線層(61,62)を形成するプロセスを複数回行うことによって、複数の半導体チップ部上に多層配線構造(6)を形成する工程とを有し、ダミーチップ部上に複数重ねられた配線層(61,62)は、製品チップ部上における配線層と同じ形状(パターン)を持つ第1の配線層(61又は62)と、第1の配線層と異なる形状を持つ第2の配線層(62又は61)とを含み、ダミーチップ部上に複数重ねられた配線層のいずれかにおける下部層(611又は621)は、貫通メタル配線を持たない絶縁膜である。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】正常に動作しない半導体チップを含んでいても、正常に動作しない半導体チップを含んでいない場合と同等の機能を有するパッケージを容易に実現できるようにする。

【解決手段】積層チップパッケージ1Mは、本体2と配線3を備えている。本体2は、積層された複数の階層部分10を含む主要部分2Mと、主要部分2Mの上面と下面に配置された複数の端子とを有している。配線3は、複数の端子に電気的に接続された複数のライン(ワイヤW)を含んでいる。複数のラインは、複数の共通ラインと、複数の階層依存ラインとを含んでいる。複数の階層部分10の各々は、複数の共通ラインに電気的に接続された複数の共通電極と、複数の階層依存ラインのうち、その階層部分10が利用する階層依存ラインにのみ選択的に、電気的に接続された選択的接続電極とを含んでいる。選択的接続電極は、どの階層依存ラインに電気的に接続されるかに応じて形状が異なっている。

(もっと読む)

メモリデバイスおよびその製造方法

【課題】コントローラチップや積層チップパッケージの大きさに関わらず、外部との接続を確実に確保し得るだけの汎用性の高い構造を備えたメモリデバイスおよびその製造方法を提供する。

【解決手段】メモリデバイス140は、積層チップパッケージ90と、コントローラプレート110とを有している。積層チップパッケージ90は、複数のメモリチップ50が積層されている。積層チップパッケージ90とコントローラプレート110との間に介挿チップ51が積層されている。コントローラプレート110の対向面に複数の対向配線電極113が形成されている。対向面の裏側に複数の外側配線電極112が形成されている。介挿チップ51は複数の介挿配線電極を有している。複数の介挿配線電極は、共通配置パターンで形成されている。

(もっと読む)

積層チップパッケージの製造方法

【課題】積層された複数の半導体チップを含む本体の側面に配線が配置された積層チップパッケージを、低コストで短時間に大量生産する。

【解決手段】積層チップパッケージは、複数の階層部分を含む本体と、本体の側面に配置された複数のワイヤを含む配線を備えている。積層チップパッケージの製造方法は、積層基礎構造物120を作製する工程と、積層基礎構造物120を切断する工程を備えている。積層基礎構造物120は、配列された複数の分離前本体2Pと、隣接する2つの分離前本体2Pの間に配置された複数の収容部133と、複数の収容部133内に収容された複数の予備ワイヤ143を含んでいる。複数の収容部133は、感光性樹脂層に対してフォトリソグラフィによって形成される。積層基礎構造物120を切断する工程において、複数の分離前本体2Pが互いに分離され、予備ワイヤ143によってワイヤが形成される。

(もっと読む)

11 - 20 / 4,946

[ Back to top ]