国際特許分類[H01L27/088]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | 電界効果構成部品のみを含むもの (6,291) | 構成部品が絶縁ゲートを有する電界効果トランジスタであるもの (5,861)

国際特許分類[H01L27/088]の下位に属する分類

相補型MIS電界効果トランジスタ (2,948)

国際特許分類[H01L27/088]に分類される特許

31 - 40 / 2,913

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

積層型半導体装置及びその製造方法

【課題】本発明は、接続電極のピッチを大きくせずにゲートの寄生容量を小さくすることができ、回路の高速化と層間接続の高密度化の両立が図れる積層型半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1のゲート60と、該第1のゲートよりも下層に形成された第1及び第2の不純物拡散領域31、33とを有する第1の半導体素子70と、

前記第1のゲートと対向して接合された第2のゲート65と、該第2のゲートよりも上層に形成された第3及び第4の不純物拡散領域36、38とを有する第2の半導体素子75と、を有することを特徴とする。

(もっと読む)

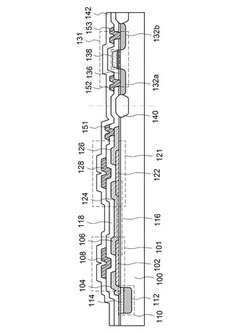

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の不純物濃度を好適に制御する半導体装置の製造方法を提供する。

【解決手段】第2トランジスタ170のゲート電極171を半導体基板1に対するマスクとして半導体基板1へイオン注入を行うことにより、第2トランジスタのドレイン175を形成するとともに、第2トランジスタ170のゲート電極171へイオン注入を行う。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

31 - 40 / 2,913

[ Back to top ]