国際特許分類[H01L27/088]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | 電界効果構成部品のみを含むもの (6,291) | 構成部品が絶縁ゲートを有する電界効果トランジスタであるもの (5,861)

国際特許分類[H01L27/088]の下位に属する分類

相補型MIS電界効果トランジスタ (2,948)

国際特許分類[H01L27/088]に分類される特許

41 - 50 / 2,913

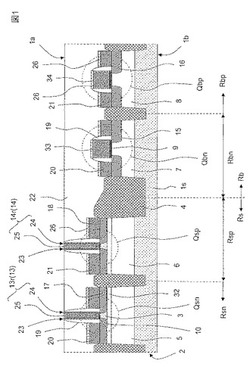

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

高移動度プレーナおよび複数ゲートのMOSFETのためのハイブリッド基板、基板構造およびその基板を形成する方法

【課題】プレーナあるいは複数ゲートまたはその両方の金属酸化膜半導体電界効果トランジスタ(MOSFET)で使用するための高移動度面を有するハイブリッド基板を提供すること。

【解決手段】ハイブリッド基板は、n型デバイスに最適な第1の表面部分と、p型デバイスに最適な第2の表面部分とを有する。ハイブリッド基板の各半導体層における適切な表面およびウェハ・フラットの方向により、デバイスのすべてのゲートは同じ方向に配向され、すべてのチャネルは高移動度面上に位置する。本発明は、ハイブリッド基板、ならびに、その上に少なくとも1つのプレーナまたは複数ゲートのMOSFETを集積する方法も提供する。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置

【課題】 半導体層にIGBT領域とダイオード領域が混在している半導体装置において、寄生ダイオードの動作を抑制する技術を提供する。

【解決手段】 半導体装置100は、素子範囲と、素子範囲を囲む終端範囲に区画された半導体層15を有する。素子範囲には、IGBT領域10とダイオード領域12が形成されている。半導体層15のうちのダイオード領域12の裏面部は、n型のカソード領域が形成されているカソード部分38aと、上記n型のカソード領域が形成されていない非カソード部分38bを有している。半導体装置100では、非カソード部分38bがダイオード領域12の中心側よりも端部側に相対的に多く存在する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

41 - 50 / 2,913

[ Back to top ]