国際特許分類[H01L29/74]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302)

国際特許分類[H01L29/74]の下位に属する分類

ゲートターンオフサイリスタ (51)

双方向サイリスタ,例.トライアック (21)

電界効果によりターンオンするもの (39)

国際特許分類[H01L29/74]に分類される特許

11 - 20 / 191

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出

来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有

する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われ

る回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる

電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置と

する。

(もっと読む)

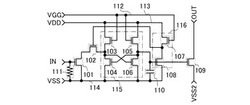

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置

【課題】例えばSIThyに適用した場合に、ゲート電極とカソード電極との短絡を防止すると共に、ゲート電流の増大、チャネル領域の面積の拡大を図る。

【解決手段】半導体基板12の一主面に複数のランド20と複数のグルーブ22が形成されている。ランド20の表面部にカソード領域24が形成され、グルーブ22の底部にゲート領域26が形成されている。グルーブ22内にゲート電極16が形成され、ランド20の上面にカソード電極14が形成されている。ランド20の上面とグルーブ22の底面にわたって絶縁膜28が形成されている。カソード電極14の側面とゲート電極16と絶縁膜28とを覆うように層間絶縁膜30が形成され、カソード電極14上面と層間絶縁膜30とを覆うように接続電極32が形成されて各カソード電極14が電気的に接続されている。グルーブ22の側壁とゲート電極16の側壁との間に絶縁膜28のみが介在している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐電圧特性の温度依存性を改善した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】アノード端子T2に、カソード端子T1に対して大きな電圧を印加したときに形成される空乏層DLに、N型半導体領域N4から到達する電子が増加しないように、N型半導体領域N4を、不純物を高濃度に含む高濃度N型半導体領域N4aと、高濃度N型半導体領域N4aに比較して不純物を低濃度に含む低濃度N型半導体領域N4bとが交互に配置される構成とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐電圧特性を改善した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】アノード端子Taに、カソード端子Tkに対して大きな電圧を印加したときに形成される空乏層DLの端部に、アノード層(P型エミッタ領域、P型半導体領域P2)から到達する正孔が増加しないように、アノード層の端部であるP型半導体領域P2bを、アノード層の中央部であるP型半導体領域P2aに対して低濃度の不純物領域で形成する。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置

【課題】トレードオフの関係にある臨界オフ電圧上昇率dV/dtとゲート感度との関係を改善した半導体装置を提供する。

【解決手段】少なくとも、ゲートトリガ電流IGTの経路となるベース層(P型ベース領域、P型半導体領域P1)のゲート電極M1bとのオーミック接触面である高濃度不純物層を、高融点金属シリサイド層LMで形成する。

(もっと読む)

半導体装置

【課題】保持電流特性とブレークダウン電圧に影響を与えずに、点弧動作感度の高感度化を実現する片導通サイリスタ(半導体装置)を提供する。

【解決手段】片導通サイリスタ100は、p領域1とn領域2とp領域3とn領域4とが順に接合されるサイリスタ部110と、n領域2とp領域3とが接合されたダイオード部120とを有する。片導通サイリスタ100は、ダイオード部120におけるn領域2に接する第1のダイオード部表面F12とダイオード部120におけるp領域3に接する第2のダイオード部表面F22との間に形成され、サイリスタ部110が導通する動作過程を示す点弧動作の際に、第1のダイオード部表面F12と第2のダイオード部表面F22との間に流れる電流経路を、第1のダイオード部表面F12と第2のダイオード部表面F22との最短経路より長くさせるn領域5を備える。

(もっと読む)

圧接型GTOサイリスタ

【課題】均一なターンオフ動作をさせ、ターンオフ動作の失敗による素子の破壊を抑制可能な圧接型GTOサイリスタを提供することを目的とする。

【解決手段】本発明にかかる圧接型GTOサイリスタは、半導体基体12と半導体基体12上に平面視環状に配置されてカソード電極18を形成するエレメントパターンと、環状の中央近傍において、半導体基体12上に圧接されたゲート電極38と、ゲート電極38の所定方向の側面に接続されたゲートリード44とを備え、環状の中心位置である第1平面中心Aが、ゲート電極38の平面視における中心位置である第2平面中心Bに対し、所定方向にずれて位置する。

(もっと読む)

11 - 20 / 191

[ Back to top ]