国際特許分類[H03K17/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 完全導通状態を確保するための変形 (176)

国際特許分類[H03K17/06]に分類される特許

61 - 70 / 176

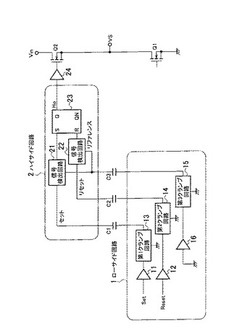

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

昇圧回路、および降圧回路

【課題】入力電圧を昇圧して出力する半導体集積回路における、トランジスタの耐圧が、入力電圧以下に抑えられる昇圧回路を提供する。

【解決手段】コンデンサCpは、一方の端子がクロック信号を出力するクロック端子に接続され、他方の端子が整流回路4に接続されている。コンデンサCpの他方の端子の最低電圧を第1の電圧にクランプするクランプ回路3を備えている。このクランプ回路3は、第1のN型トランジスタN1、および第2のN型トランジスタN2を有している。この第1のN型トランジスタN1は、ドレインをコンデンサの他方の端子に接続し、ソースを前記第2のN型トランジスタN2のドレインに接続し、さらに、ゲートを第1の電圧よりも高い第2の電圧Vaに接続している。また、第2のN型トランジスタN2は、ソースを第1の電圧Vpに接続し、ゲートを前記クロック信号の反転信号を出力する反転信号端子に接続している。

(もっと読む)

PLL回路

【課題】ノイズの抑圧を効果的に行うことができるPLL回路を提供する。

【解決手段】位相比較器10と、チャージポンプ回路20と、ループフィルタ30と、VCO40と、N分周器50とを備える。チャージポンプ回路20の一実施形態は、アップ信号UP1によりスイッチ22をオンした後、アップ信号UP1を遅延させたアップ信号UP2により再度スイッチ22をオンする。同様に、ダウン信号DN1によりスイッチ23をオンした後、ダウン信号DN1を遅延させたダウン信号DN2により再度スイッチ23をオンする。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続され、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トランジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジスタのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする。

(もっと読む)

DC−DCコンバータ

【課題】出力短絡保護機能を設ける場合に、短絡電流をバイパスするバイパス回路を外部に設けることなく、内部回路(内部素子)を保護できるDC−DCコンバータの提供。

【解決手段】この発明は、直流電圧を昇圧して出力電圧を生成し、当該出力電圧の生成のために入力端子1と出力端子2との間に複数のMOSトランジスタM1〜M4が直列接続されたDC−DCコンバータである。MOSトランジスタM4は、自己の基板電位制御用のMOSトランジスタM41、M42を有する。DC−DCコンバータの定常動作時にはMOSトランジスタM42がオンし、MOSトランジスタM4の基板端子に出力端子2の電位が印加される。一方、DC−DCコンバータの出力短絡時にはMOSトランジスタM41がオンし、MOSトランジスタM4の基板端子に出力端子2とは反対側の電位が印加される。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電位が昇圧規定電位に達し、小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路1は、制御部10と発振回路20と昇圧部30とを具備する。発振回路20は、予め定められた一定周期のパルス信号を出力する。昇圧部30は、電位を昇圧するn(n≧1)個の昇圧回路を備え、発振回路20から出力されるパルス信号に応じて第1の電荷量を出力する。制御部10は、昇圧部30から出力される電位と、予め定められた規定電位とを比較し、昇圧部30から出力される電位が一旦規定電位より大きくなると、昇圧部30に第1の電荷量より少ない電荷量を出力させる。

(もっと読む)

半導体スイッチング装置

【課題】ノーマリオン型の半導体素子を用いて、より安全なノーマリオフ的な動作となる簡単な構成の半導体スイッチング装置を提供する。

【解決手段】市販のゲートドライバ11を用いて、ノーマリオン型のJFET10を駆動する。このとき、NチャネルのJFET10のソースSをゲートドライバ11の高圧側の電源ノード12に接続し、ゲートGをゲートドライバ11の出力ノード15に接続する。入力された制御信号VsigがLレベルの場合、出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。したがって、Lレベルの制御信号Vsig入力に対して、ゲート・ソース間に負の閾値電圧以下の電圧が印加されてJFET10がターンオフするというノーマリオフ的な動作が実現している。

(もっと読む)

負荷駆動回路

【課題】負荷電流が大なる場合でも損失電力を小とし、システム全体を小型化し、その上電力効率も上げ得る負荷駆動回路を提供する。

【解決手段】信号源(4)と、信号源(4)よりの入力信号と負荷電流検出部(R3)よりの検出信号とを受けて差演算を行い、その出力をOPアンプ(1)の非反転入力端子に入力する演算回路(8)と、前記入力信号を受け、その極性に応じて、正又は負のコントロール信号を出力する可変/固定電圧選択回路(5)と、この可変/固定電圧選択回路からの正のコントロール信号を受けて所定の正電源電圧をNPN型トランジスタ(Q1)に供給する第1の電源供給部(6)と、可変/固定電圧選択回路からの負のコントロール信号を受けて所定の負電源電圧をPNP型トランジスタ(Q2)に供給する第2の電源供給部(7)と、を備える。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】 電力変換装置の各アームを構成する半導体素子に対して設けられるフリーホイーリングダイオードのサージ電圧を抑制し、半導体素子のターンオン損失を低減する。

【解決手段】従来のゲート駆動装置に対し、抵抗R,コンデンサCからなる遅延回路、抵抗Rg(on)1およびトランジスタTR10を接続することにより、フリーホイーリングダイオード逆回復時の低電流域では、半導体素子IGBTを抵抗Rg(on)により、また高電流域では抵抗Rg(on)と抵抗Rg(on)1との並列抵抗により、それぞれターンオンさせることで掲記課題の解決を図る。

(もっと読む)

チャージポンプ回路

【課題】位相比較周波数が高い場合にも、フリッカ雑音の影響を小さくし、チャージポンプ回路の出力の雑音密度のオフセット周波数依存を小さくする。

【解決手段】PLL回路に設けられ、位相比較回路が出力する制御信号に従って電流吐き出し用の電流源と電流吸い込み用の電流源をオン・オフ制御するチャージポンプ回路において、蓄積期間信号に従って前記電流源からの電荷を蓄積し、出力期間信号に従って蓄積された電荷を出力する電荷蓄積・放出回路を備え、蓄積期間信号は、位相比較回路からの制御信号の複数周期に跨った期間を持つように設定される。

(もっと読む)

61 - 70 / 176

[ Back to top ]