Fターム[2G132AD00]の内容

電子回路の試験 (32,879) | 試験項目 (2,469)

Fターム[2G132AD00]の下位に属するFターム

電圧、電流、電力 (565)

パラメトリック特性 (57)

インピーダンス (95)

周波数、位相 (83)

論理値(HL)の電圧 (48)

論理パターンの一致 (617)

遅延時間、タイミング (406)

波形、パルス幅 (101)

断線、短絡、配線状態 (421)

発熱検知 (19)

Fターム[2G132AD00]に分類される特許

21 - 40 / 57

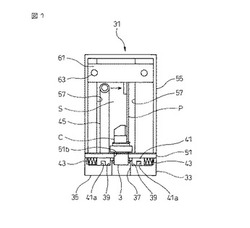

プリント基板保持装置

【課題】カバー部を強固にチャックすることができ、高速移動、高精度位置決めが可能なカバー部を有するプリント基板保持装置を提供する。

【解決手段】このプリント基板保持装置31は、プリント基板Pを保持する保持部33と、プリント基板Pを覆い、このプリント基板Pを保持部33とともに閉空間Sに閉じ込めるカバー55と、このカバー55内に配設され前記プリント基板Pに所定の気体を供給するノズル体45とを備え、カバー55の側面でこのカバー55の重心より上方の近傍に、カバー55の幅又はそれ以上の長さを有するガイドバー61を設け、このガイドバー61は位置決め穴63を有する。

(もっと読む)

実装基板検査システムおよびそのシステムにおける検査方法

【課題】実装基板検査システムおよびそのシステムにおける検査方法において、検査の開始から終了まで実装基板が結露するのを防止しつつ、検査時間を短時間化する。

【解決手段】実装基板検査システム10は、実装基板を内部に入出可能に支持する断熱筐体31と、断熱筐体31に設けられ同断熱筐体31内の温度を調整するための熱媒体を導入するとともに閉塞手段によって閉塞可能な導入口36と、を備えた搬送可能な複数の検査箱30と、実装基板20が収納されている検査箱30と脱着可能に接続され、実装基板20の温度の調整を実施するために使用されるものである少なくとも1つの温度調整装置50と、実装基板20が収納されている検査箱30と脱着可能に電気的に接続され、実装基板20の電気的特性の検査を実施するために使用されるものである少なくとも1つの検査装置40と、を備えている。

(もっと読む)

半導体検査装置および半導体検査手法

【課題】多数個の半導体デバイスに対してそれらの電気特性を同時に検査する場合でも、個々の半導体デバイスについて正確に検査することで製品としての歩留り低下を確実に抑えることができる半導体検査装置および半導体検査手法を提供する。

【解決手段】多数個の半導体デバイスを検査する際に、以前に実施されメモリ99に格納された別の検査または製造における判定結果または測定値、あるいは、今回の検査においてメモリ99に格納された過去の判定結果または測定値を元に、今回検査対象となる半導体デバイスの中で、同時に検査する半導体デバイスの組合せを決定する組合せ決定手段105を備える。

(もっと読む)

インターフェイス回路

【課題】テストコストの低減化およびテスト精度の向上を図ることが可能なインターフェイス回路を提供する。

【解決手段】このインターフェイス回路35は、テスタ30の出力信号を受けるバッファ40と、DUT27の出力信号の反射を抑制する負荷回路44と、バッファ40の出力信号を受ける切換端子43aと、DUT27に接続される切換端子43bと、負荷回路44に接続される切換端子43cとを有する高速切換スイッチ43と、入力ノードが切換端子43bに接続され、DUT27の出力信号をテスタ30に伝達させるバッファ42とを備える。したがって、テスタ30とDUT27の間においてミスマッチングが生じている部分の長さを短縮できる。

(もっと読む)

電源ノイズ測定装置,集積回路,および半導体装置

【課題】集積回路内部において発生した電源ノイズを正確に測定できるようにする。

【解決手段】集積回路10の内部に配設され、集積回路10の電源電圧間に接続された第1インダクタと集積回路10の外部出力端子15a,15bに両端をそれぞれ接続され第1インダクタに対向する第2インダクタとからなる相互誘導インダクタ対2と、この相互誘導インダクタ対2の第2インダクタから外部出力端子15a,15bを介して出力された電圧波形に基づいて、集積回路10の電源ノイズを測定する電源ノイズ測定部5とをそなえて構成する。

(もっと読む)

コンパレータのスキュー測定方法

【課題】測定精度の向上を図るとともに、その測定時の実行時間の短縮を図るようにしたコンパレータのスキュー測定方法の提供。

【解決手段】遅延回路16−1〜16−3に各遅延量を設定し、クロック遅延回路13に遅延量を設定する(S31〜S33)。コンパレータ18−1に基準クロックを校正用ドライバ2を経て供給すると同時に、その基準クロックをクロック遅延回路13、遅延回路16−1で遅延させてストローブ信号とする。コンパレータ18−1は、そのストローブ信号の供給タイミングで基準クロックのパス/フェイルの判定を100回行い、フェイル数を求める(S35)。同様に、コンパレータ18−2、18−3についても、その各フェイル数を求める(S38、S39)。その各フェイル数について、予め作成してあるフェイル分布と照合し、これによりコンパレータスキューを求める(S43)。

(もっと読む)

演算増幅器を含むアナログ回路の入出力特性測定装置及び演算増幅器を含むアナログ回路の入出力特性測定方法

【課題】演算増幅器の出力信号のオフセット及びゲインを目標値に調整するための調整値(抵抗値)を容易に求めることができ、この調整値をもとに、予め設けた調整用回路素子(抵抗器)を該オフセット及びゲインが目標値となるように削除可能とすること。

【解決手段】測定用電源304によって被測定回路302に複数の既知電圧VFを印加し、この際、第1〜第3の電圧測定部306〜308によって、レベル変換器(演算増幅器)120の出力電圧VLEV_M、PWM/アナログ変換器90aの出力電圧VCTI、レベル変換器120のオフセット電流を供給する電源電圧Vcc1を測定する。演算部310によって、それら測定値の各相関関係から、レベル変換器120の入出力特性及びレベル変換器120の出力側以降の入出力特性を求めて、レベル変換器120のオフセット及びゲインを目標値とするための調整値を求める。

(もっと読む)

半導体装置の検査方法

【課題】半導体ウェハに形成された欠陥検査用配線に生じる欠陥を容易に検出する。

【解決手段】半導体ウェハ10に欠陥検査用配線20を形成する際、欠陥検査用配線20の幅を厚さより小さく形成する。これにより、欠陥検査用配線20の厚さを確保しつつ、欠陥検査用配線の断面(配線の長手方向に垂直な断面)の断面積を小さくし、欠陥検査用配線20に熱ストレスや上層膜からの応力の影響を受けやすくさせる。すなわち、ウェハ工程においてパターニング等によるストレスによって欠陥検査用配線20内に欠陥が発生すると、その欠陥が抵抗となって、欠陥検査用配線20の抵抗値が増大するため、欠陥検査用配線20内の欠陥を容易に、かつ、高感度に検出することができる。

(もっと読む)

半導体集積回路及びそれを用いたデューティ測定・補正方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定及び補正する。

【解決手段】 半導体装置20には、半導体集積回路としてのデューティ測定・補正回路1及びPLL回路4が設けられている。デューティ測定・補正回路1は、デューティ測定回路部2及びデューティ補正回路部3から構成され、デューティ比が変化した補正前クロック信号CLKAが入力される。デューティ測定回路部2から出力される信号Outが“Low”レベルから“High”レベルに変化したときのデューティ測定回路部2の遅延回路の遅延時間が補正前クロック信号CLKAのデューティとして、デューティ測定回路部2で測定される。このとき、デューティ測定回路部2の遅延回路と対をなすデューティ補正回路部3の遅延回路が選択されて、補正前クロック信号CLKAのデューティがデューティ補正回路部3で補正される。

(もっと読む)

半導体リーク電流検出器とリーク電流測定方法および電圧トリミング機能付半導体リーク電流検出器とリファレンス電圧トリミング方法およびこれらの半導体集積回路

【課題】ビット線リーク電流は不揮発性メモリのしきい値制御を阻害し、信頼性を低下させる。微小なビット線リーク電流を低コストにテストする手法および回路を提供する。

【解決手段】本発明の半導体リーク電流検出器は、被測定電流を導通させ、または非道通にする第1のアナログスイッチと、リファレンス電流を導通させ、または非道通にする第2のアナログスイッチと、前記第1のアナログスイッチおよび第2アナログスイッチに接続され、前記被測定電流または前記リファレンス電流によって充電される積分容量素子と、前記積分容量素子をディスチャージするディスチャージ手段と、ディスチャージ後にリファレンス電流によって前記積分容量素子に生じる積分電圧、およびディスチャージ後に被測定電流によって前記積分容量素子に生じる積分電圧のそれぞれと、リファレンス電圧とを比較する比較手段とを備える。

(もっと読む)

通信装置

【課題】CDR回路を有する双方向通信回路のループバックテストにおいて、クロックの結線及びCDR回路内の全回路を高速でテスト可能とする。

【解決手段】PLLからCDR回路へのCDR用多相クロックを入力としクロック選択信号に基づきCDR用多相クロック信号のいずれか1つを選択して出力するクロック選択回路を備えている。ループバックテスト時、クロック選択回路で選択されたクロック信号が送信クロックとして用いられ、送信データは入出力兼用端子にて折り返されて受信回路に入力され受信回路からのデータがCDR回路に入力され、比較回路はCDR回路からの再生データと期待値データの比較を行うことでテストが行われる。クロック選択回路で送信クロックの位相を可変させることで、送信回路遅延時間(tTx)と受信回路遅延時間(tRx)の和の遅延時間(=tTx+tRx)が可変自在とされる。

(もっと読む)

半導体チップおよびその試験方法

【課題】破損箇所を簡単に特定することを可能とする半導体チップおよびその試験方法を提供する。

【解決手段】入出力パッドP0〜P10のそれぞれにアノードを接続するようにダイオード13を設ける。各ダイオード13のカソードに共通に接続し、また、半導体チップ3の周縁に沿って入出力パッドP0〜P10を囲むように破損検出用配線12を設ける。そして、破損検出用配線12の一端に、テスト用パッドP13を設ける。テスト用パッドP13に接地電圧を印加した状態で、各入出力パッドP0〜P10に対して正の定電流を印加して電圧測定を行うことにより、半導体チップ3の破損の検出および破損箇所の特定を行うことができる。また、ダイオード13のアノードとカソードとを逆にして接続することも可能である。

(もっと読む)

評価用半導体装置、及び評価用半導体装置の製造方法

【課題】評価用半導体装置の二次実装評価をするのに、かかる工数を抑えて、早く評価す

ることができる評価用半導体装置、及び評価用半導体装置の製造方法を提供する。

【解決手段】評価用半導体装置11は、二次実装評価を行うために用いられ、ボンディン

グパッド23が形成されたダミーチップ12と、ダミーチップ12が搭載されるインター

ポーザー15と、インターポーザー15に設けられたハンダボール14と、ボンディング

パッド23からハンダボール14に至るまでを電気的に接続するためのボンディングワイ

ヤ13とを有する。ダミーチップ12は、製品であるICチップとしての機能を必要とし

ないことから、ボンディングパッド23の形成を、インクジェット法によって所望の位置

や形状に印刷する。これにより、早く評価用半導体装置11を製造することができ、二次

実装評価を早く行うことができる。

(もっと読む)

半導体メモリ

【課題】テスト時間を短縮する。

【解決手段】2ビット以上の情報を記憶単位として記憶する複数のメモリバンクとデータバッファを有する。テストモードにおいてデータバッファが保持する前記情報の記憶単位毎の値のうち一の値を持つものとその他の値を持つものとを区別する制御データをメモリバンクのセンスラッチに並列転送し、前記制御データの転送を受けたメモリバンクにおいて、指定されたワード線の選択によってビット線に得られる状態が前記転送された制御データに基づいてビット線に得られる状態に一致するか否かを判定する。不一致の判定結果を得たメモリバンクを除いて、対応するデータバッファが保持する前記情報の記憶単位毎の値のうち別の一の値を持つものとその他の値を持つものとを区別する制御データを対応するメモリバンクのセンスラッチに並列転送して前記判定を行い、前記判定結果が不一致となったメモリバンクを外部から識別可能にする。

(もっと読む)

検査回路および検査システム

【課題】トランジスタの閾値判定を、アナログテスタを用いて簡単に、かつ、比較的短時間で行う。

【解決手段】N個(たとえば8)のトランジスタに基準電圧を印加した状態で、8個のトランジスタから、基準電圧VRを基準とする各閾値電圧の大小を表す8ビットの並列データS10を出力させるデータ出力回路41と、8ビットの並列データS10を直列ビット列S42に変換する変換回路42と、直列ビット列S42のパルス数を計数し、計数値をアナログテスタ6に出力する計数回路(カウンタ44)とを有する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】ファンクションテストにより電流源の動作確認を可能とする。

【解決手段】第1、第2の入力信号を差動入力とする第1、第2の差動対を備え、第1、第2の差動対の出力対は共通接続され負荷回路に接続され差動出力端子に接続され、第1乃至第4の電流源と、第1乃至第4のスイッチ対を備え、第1乃至第Nのスイッチ対の各一方のスイッチは一端は、それぞれ、前記第1乃至第4の電流源に接続され、他端は前記第1の差動対に共通接続され、第1乃至第4のスイッチ対の各他方のスイッチは一端は、それぞれ、前記第1乃至第4の電流源に接続され、他端は前記第2の差動対に共通接続され、前記第1乃至第Nのスイッチ対の制御端子には、制御信号がそれぞれ接続され、制御信号にパタンを印加し、出力信号と期待値を比較するファンクションテストにより電流源の動作確認を可能としている。

(もっと読む)

不揮発性半導体記憶装置及びそのテスト方法

【課題】 正常なメモリセルを過消去状態に導く相互インダクタンス不良の不良メモリセルを検出する不揮発性半導体記憶装置のテスト方法を提供する。また、検出された不良メモリセルを冗長救済する不揮発性半導体記憶装置を提供する。

【解決手段】 フローティングゲートの形成されたトランジスタを有するメモリセルを行方向及び列方向に夫々複数配列したメモリセルアレイを備えた不揮発性半導体記憶装置のテスト方法であって、消去動作後に、制御ゲート電圧を変化させ、各制御ゲート電圧に対するドレイン電流を読み出し、各ドレイン電流からメモリセルの相互コンダクタンスまたは対応する相当値を求め、予め設定された所定の基準値と比較し、相互コンダクタンスまたは対応する相当値が基準値以下の場合にメモリセルが相互コンダクタンス不良であると判定する。

(もっと読む)

半導体集積回路、設計支援ソフトウェアシステム、および、テストパターン自動生成システム

【課題】メモリ回路の縮退故障および遅延故障のテストを低コストで実施可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、冗長セル2を有するメモリ回路3と、救済コードに基づいて、メモリ回路3を救済する論理が決定されるヒューズ回路4と、ヒューズ回路4の出力信号により制御される第1のレジスタ5と、縮退故障をテストするためスキャン設計された第2のレジスタ6と、第1および第2のレジスタ5、6の出力信号を切替えるレジスタ選択回路7と、メモリ回路3の入力を故障セル1aが接続された経路を含む第1の信号経路から故障セル1aを回避し冗長セル2が接続された経路を含む第2の信号経路に切替える第1および第2の切替回路10a、10bと、縮退故障をテストするためのメモリ迂回回路11と、第1および第2の切替回路10a、10bを制御する信号を出力するデコード回路12と、を備える。

(もっと読む)

EMI低減動作テスト回路

【課題】 ASIC等の半導体チップ内部に設けたEMI低減変調回路の変調ON/OFF動作の確認を安定して高信頼に行う。

【解決手段】 ASIC内に、ASICのクロック周波数をダウンスプレッド/センタースプレッド変調してEMI低減するSSCG回路1と、SSCG回路1の出力クロックでカウントアップする第1のカウンタ3と、第1のカウンタ3によるカウント動作を所定期間に制限する第1の制御手段(第2のカウンタ2、第2の比較器4、リセット回路5、第3のレジスタ6)と、第1のカウンタ3によるSSCG回路1の変調ON動作時における所定期間でのカウント値を記憶する第1のレジスタ7と、変調OFF動作時における所定期間でのカウント値を記憶する第2のレジスタ8と、第1,第2のレジスタ7,8で記憶したカウント値を比較して一致もしくは不一致のいずれかを示す信号(H/L)を出力する第1の比較器9とを設ける。

(もっと読む)

半導体集積回路とそのジッタ測定方法

【課題】内蔵するPLLのジッタを正確に測定できる半導体集積回路とそのジッタ測定方法を提供する。

【解決手段】テストクロック信号TCKの立ち上がり時点において、マスタクロック信号MCKの状態をFF38で保持し、このFF38の出力信号とテストクロック信号TCKを反転した信号のANDを取ってカウンタ34のクロック端子に入力する。これにより、テストクロック信号TCKの立ち上がり時点でマスタクロック信号MCKが“H”である回数をカウントすることができる。従って、ロジックテスタ等の測定器から出力するテストクロック信号TCKの立ち上がりのタイミングを順次ずらして、その立ち上がりのタイミングにおけるマスタクロック信号MCKの状態をカウントすることにより、このマスタクロック信号MCKのジッタを正確に測定することができる

(もっと読む)

21 - 40 / 57

[ Back to top ]