Fターム[2H092JB69]の内容

液晶−電極、アクティブマトリックス (131,435) | アクティブ基板の能動素子以外の構造 (19,547) | 容量素子 (3,806) | 容量素子の接続 (1,973) | 容量素子用配線を設けたもの (1,655)

Fターム[2H092JB69]に分類される特許

61 - 80 / 1,655

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】第1方向に沿って延出し第2方向に沿って第1ピッチで配置された第1ゲート配線及び第2ゲート配線と、第2方向に沿って延出し第1方向に沿って第1ピッチよりも大きな第2ピッチで配置された第1ソース配線及び第2ソース配線と、前記第2ゲート配線及び前記第1ソース配線と電気的に接続されたスイッチング素子と、前記第1ゲート配線及び前記第2ゲート配線と前記第1ソース配線及び前記第2ソース配線とで囲まれた画素電極であって、第2方向に沿って延出した主画素電極及び第2方向に沿って延出するとともに前記スイッチング素子とコンタクトするコンタクト部を備えた画素電極と、を備えた第1基板と、前記主画素電極と前記コンタクト部との間に位置し第2方向に沿って延出した主共通電極を備えた共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】第1方向に延出した第1ゲート配線及び第2ゲート配線と第2方向に延出した第1ソース配線及び第2ソース配線とで囲まれスイッチング素子とコンタクトするコンタクト位置よりも第1ゲート配線側に位置し第1方向に延出した第1主画素電極及びコンタクト位置よりも第2ゲート配線側に位置し第1方向に延出した第2主画素電極を備えコンタクト位置から第1主画素電極までの第2方向に沿った距離とコンタクト位置から第2主画素電極までの第2方向に沿った距離とが同一である画素電極を備えた第1基板と、コンタクト位置、第1ゲート配線、及び、第2ゲート配線のそれぞれの上方を通り第1方向に延出した主共通電極を備えた第2基板と、第1基板と第2基板との間に保持された液晶分子を含む液晶層と、を備えた液晶表示装置。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

液晶装置、液晶装置の製造方法、電子機器

【課題】液晶層中の不純物の偏在に起因する表示不具合が改善された液晶装置、液晶装置の製造方法、この液晶装置を備えた電子機器を提供すること。

【解決手段】本適用例の液晶装置は、基板としての素子基板10上にトランジスターとしてのTFT30と、画素電極15と、画素電極15をTFT30の半導体層30aにおける第2ソース・ドレイン領域30dに電気的に接続させる柱状のコンタクト部CNT4とを有し、コンタクト部CNT4は、画素電極15の液晶層側の表面において突出部15aを形成している。

(もっと読む)

液晶表示装置

【課題】 液晶表示装置における各画素の開口率を高くする。

【解決手段】アクティブマトリクス型の液晶表示パネルを有する液晶表示装置であって、1本の走査信号線を挟んで隣接する2つの画素のTFT素子は、それぞれ、ゲートが当該1本の走査信号線に接続しており、かつ、ソースまたはドレインのうちの一方が異なる映像信号線に接続しており、隣接する2本の走査信号線の間には、当該2本の走査信号線のうちの一方の走査信号線にゲートが接続している前記TFT素子を有する画素と、当該2本の走査信号線のうちの他方の走査信号線にゲートが接続している前記TFT素子を有する画素とが、前記映像信号線の延在方向に沿って並んでおり、かつ、当該2つのTFT素子のソースまたはドレインのうちの一方が異なる映像信号線に接続している液晶表示装置。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

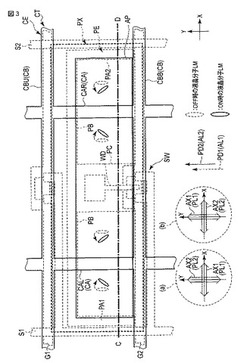

【解決手段】第1方向に延出した第1ゲート配線G1及び第2ゲート配線G2と、第2方向に延出した第1ソース配線S1及び第2ソース配線S2と、第1ゲート配線及び第2ゲート配線と第1ソース配線及び第2ソース配線とで囲まれた内側に位置する画素電極PEであって第1ゲート配線及び第1ソース配線と接続されたスイッチング素子とコンタクトするコンタクト部、コンタクト部から第1方向に延出した2本以上の主画素電極PA、及び、第2方向に延出し主画素電極を接続する接続部を備えた画素電極とを備えた第1基板と、第1ゲート配線と第2ゲート配線の上方、及び主画素電極間に位置し第1方向に延出した主共通電極CAと、第1ソース配線と第2ソース配線の上方に位置し第2方向に延出した副共通電極CBとを備えた共通電極を備えた第2基板とを備えた液晶表示装置。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を抑制することが可能な液晶表示装置を提供する。

【解決手段】 直線的に延出した帯状の主画素電極を備えた画素電極と、前記画素電極を覆うとともに前記主画素電極の延出方向と略平行な第1配向処理方向に配向処理された第1配向膜と、を備えた第1基板と、前記主画素電極を挟んだ両側で前記主画素電極の延出方向と略平行な方向に沿って延出した主共通電極及び第1配向処理方向の上流側に位置する前記主画素電極の一端部側において前記主画素電極の延出方向に交差する方向に沿って延出した副共通電極を備えた共通電極と、前記共通電極を覆うとともに第1配向処理方向と同一方向である第2配向処理方向に配向処理された第2配向膜と、を備えた第2基板と、前記第1基板と前記第2基板との間に保持された液晶分子を含む液晶層と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

半導体装置

【課題】1画素に複数の副画素を設けることにより視野角特性を向上させた表示装置を提

供することを課題とする。又は、複数の副画素を設けた場合であっても開口率の低下を抑

制する表示装置を提供することを課題とする。

【解決手段】第1の副画素、第2の副画素及び第3の副画素を有する画素と、走査線と、

信号線と、第1の容量配線と、第2の容量配線と、第3の容量配線とを設け、第1の副画

素〜第3の副画素にそれぞれ、第1の容量素子〜第3の容量素子の一方の電極及び第1の

容量配線〜第3の容量配線に電気的に接続する画素電極とを設け、第1の容量配線及び第

2の容量配線の電位を変化させ、第3の容量配線の電位を概略一定に保持する構成とする

。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】第1方向に沿って延出したゲート配線と、第1方向に交差する第2方向に沿って延出したソース配線と、第1方向に沿った長さが第2方向に沿った長さよりも長い画素に配置され第1方向に沿って延出した主画素電極を備えた画素電極と、を備えた第1基板と、前記主画素電極を挟んだ両側で第1方向に沿ってそれぞれ延出した主共通電極を備えた共通電極を備えた第2基板と、前記第1基板と前記第2基板との間に保持された液晶分子を含む液晶層と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

アクティブマトリックス型表示素子およびその製造方法

【課題】少ない工程数でアクティブマトリクス表示素子を形成する。

【解決手段】実施形態にかかるアクティブマトリックス型表示素子の製造方法は、絶縁基板上にゲート電極層、第1の絶縁膜、酸化物半導体層、第2の絶縁膜、酸化物半導体層と電気的に接続したソース・ドレイン電極を順に形成する工程を含む。酸化物半導体層は、ソース・ドレイン電極が形成される領域から画素領域にわたって形成され、第2の絶縁膜を形成する前に、酸化物半導体の画素領域に相当する部分を低抵抗処理して第1の画素電極を形成する。

(もっと読む)

液晶表示装置および液晶表示装置の製造方法

【課題】表示品位の劣化を抑制することが可能な液晶表示装置を提供する。

【解決手段】第1方向に沿った長さが第1方向に交差する第2方向に沿った長さよりも短い画素に配置されるとともに、第2方向に沿って延出した主画素電極及び第1方向に沿って延出し主画素電極と電気的に接続された副画素電極を有する画素電極を備えた第1基板10と、主画素電極を挟んだ両側で主画素電極と略平行に延出した主共通電極及び副画素電極を挟んだ両側で副画素電極と略平行に延出し主共通電極と電気的に接続された副共通電極を有する共通電極を備えた第2基板と、第1基板10と第2基板との間に保持された液晶分子を含む液晶層と、を備え、主画素電極と主共通電極との第1方向に沿った水平電極間距離は、主画素電極と主共通電極との第1方向及び第2方向に直交する第3方向に沿った垂直電極間距離よりも大きいことを特徴とする液晶表示装置。

(もっと読む)

半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】非選択期間において、出力信号のノイズが小さく、且つトランジスタの特性劣化を抑制できる液晶表示装置の駆動回路を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを設け、第1のトランジスタにおいて、第1端子を第1の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第5の配線に接続し、第2のトランジスタにおいて第1端子を第3の配線に接続し、第2端子を第6の配線に接続し、第3のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第4の配線に接続し、第4のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第6の配線に接続し、ゲート端子を第4の配線に接続する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

液晶表示装置

【課題】FFS方式を代表とする横電界方式の液晶表示装置において、液晶材料にかかる

電界を十分にすることを課題とする。

【解決手段】横電界方式において、1組の電極ではなく、複数組の電極を用いて、共通電

極直上や画素電極直上にある液晶材料に電界をかける。1組の電極は、櫛歯状に設けられ

た共通電極と、櫛歯状に設けられた画素電極との組である。その他の組の電極は、画素部

に設けられた共通電極と、該櫛歯状に設けられた画素電極との組である。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす、適切な構成を備えた保護回路等を提供する。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

液晶表示装置

【課題】プーリングの発生し難い液晶表示装置を提供する。

【解決手段】液晶表示装置は、液晶表示パネルと、センシング基板と、液晶表示パネル及びセンシング基板を接合する接着材と、を備える。液晶表示パネルは、画素電極PEを有した第1基板と、共通電極CEを有した第2基板と、液晶層と、表示領域と、画素電極及び共通電極で形成された画素PXと、を具備している。画素電極PEは第2方向Yに長手方向を持つ主画素電極PAを有する。共通電極CEは第1方向Xに主画素電極PAを挟んで位置し第2方向Yに長手方向を持つ一対の主共通電極CAを有する。

(もっと読む)

液晶表示装置

【課題】信頼性の高い液晶表示装置を提供する。

【解決手段】マトリクス状に配置された複数の画素電極PEと、画素電極PEが配列する行に沿って延びるゲート配線Gと、列に沿って延びるソース配線Sと、複数の画素電極PEが配置された領域ACTの周囲の領域において画素電極PEと同層に配置されゲート配線に印加されるト電位が供給される電極EBと、を備えた第1基板ARと、複数の画素電極PEが配置された領域ACTおよび周囲の領域と対向した共通電極CEを備え第1基板ARと対向して配置された第2基板CTと、第1基板ARと第2基板CTとの間に挟持された液晶層LQと、を備え、共通電極CTは、少なくとも電極EBの端部と対向する部分に電極除去部CEAを備える液晶表示装置。

(もっと読む)

液晶表示装置

【課題】表示品位を劣化することなく、種々の解像度に対応することを可能とする。

【解決手段】 第1方向に沿って間隔をおいて配置され第1方向に交差する第2方向に沿ってそれぞれ延出した2本の信号配線と、前記信号配線の間に配置された2本以上の第1主電極を備えた第1電極と、を備えた第1基板と、前記信号配線の上方、及び、前記第1主電極間にそれぞれ配置されるとともに前記第1主電極の延出方向と略平行な方向に沿って延出した第2主電極を備えた第2電極を備えた第2基板と、前記第1基板と前記第2基板との間に保持された液晶分子を含む液晶層と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

61 - 80 / 1,655

[ Back to top ]