Fターム[2H092NA14]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 安定化 (3,125) | 静電破壊防止 (416)

Fターム[2H092NA14]に分類される特許

41 - 60 / 416

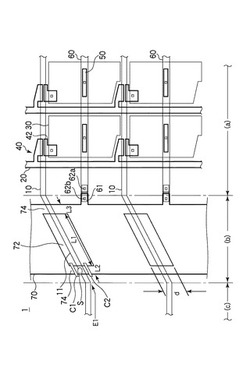

表示装置用基板及びそれを用いた液晶表示装置

【課題】本発明は、静電気流入による層間短絡などの障害が生じたとしても容易に修復することのできる表示装置用基板を提供することを目的とする。

【解決手段】基板1上の表示領域内に配設され、表示領域の内方より表示領域の外方に向けて引き出し形成される第1の配線部10を有する。さらに、基板1上の表示領域の外の第1の配線部10と絶縁膜を介して交差して形成される第2の配線部70を有する。さらに、第2の配線部70に形成され、少なくとも交差する第1の配線部10と重なり合う領域に開口した開口部72を有する。さらに、開口部72の両端に形成され、絶縁膜を介して第1及び第2の配線部10、70が重なり合う重畳部74を有する。

(もっと読む)

電気光学装置の製造方法および電気光学装置

【課題】誘電体層に高誘電率絶縁膜を用い、高誘電率絶縁膜等のエッチングにドライエッチングを採用した場合でも、静電破壊の発生を防止することができる電気光学装置の製造方法、および当該方法により製造した電気光学装置を提供すること。

【解決手段】液晶装置100を製造するにあたって、高誘電率絶縁膜形成工程および高誘電率絶縁膜パターニング工程によって誘電体層42aを所定領域に形成した後、第2電極形成用導電膜形成工程および第2電極形成用導電膜パターニング工程によって容量線5b(第2電極)を形成する。このため、高誘電率絶縁膜42は、広い領域にわたって形成された状態でドライエッチング時のプラズマを受けるのは、高誘電率絶縁膜パターニング工程の間だけであり、第2電極形成用導電膜パターニング工程を行う時点では、すでにパターニングされている。

(もっと読む)

画素アレイおよびそれを有するディスプレイパネル

【課題】画素構造の開口率を増やすことのできる画素アレイおよびそれを有するディスプレイパネルを提供する。

【解決手段】複数の画素構造を含む画素アレイを提供する。画素構造のうち少なくとも1つは、スキャンラインと、データラインと、能動素子と、画素電極と、読み出しラインと、EMI遮蔽層と、検出装置とを有する。スキャンラインおよびデータラインは、基板の上に配置される。能動素子は、スキャンラインおよびデータラインに電気接続される。画素電極は、能動素子に電気接続される。読み出しラインは、データラインの上方または下方に配置される。EMI遮蔽層は、データラインを覆い、読み出しラインとデータラインの間に位置する。検出装置は、スキャンラインおよび読み出しラインに電気接続される。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、データ線に電気的に接続された付加容量の破損を防止する。

【解決手段】電気光学装置は、対向配置され、シール材(52)で囲まれた領域に電気光学物質(50)を挟持する第1基板(10)及び第2基板(20)と、第1基板上の画素領域(10a)に走査線(11)とデータ線(6)との交差に対応して設けられた画素電極(9)と、画素電極と、走査線及びデータ線との間に、画素電極に容量絶縁膜(72)を介して対向するように設けられた蓄積容量電極(71)と、画素電極と同一層からなる第1容量電極(610)と、蓄積容量電極と同一層からなる第2容量電極(620)とを有し、データ線と電気的に接続された付加容量(600)とを備える。付加容量は、画素領域と、シール材で囲まれた領域の外周よりも内側との間の領域に配置されている。

(もっと読む)

表示装置

【課題】簡易な構成で配線間の静電破壊を防ぐこと。

【解決手段】表示装置は、絶縁基板と、前記絶縁基板の上に第1の信号線と第2の信号線とが形成された第1の導電層と、前記第1の導電層の上層に設けられた絶縁層と、前記絶縁層の上層に設けられ、前記第1の信号線および第2の信号線と平面的に重なる半導体膜が形成された半導体層と、を含む。

(もっと読む)

液晶パネル、TFTアレイ基板及びその製造方法

【課題】液晶パネル、TFTアレイ基板及びその製造方法を提供する。

【解決手段】本発明は、液晶パネル、TFTアレイ基板及びその製造方法に関する。ベース基板と、前記ベース基板上に形成されたゲート走査線と、データ走査線と、前記ゲート走査線および前記データ走査線を上から覆う保護層とを備えるTFTアレイ基板であって、前記保護層における封止剤を塗布した領域の、ゲート走査線と/またはデータ走査線に対応する位置に、導電層が設けられる。前記導電層は、当該TFTアレイ基板における封止剤の外部領域に延びるとともに、接地端に接続される。前記導電層を形成する材料としては、透明導電材料を有する。

(もっと読む)

液晶表示装置

【課題】 上透明基板の表面に形成された保護用電極と下透明基板の配線電極を、液晶パネルの側面に設けた導電材で電気的に接続した液晶表示装置について、基板の破損や導電材の接続状態を容易にチェック可能な構成とする。

【解決手段】 液晶パネルを構成する上透明基板1の外表面に設けられた保護用電極3を設け、下透明基板2に、画素電極に信号を供給する複数の配線8と、この複数の配線のうち両端の配線より外形側に形成された放電用第一配線5及び放電用第二配線6と、外部の回路と電気的に接続するための端子電極を設けた。このとき、放電用第一配線5及び放電用第二配線6と保護用電極3を電気的に接続するために、シール材9の外側の上透明基板1と下透明基板2の内表面の間から上透明基板1の端面にかけて導電材4を設けることとした。

(もっと読む)

ディスプレイパネル及びマザーパネル並びにディスプレイパネルの製造方法

【課題】パネルの製造中において配線の腐食・劣化・電蝕等を抑えるとともに、パネルの製造後でもパネルの各素子を静電気から保護する。

【解決手段】ディスプレイパネル1は、基板10と、基板10の表側に発光素子8とトランジスタ5,6とを有する画素Pixが配列されている表示領域30と、表示領域30内に設けられているとともに、表示領域30の外側に引き回された複数の配線52,53,54,55と、表示領域30の外側で基板10の表側に設けられ、配線52,53,54,55にそれぞれ接続された保護素子72,73,74,75と、表示領域30の外側で基板10の表側に設けられ、保護素子72,73,74,75に接続され、基板10の縁まで至る引出し配線80と、を備える。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

表示装置

【課題】 静電気放電対策用の新たな部品を用いることなく、ドライバに伝搬する静電気放電ノイズを低減することができる表示装置を提供する。

【解決手段】 第1接地配線21は、フレキシブル回路基板13の配列方向のドライバ14の両側にそれぞれが形成され、ドライバ14と第1共通電極電圧配線15aとの間の領域に、第1共通電極電圧配線15aに近接して平行に、プリント回路基板12側から直線状に形成される。第2接地配線22は、第1共通電極電圧配線15aとフレキシブル回路基板13の周縁との間の領域、および第2共通電極電圧配線15bと表示パネル11の周縁との間の領域に形成され、共通電極電圧配線15と近接して平行に形成される。第1接地配線21および第2接地配線22は、プリント回路基板12に形成される接地電位部に電気的に接続される。

(もっと読む)

液晶表示装置用基板、液晶表示装置及びその製造方法

【課題】静電気の荷電量に関係なしに静電気から液晶表示基板を保護することにある。

【解決手段】画像を表示する多数の画素電極と半導体素子とを有している透明な絶縁の第1基板と、前記第1基板上に形成され前記半導体素子と連結された配線と、隣接した前記配線との間に連結され、前記第1基板から発生される静電気を消耗させる多数のスパーク誘導回路とを含む。

(もっと読む)

マザーボード及びアレイ基板の製造方法

【課題】マザーボード及びアレイ基板の製造方法に関する。

【解決手段】マザーボード及びその製造方法であって、該マザーボードは、少なくとも一つの表示領域及び上記表示領域の周辺のプレカッティング領域を有する基板を備え、上記表示領域はゲートスキャンライン及びデータスキャンラインを有し、上記プレカッティング領域は電気的に接続されているゲートライン連通線とデータ連通線を有し、上記ゲートライン連通線は上記表示領域におけるゲートスキャンラインごとと電気的に接続し、上記データ連通線は上記表示領域におけるデータスキャンラインごとと電気的に接続する。

(もっと読む)

液晶表示装置

【課題】静電気を逃がす金属部品2の薄型、及び小型化を達成し、かつ金属部品2の組付けが容易な液晶表示装置を提供する。

【解決手段】文字板62の開口部62aの奥に取付けられた液晶パネル本体1内の透明導電膜15が金属部品2によって接地される液晶表示装置において、表ガラス3と裏ガラス4の間に液晶層5が封入され、表ガラス3の表面と裏ガラス4の裏面に表側偏光板6と裏面偏光板7が設けられている。表ガラス3と表側偏光板6との端面の位置ずれによって形成された端面のずれ部14に位置し、表ガラス3と表側偏光板6との間に形成された透明導電膜15から引き出された露出部15aを備える。この露出部15aに接触する鋏み込み形状部23a、23b、24a、24bによって透明導電膜15がフレキシブルプリント基板10を介して回路基板32内のアースに接続される。

(もっと読む)

液晶表示装置

【課題】外部接続する電位と、液晶の駆動波形の平均電位との間に相違がある構成であっても、表示不良の発生を抑制することのできる液晶表示装置を提供する。

【解決手段】液晶表示装置は、互いに対向する一対の基板と、一対の基板の間に挟持された液晶層と、液晶層を介して互いに対向する一対の電極と、一対の電極のそれぞれに接続する駆動回路と、一対の基板の一方で液晶層の側とは反対の側に設けられた外部電極とを備える。外部電極は、コンデンサを介してグラウンドに接続する。コンデンサの容量は、一対の電極と外部電極との間の静電容量以上であることが好ましい。

(もっと読む)

液晶表示装置の製造方法

【課題】配線破断を軽減する構造を有する液晶表示装置の製造方法を提供する。

【解決手段】基板上にゲート配線及び信号配線、ゲート絶縁膜、半導体パターン、データ配線、保護膜、ドレーン電極を露出させる第1接触孔及び信号配線を露出させ、側辺の長さが幅より大きく形成される複数の第2接触孔、第1及び第2接触孔を通じてドレーン電極に連結される画素電極及び信号配線に連結される信号配線補助パッドを形成する液晶表示装置の製造方法であって、信号配線を形成する段階では、信号配線に一対一に対応する複数の信号リードを有する信号伝送用フィルムを含み、信号伝送用フィルムには複数の信号リードのうちの高電圧信号を伝送する第1信号リードと低電圧信号を伝送する第2信号リードとの間にダミーリードが形成され、ダミーリードに対応するダミー配線が基板に形成され、ダミー配線は信号配線より酸化傾向が小さい特性を有する導電物質で形成される。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、高い信頼性を実現する。

【解決手段】電気光学装置は、画素電極(9a)と、画素電極に対応して設けられたトランジスター(30)と、トランジスターと電気的に接続されたデータ線(6a)と、画素電極及びトランジスター間に設けられ、第1電極(72)及び第2電極(71)が容量絶縁膜(75)を介して対向配置されることで形成される蓄積容量(70)と、第1電極と同一層に設けられた第1付加容量電極(401)と、第1電極及び第2電極とは異なる層に設けられた第2付加容量電極(402)とが、付加容量絶縁膜(42)を介して対向配置されることで形成され、データ線と電気的に接続された付加容量(400)とを備える。

(もっと読む)

電子装置

【課題】複数のスイッチング素子が配置された領域の周辺部の切断を行う必要がないと共に、周辺部に保護素子を設ける必要がない静電対策手段を備える電子装置を提供する。

【解決手段】複数の走査線14と、複数の走査線14と交差する複数の信号線12と、複数の走査線14と複数の信号線12の交差点16に対応してそれぞれ設けられた複数のスイッチング素子40と、複数のスイッチング素子40が配置されたスイッチング素子配置領域20の外側で、複数の走査線14と複数の信号線12とに接続された共通接続部材10であって、固有抵抗値が可変な材料から成る共通接続部材10と、を備える。

(もっと読む)

液晶表示装置の製造方法

【課題】外部接続する電位と、液晶の駆動波形の平均電位との間に相違がある構成であっても、表示不良の発生を抑制することのできる液晶表示装置の製造方法を提供する。

【解決手段】液晶表示装置は、互いに対向する一対の基板と、一対の基板の間に挟持された液晶層と、液晶層を介して互いに対向する一対の電極と、一対の電極と液晶層との間にそれぞれ設けられた一対の配向膜と、一対の基板の一方で液晶層の側とは反対の側に設けられた外部電極とを備える。一対の基板をシール材を介して所定の間隔で貼り合わせた後、加湿処理を行ってから、一対の基板およびシール材で包囲された空間内に液晶材料を注入する。加湿処理は、25℃以上の温度であって85%以上の相対湿度で行うことが好ましい。

(もっと読む)

液晶装置、その製造方法、および、電子機器

【課題】MOS−FETアレイ回路の損傷を防止でき、製品の歩留まりを向上できる反射型液晶パネルを提供する。

【解決手段】一面にMOS−FETアレイ回路およびこのMOS−FETアレイ回路上配置された反射電極の延在部317B(導通部319)を含む表示素子部317が設けられた素子基板と、この素子基板の一面に対向配置され、素子基板の一面に対向する対向面に透明電極が形成された対向基板と、素子基板と対向基板との間に、表示素子部317を囲んで環状に設けられたシール材340と、このシール材340で囲まれた領域内に封入された液晶と、を備え、素子基板の外周縁の位置においては、シール材340がMOS−FETアレイ回路が積層する延在部317B(導通部319)に積層しない。

(もっと読む)

液晶装置の製造方法、液晶装置、および、液晶装置を備えた電子機器

【課題】簡単な構成で放電による回路構成の損傷を防止できる反射型液晶パネルの製造方法を提供する。

【解決手段】MOS−FETアレイ回路および画素電極が積層された積層領域317Cを含む表示素子部317が一面に複数配列形成され、隣り合う周縁電極317Bが離間する素子側マザー基板と、この素子側マザー基板の一面に対向配置され、素子側マザー基板の一面に対向する対向面に透明電極が設けられた対向側マザー基板と、を用い、素子側マザー基板の周縁電極317Bは、外周縁から隣接する他の周縁電極317Bに向けて突出し先端に向けて幅狭となる放電誘発部317Eを有する。

(もっと読む)

41 - 60 / 416

[ Back to top ]