Fターム[3C081CA27]の内容

Fターム[3C081CA27]の下位に属するFターム

スパッタリング (222)

Fターム[3C081CA27]に分類される特許

81 - 100 / 107

MEMSスイッチおよびこれを備えた集積回路

【課題】小型が図れ、大容量の電流をオン/オフ可能な磁気駆動によるMEMSスイッチ及びこれを備えた集積回路を提供する。

【解決手段】シリコン基板1にMEMS(Micro Electro Mechanical System)技術により支持部2が立設され、支持部2の先端面には、シリコン基板1の表面に平行させて板状の磁性体3が設けられている。磁性体3の一端の内側には第1の接点4が設けられ、これに対向させてシリコン基板1上には第2の接点6が設けられている。シリコン基板1側から磁性体3に磁力が付与されると、吸引されて撓み、第1の接点4が第2の接点6に接触し、スイッチオンになり、磁力が消滅すると磁性体3は待機位置に復帰する。

(もっと読む)

光偏向器および光学装置

【課題】大きな偏向角および大振幅動作が得られ、また、小型化、薄型化、および軽量化を図ることができる光偏向器を提供すること。

【解決手段】反射板1を弾性支持部2a,2bを中心に回転振動させる圧電ユニモルフ振動体210a〜210dを備えた光偏向器であって、圧電ユニモルフ振動体210a〜210dの振動板23a〜23dの両端の一方を弾性支持部2a,2bに接続するとともに、両端のもう一方を支持体9に接続し、振動板23a〜23d、反射板1、弾性支持部2a,2b、支持体9を一体に形成し、圧電ユニモルフ振動体210a〜210dが、それぞれ複数の並列振動板23a−1〜3,23b−1〜3,23c−1〜3,23d−1〜3および並列アクチュエータ28a−1〜3,28b−1〜3,28c−1〜3,28d−1〜3を備えていることを特徴とする光偏向器とした。

(もっと読む)

キャビティの上の層の平面化

【課題】ミラー面を有するマイクロデバイスの製造方法を提供すること。

【解決手段】マイクロ構造を製造する方法であって、下層に形成されたへこみの中に犠牲材料を配置することと、該へこみの中の該犠牲材料上に補償材料の層を形成することと、該補償材料の第1の部分を除去することによって、該犠牲材料上に実質的に平らな表面を形成することであって、該実質的に平らな表面は、実質的に該下層の該上面と共平面であることと、該下層上に上層を形成し、実質的に平らな表面に形成することとを包含する、方法。

(もっと読む)

RFデバイス

【課題】選択可能なキャパシタンスを有するRFデバイス提供すること。

【解決手段】RFデバイスであって、RF信号を搬送するための第1の導体と、前記第1の導体から所定の間隔をもたせて配置された変形可能膜であって、前記RF信号を選択的にフィルタリングするように構成されておりさらに前記RF信号を選択的にフィルタリングするための少なくとも3つの個別の作動可能な位置を有する変形可能膜と、を具備する。

(もっと読む)

マイクロデバイスのパッケージング

【課題】アンチスティクション材料をマイクロデバイスに適用するための方法、ならびにアンチスティクション材料を適用されたマイクロメカニカルデバイスを提供すること。

【解決手段】マイクロデバイスにアンチスティクション材料を適用する方法であって、マイクロデバイスをチャンバ内に封じ込めることと、コンテナ内でアンチスティクション材料を蒸発させ、蒸発したアンチスティクション材料を形成することと、該チャンバと流体連通する入口を介することにより、該コンテナから該封じ込められたチャンバの中に、該蒸発したアンチスティクション材料を移送することと、該蒸発したアンチスティクション材料を該マイクロデバイスの表面上に堆積させることとを包含する、方法。

(もっと読む)

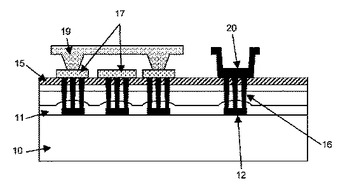

モノリシックIC及びMEMSマイクロ加工方法

高応力窒化シリコンがメカニカル材料として使用され、アモルファスシリコンが犠牲層として機能する、モノリシックIC/MEMSプロセスが開示される。電子回路及びマイクロ電子機械デバイスは、単一ウェーハの別個の区域に構築される。IC及びMEMSプロセスステップの順序は、後続の高プロセス温度による、半製品回路及びデバイスの変化を回避するように設計される。 (もっと読む)

MEMSデバイスおよびその製造方法

【課題】構造体の機械的な特性を保持しながら電気的な抵抗値を軽減し、優れた動作特性を有するMEMSデバイス、およびその製造方法を提供する。

【解決手段】シリコン基板1上に形成された多結晶シリコンからなる固定電極10と、シリコン基板1上に形成された窒化膜3と隙間を設けて機械的に可動な状態で配置された多結晶シリコンからなる可動電極20と、可動電極20の周囲に形成され且つ固定電極10の一部を覆うように形成された第1層間絶縁膜13、第1配線層23、第2層間絶縁膜14、第2配線層24、および保護膜19がこの順に積層された配線積層部と、を有し、固定電極10の前記配線積層部に覆われた部分がシリサイド化されてシリサイド部分25が形成されている。

(もっと読む)

MEMSデバイスおよびその製造方法

【課題】構造体の機械的な特性を保持しながら電気的な抵抗値を軽減し、優れた動作特性を有するMEMSデバイス、およびその製造方法を提供する。

【解決手段】シリコン基板41上に形成されたシリコンからなる固定電極50と、シリコン基板41上に形成された窒化膜43と隙間を設けて機械的に可動な状態で配置されたシリコンからなる可動電極60と、可動電極60の周囲に形成され且つ固定電極50の一部を覆うように形成された第1層間絶縁膜52、第1配線層63、第2層間絶縁膜53、第2配線層64、および保護膜59がこの順に積層された配線積層部と、を有している。可動電極60は、タングステンまたはモリブデンなどの高融点金属によりシリサイド化されてシリサイド部分65が形成されている。

(もっと読む)

マイクロマシンデバイスの製造方法

本発明は、電気回路を含む基板(10)の上に、少なくとも1つのマイクロマシン構造を含むマイクロマシンデバイスを、下方の電気回路に影響を与えることなく作製する方法を提供する。この方法は、電気回路を含む基板(10)の上に、保護層(15)を形成する工程と、少なくとも1つのマイクロマシン構造を形成するための複数のパターニングされた層を保護層(15)の上に形成する工程であって、複数のパターニングされた層は、少なくとも1つの犠牲層(18)を含む工程と、その後に、犠牲層(18)の少なくとも一部を除去して、少なくとも1つのマイクロマシン構造を開放する工程とを含む。この方法は、更に、保護層(15)を形成する前に、マイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板(10)をアニールする工程を含み、アニールは、その後の製造工程中に、保護層(15)の下での気体の形成を防止する。本発明は、また、本発明の具体例にかかる方法で得られたマイクロマシンデバイスを提供する。  (もっと読む)

(もっと読む)

センサの製造方法、レゾネータの製造方法

【課題】高い生産性を実現することのできるセンサの製造方法等を提供することを目的とする。

【解決手段】ディスク状の振動子と、振動子の外周部にギャップを隔てて配置された駆動電極、検出電極と、を備えたセンサの製造にあたり、振動子と駆動電極、検出電極とのギャップ部分を、電子線照射によりパターン形成する第一のパターン形成工程と、振動子と駆動電極、検出電極とのギャップ部分以外の部分を、ステッパによりパターン形成する第二のパターン形成工程と、を含むようにした。電子線照射によるパターン形成を行うためのアライメントマークMは、活性Si層53を貫通することのないように形成し、ボックス層52におけるチャージアップを防ぐようにした。

(もっと読む)

マイクロアクチュエータのコイル製造方法

【課題】マイクロアクチュエータのコイル製造方法を提供する。

【解決手段】基板100を準備する工程、基板100の上側にコイルを形成するための複数のトレンチ112を形成する工程、基板100の上側の複数のトレンチ112を除いた残余部分を遮蔽剤120で覆う工程、複数のトレンチ112に導電性物質130を電気メッキする工程、及び基板100上にパッシベーション層を形成する工程を含むマイクロアクチュエータのコイル製造方法である。これにより、ウェーハの反りを最小化してコイルの断面積の変化を減らすことによって、コイル駆動に印加される駆動電流及び消費電力を減少させうる。

(もっと読む)

電気的機械的メモリ素子及びその製造方法

【課題】 高い信頼性及び優秀な動作特性を有するメモリ素子及びその製造方法を提供する。

【解決手段】 メモリ素子は、基板100と、基板100に対して垂直方向に延長される第1電極110と、基板100に対して垂直する方向に延長され、電極のギャップによって第1電極110と互いに離隔するように配置される第2電極120と有する。さらに、前記電極ギャップの内部に垂直方向に延長され、第1ギャップ118Aだけ第1電極110から離隔され、第2ギャップ118Bだけ第2電極120から離隔され、静電気的に変形されることが可能であって、第1曲げ状態では、第1ギャップ118Aを通じて第1電極110と電気的に接続されるようにし、第2曲げ状態では第2ギャップ118Bを通じて第2電極120と電気的に接続されるようにし、待機状態では第1電極110及び第2電極120と互いに電気的に絶縁されるようにする第3電極とを含む。

(もっと読む)

可変光減衰器アレイ

【課題】レンズアレイとスペーサと回転駆動鏡アレイと、駆動電極アレイを集積化して小型化を図る。

【解決手段】入力用光ファイバ群31と、出力用光ファイバ群32と、サーキュレータ34と、スペーサ37,38と、レンズアレイ35と、MEMSミラーアレイ36と、MEMS電極39を一体化してアレイ化した構成とする。

(もっと読む)

可視スペクトルモジュレーターアレイ

【課題】非金属の変形自在の干渉型変調素子を製造する。

【解決手段】各変形自在素子は変形機構と光学的部分を有し、それぞれ制御された変形特性と制御された変調特性とを独立して素子に与える。変形自在の変調素子は非金属である。素子は、最終の共振器寸法と関係がある層厚を有している犠牲層と犠牲層をそれら間にてサンドウィッチする2つの層を形成し、化学薬品(例えば、水)を使い又はプラズマに基づいた処理を行い犠牲層を除去することによって形成される。各変調素子は引張応力下で保持される変形自在部分を有し、制御回路は変形された部分の変形を制御する。

(もっと読む)

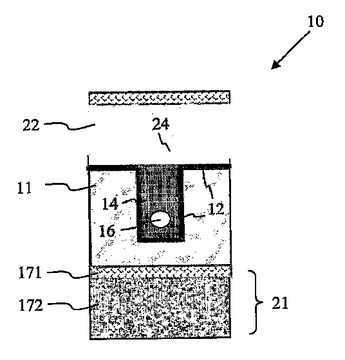

透明なマイクロ流体デバイス

生物学的実体の状況を分析するデバイス。デバイス(10)は、少なくとも2つの対向側方壁とベース壁とによって凹部が内部に画定されたほぼ透明なベース基板(11)と、凹部を占める少なくとも一部を有するほぼ透明な充填部材(14)と、充填部材とベース基板の間に配置されたほぼ透明な分離層(12)と、充填部材に画定されたチャネル(16)とを備え、チャネルは、充填部材の第1側方壁の上に配置された入口と、充填部材の第2側方壁の上に配置された出口とを備えている。充填部材の第1側方壁は、充填部材の第2側方壁と対向する関係で配置され、充填部材の第1側方壁および第2側方壁の少なくとも一部は、凹部を画定する対向側方壁に対して少なくともほぼ垂直である。  (もっと読む)

(もっと読む)

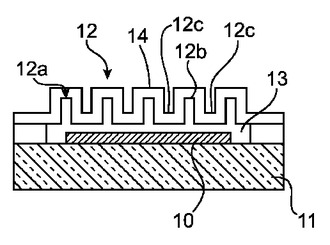

高められた機械的抵抗を有するキャップによって区切られた空洞を備えた超小型構成体

本発明は、基板(11)によって支持された動作部分(10)を囲むキャップ(12)によって仕切られたキャビティ(13)を備えた超小型構成体から成る。キャップ(13)は、少なくとも1つの突出した補剛部材(12b)を有する帆号手段を備えている。突出した補剛部材(12b)は、頂部壁(12a)の2つの凹状領域(12c)の間に配置されており、基板(11)に接触することなく、凹状領域(12c)から離隔した端部(14)を有している。  (もっと読む)

(もっと読む)

材料付着法によるマイクログリッパの製造方法

ベース体及びベース体と一体的に接続された把持体を含んでおり、この把持体が、ベース体から突き出ており、且つ自由端部領域では収容スリット(6)を、マイクロメートル又はサブマイクロメートルのスケールの対象物を収容スリット内に把持及び保持のために挟み得るように設けられたマイクログリッパ(8)の製造方法、並びに属概念のマイクログリッパを説明する。本発明は、ベース体及び把持体が、材料付着法によって少なくとも一つの共通の第1の材料層及び一つの共通の第2の材料層(3、4)を形成することで製造されること、並びに材料層が、基本的に平らに形成され、且つ平らな基体表面を準備する方法ステップと、基体表面上に第1の犠牲層(13)を付着する方法ステップと、第1の犠牲層(13)上に第1の材料層(3)を付着する方法ステップと、第1の材料層(3)上、少なくとも第1の材料層の一つの局所的な領域上に第2の犠牲層(14)を付着する方法ステップと、第1の材料層(3)及び第2の犠牲層(14)上に第2の材料層(4)を付着する方法ステップと、収容スリットを形成するため第2の犠牲層(14)を除去する方法ステップと、製造されたマイクログリッパを基体表面からはずすために第1の犠牲層(13)を除去する方法ステップと、を実施することで互いに接続されることを特徴とする。 (もっと読む)

犠牲材料を用いるマイクロデバイス作成方法

【課題】空間光変調器などに用いられるマイクロ構造を提供すること。

【解決手段】第一の高さを有する第一の構造部分と、該第一の高さより高い第二の高さを有する第二の構造部分とを備える基板を形成することと、該基板の上に、ポリアリーレン、水素シルセスキオキサンなどの第一の犠牲材料を堆積することであって、該犠牲材料は、該第一の構造部分を少なくともカバーする、ことと、該第一の犠牲材料の上に、第一の構造材料の層を堆積することと、該第一の構造材料の該層の中に、開口部を形成することであって、該開口部は、外側から該第一の構造材料の該層の下の該第一の犠牲材料へのアクセスを提供する、ことと、該第一の犠牲材料を除去して、該第二の構造部分と接続する第三の構造部分を形成することであって、該第三の構造部分の少なくとも一部は、該第一の構造部分の上にある、こととを包含する、マイクロ構造を作成する方法。

(もっと読む)

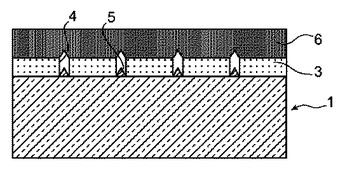

微細構造素子の面に開口したキャビティの保護方法

本発明は、関与部(5)を有しており、微細構造素子(1)の一つの面上で開口している少なくとも一つのキャビティ(4)の内部を保護するための方法に関している。ここで、前記微細構造素子は、前記面上で保護物質の非コンフォーマル層(6)の堆積を備えており、前記非コンフォーマル層は前記関与部を覆うことなくキャビティをふさぐ。本発明は、そのような微細構造素子を備えた素子を製造する方法にも関している。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス、及び不揮発性マイクロエレクトロメカニカルメモリセルを製造する方法。この方法は、原子層堆積法を用いて犠牲材料第1層を基板上に堆積させる第1の工程を有する。この方法の第2の工程は、犠牲材料第1層の少なくとも一部分上にカンチレバー(101)を設けることである。第3の工程は、原子層堆積法を用いて犠牲材料第2層を犠牲材料第1層上に、またカンチレバーの一部が犠牲材料によって囲まれるようにカンチレバーの一部の上に堆積させることである。第4の工程は、犠牲材料第2層の少なくとも一部分を覆う別材料層(107)を設けることである。最後に、最終工程は、カンチレバーを囲む犠牲材料をエッチングによって除去し、カンチレバーが内部に懸設されるキャビティ(102)を規定する工程である。 (もっと読む)

81 - 100 / 107

[ Back to top ]