Fターム[4E351DD41]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | 電気的活性材の材質と形態 (6,005) | 誘電体(絶縁体を含む) (221)

Fターム[4E351DD41]の下位に属するFターム

ペロブスカイト型構造のもの (105)

Ta2O5,MnO2 (12)

酸化硅素 (13)

粒界絶縁層を持つ誘電体

ガラス誘電体 (10)

有機物誘電体又は有機物を含む誘電体 (26)

Fターム[4E351DD41]に分類される特許

21 - 40 / 55

複合有機封入剤

本発明は、組成物、および特に電子デバイスの保護コーティングのためのかかる組成物の使用に関する。本発明は、複合封入剤で被覆され、かつプリント配線板に埋め込まれた箔上焼成セラミックコンデンサに関する。  (もっと読む)

(もっと読む)

プリント配線板および半導体パッケージ内部に埋め込むための別個の箔上形成薄膜コンデンサを形成する方法

【課題】プリント配線板または有機半導体パッケージ基板内部に埋め込むための別個の薄膜コンデンサを形成する方法を提供すること。

【解決手段】本発明は、セラミック誘電体が酸エッチング液と接触しないように、サンドブラストまたは他の手段によってコンデンサの選択部分を除去するステップを含む方法に関する。

(もっと読む)

プリント回路基板内蔵型キャパシタの製造方法

【課題】プリント回路基板内蔵型キャパシタの製造方法を提供する。

【解決手段】補強基材及びその両面に積層された銅箔からなるCCL基板を用意するステップと、前記CCL基板の銅箔表面を平坦化するステップと、前記平坦化された銅箔表面上に誘電層を形成するステップと、前記誘電層上に上部電極を形成するステップとを含む。

(もっと読む)

受動素子を備えた配線板の製造方法

【課題】改善された特性を有する受動素子を備えた配線板の製造方法を提供すること。

【解決手段】それぞれ第1の面および第2の面を有する第1および第2の金属箔の少なくともいずれか一方の第1の面に抵抗ペーストおよび/または誘電体ペーストを塗布する工程と、塗布された抵抗ペーストおよび/または誘電体ペーストの縁部を除去する工程と、第1の金属箔の第1の面に対向して熱可塑性かつ熱硬化性を有する絶縁板を配置し、かつ絶縁板の第1の金属箔が対向する面とは異なる面に対向して第2の金属箔の第1の面側を配置する工程と、これらの配置された第1の金属箔、絶縁板、および第2の金属箔の三者を積層加圧かつ加熱して一体化し両面配線板を形成する工程と、形成された両面配線板の第1の金属箔および/または第2の金属箔をパターニングする工程とを具備する

(もっと読む)

モノリシックセラミック素子および作製方法

ここで提案されるのは、多層構造を有する改善形のモノリシックセラミック素子であり、この素子は、作製時に横方向に最小限にしか変形しない。これは、機能性セラミックからなる機能層(F1,F2)の他に、誘電再結晶材料を含む少なくとも1つのテンション層(S)を有する多層構造によって達成される。このテンション層の相転移温度は、焼成温度よりも低く、再結晶化される構造が得られる。この構造は、機能層の焼成温度の間、固体状態に止まり、上記の多層構造を横方向に力を加えるため、焼成による縮みは、層面に対して垂直なZ軸方向にしか発生しない。  (もっと読む)

(もっと読む)

部分的にジルコニウム、スズまたはハフニウムによって置換されたチタニウムを有するチタン酸バリウム薄膜

【課題】高静電容量、低損失正接、および許容できる静電容量対温度特性を有する薄膜コンデンサ。

【解決手段】高誘電率(誘電定数)の、薄膜CSDチタン酸ベース誘電体組成物であって、チタンがジルコニウム、スズまたはハフニウムによって部分的に置換された組成物を提供すること。組成物は、X7R要求条件をより良く満足させる温度の関数としての静電容量を示す。

(もっと読む)

基板の配線構造

【課題】多層構造を持たない基板において、高周波信号の伝送品質を確保することが可能な基板の配線構造を提供することを目的とする。

【解決手段】複数の集積回路を搭載可能な基板の配線構造100において、集積回路間を接続するための信号配線150と、対向配置される第1電源層130および第2電源層140と、信号配線150に略並行に配されたリターン・パス用配線130a、140aとを備え、リターン・パス用配線130aの両終端を第1電源層(Vcc層)130に接続し、リターン・パス用配線140aの両終端を第2電源層(Gnd層)140に接続する。

(もっと読む)

薄膜キャパシタを内蔵した印刷回路基板の製造方法及びそれにより製造された印刷回路基板

【課題】薄膜キャパシタを内蔵した印刷回路基板の製造方法及びそれにより製造された印刷回路基板を提供する。

【解決手段】絶縁基材21a上に、無電解メッキで形成された部分23aと電解メッキで形成された部分23bを含む下部電極23を形成する工程と、上記下部電極上に低温成膜工程によって非晶質常誘電体膜25を形成する工程と、上記常誘電体膜上に無電解メッキ工程によって金属シード層27を形成する工程と、上記金属シード層上に電解メッキ工程を利用して上部電極29を形成する工程とを含み(上部電極29上に絶縁基板21bを設けてもよい)、薄膜キャパシタを内蔵した印刷回路基板の製造方法及びこの製造方法で製造された薄膜キャパシタを内蔵した印刷回路基板20である。

(もっと読む)

薄膜電子部品用基板及びそれを用いた薄膜電子部品並びにそれらの製造方法

【課題】本発明の目的は、数nm〜数μmの膜厚の薄膜を成膜する高精度の薄膜デバイス製造技術を適用しうる、高精度の平滑性を有するセラミックス多結晶基板やガラスセラミックス基板及び該基板の上に受動素子を形成した薄膜電子部品並びにそれらの製造方法を提供することである。

【解決手段】本発明に係る薄膜電子部品用基板は、板状のセラミックス多結晶体若しくはガラスセラミックス体の少なくとも片面に、金属酸化物薄膜からなるコーティング層を設け、金属酸化物薄膜の膜厚を0.1μm以上20μm以下とし、且つ表面粗さRaを0.5nm以上20nm以下としたことを特徴とする。この高精度の平滑性を有する基板上に薄膜電子部品をPVD法等の薄膜デバイス製造技術を適用して形成する。

(もっと読む)

抵抗素子を有するプリント配線板およびその製造方法

【課題】抵抗素子を有するプリント配線板であって、絶縁層上への抵抗素子形成後、絶縁樹脂による被覆前に施される表面処理工程において、局部電池作用による配線の断線あるいは露出している銀電極の腐食を防止し、従って抵抗値の変動を抑えた抵抗素子を提供する。

【解決手段】少なくとも1本以上の配線途中に当該配線の一部である電極部と電極部間を接続する厚膜抵抗体からなる抵抗素子を具備するプリント配線板であって、前記抵抗素子の電極部は置換型無電解銀めっき皮膜により被覆され、前記銀めっき皮膜にて被覆された電極部は前記厚膜抵抗体により被覆されることを特徴とする抵抗素子を有するプリント配線板とする。

(もっと読む)

容量性デバイス、有機誘電体積層物、かかるデバイスを組み込んだ多層構造物、およびそれらの作製方法

【課題】多層構造物の形成方法および多層構造物自体を提供すること。

【解決手段】一実施形態においては、多層構造物の形成方法は、50から150の間の誘電率を有する常誘電体フィラーとポリマーとを含む誘電体組成物を用意するステップと、前記誘導体組成物をキャリアフィルムに被着させ、それによって誘電体層とキャリアフィルム層とを含む多層フィルムを形成するステップと、前記多層フィルムを回路付きコアに貼り付けるステップであって、前記多層フィルムの誘電体層が前記回路付きコアと対向するステップと、加工の前に前記キャリアフィルム層を前記誘電体層から除去するステップと、金属層を前記誘電体層に被着させるステップであって、前記回路付きコア、誘電体層および金属層がプレーナキャパシタを形成するステップと、前記プレーナキャパシタを加工して多層構造物を形成するステップとを含む。

(もっと読む)

内蔵型薄膜キャパシター、積層構造物及びそれらの製造方法

【課題】低温の成膜工程で充分な誘電率を有する誘電体膜を得て、これを備える薄膜キャパシター等を提供する。

【解決手段】第1及び第2金属電極膜とその間にBiZnNb系非晶質金属酸化物を用いて、誘電率が15以上の誘電体膜を含む薄膜キャパシターを形成する。ポリマー基盤複合体基材上に、順次、第1金属電極膜と、BiZnNb系非晶質金属酸化物を用いて成る、誘電率が15以上の誘電体膜と、第2金属電極膜を形成して積層構造物とする。誘電体膜として採用されるBiZnNb系非晶質金属酸化物は結晶化のための高温の熱処理工程がなくても、高い誘電率を示すため、印刷回路基板のようなポリマー基盤の積層構造物の薄膜キャパシターに有益に使用できる。

(もっと読む)

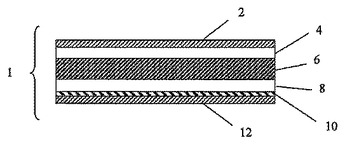

キャパシタ回路を備えるプリント配線板の製造方法及びその製造方法で得られたプリント配線板並びにそのプリント配線板を用いた内蔵キャパシタ回路を備える多層プリント配線板。

【課題】複雑な製造方法を必要とすることなく、キャパシタ回路部を除き、可能な限り誘電体層を除去したプリント配線板の製造技術を提供する。

【解決手段】基材2の表面に下部電極形成層/誘電層/上部電極形成層のキャパシタ回路形成層を設け、外層に位置する前記上部電極形成層をエッチング加工し、上部電極回路9等の回路部以外の領域の誘電層4を露出させ、前記上部電極回路9等の表面にエッチングレジスト層を残留させ、露出した誘電層4を物理的に粗く除去し、物理的に除去し、残留する誘電層4をエッチング除去し、前記上部電極回路9及びその他の回路部の表面に残留させたエッチングレジスト層を剥離し、下部電極形状を形成するためのエッチングレジスト層を形成し、第2エッチングレジストパターン10を形成した後、エッチング加工して、下部電極回路11を形成し、キャパシタ回路を備えるプリント配線板1とする。

(もっと読む)

部品内蔵配線基板用のコンデンサの形成方法

【課題】部品内蔵配線基板用のコンデンサの形成方法において、コンデンサの電極を誘電体を切断せずにトリミングで除去し、信頼性の低下と収率の悪化を防ぐ方法を提供する。

【解決手段】(1)コンデンサの下電極を、銅配線層をフォトリソグラフィとエッチングによって形成する工程(2)誘電体フィラーと絶縁樹脂が混合されている誘電体を下電極上に形成する工程(3)誘電体表面に導電性高分子膜を形成する工程(4)下電極の取出配線部と導電性高分子膜とにコンデンサ容量測定用の電極を接触し、容量を測定しながら所望の容量になるように導電性高分子膜をレーザー加工によって削り取り除去する工程(5)レーザー加工による導電性高分子膜を除去した部分を避け導電性高分子膜上ならびに誘電体上に導電性ペーストをコートする工程(6)導電性高分子膜上ならびに導電性ペースト上に電解めっきによって金属層を形成する工程によって、形成する。

(もっと読む)

プリント回路にパターニングされた埋め込み式静電容量層

パターニングされた埋め込み式静電容量層を作製する方法が開示される。方法は、プリント回路基材(505)の上に乗る導電性金属層(515)の上に乗るセラミック酸化物層(510)を作製する(1305,1310)こと、領域(705)内でセラミック酸化物層を穿孔する(1320)こと、及び、導電性金属層を化学エッチングすることによって、領域のセラミック酸化物層及び導電性金属層を除去することを含む。セラミック酸化物層は、1ミクロン厚より薄くてもよい。  (もっと読む)

(もっと読む)

抵抗器及びコンデンサ形成のための多層構造体

本発明は、抵抗器及びコンデンサを形成するために有用なものである多層構造体に関する。また、本発明の多層構造体は、印刷回路板、又は、その他の微細な電子デバイスを製造するためにも有用なものである。本発明の多層構造体は、第1の導電層と、第1の熱硬化ポリマー層と、熱抵抗フィルム層と、第2の熱硬化ポリマー層と、第2の導電層に電気めっきされたニッケル−リン電気抵抗材料層とが、順次付けられた層からなる構造を備えるものである。  (もっと読む)

(もっと読む)

プリント配線板およびその製造方法

【課題】個々の受動素子ごとに実験的に確認する必要をなくして、容易かつ簡便に任意の受動素子を設計することができ、スクリーン印刷法本来の利便性を十分に発揮することのできるプリント配線板とその製造方法を提供する。

【解決手段】基板1と、この基板1上に設けられた配線層2と、この配線層2と導通している電極3,4及びスクリーン印刷法にて印刷・形成された機能膜6とで構成される受動素子とを備える配線基板において、前記受動素子を複数個備えると共に、これら複数の受動素子の機能膜6を互いに同一面積とし、かつ、これら複数の受動素子を直列又は並列に接続する。

(もっと読む)

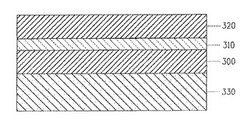

キャパシタ層形成材及びそのキャパシタ層形成材の製造方法並びにそのキャパシタ層形成材を用いて得られる内蔵キャパシタ層を備えたプリント配線板

【課題】製造コストメリットに優れたゾル−ゲル法を用いた誘電膜であって、従来に無い高い電気容量を備え且つ長寿命のキャパシタ回路を製造出来るキャパシタ層形成材を提供する。

【解決手段】上部電極形成に用いる第1導電層2と下部電極形成に用いる第2導電層3との間に誘電層4を備えるキャパシタ層形成材1において、当該誘電層4は、ゾル−ゲル法で形成した酸化物誘電膜であり、当該誘電層の厚さ方向及び平面方向に成長した粗大化結晶組織であり、且つ、粒径(長径)が50nm〜300nmの酸化物結晶組織を含むことを特徴としたキャパシタ層形成材を採用する。そして、このキャパシタ層形成材を効率よく得るための製造方法を提供する。

(もっと読む)

配線基板及びその製造方法

【課題】金属板を基材に用いながらも、耐熱性が良好であり、生産性にも優れた配線基板を提供すること。

【解決手段】Fe−Cr−Al系のステンレス鋼板からなり、所望の形状に加工された後の熱処理により表面全体に酸化アルミ皮膜が被覆されてなるステンレス鋼板1を基材とし、その基材における酸化アルミ皮膜2の上に配線3を形成した構成とする。必要に応じて保護膜4を形成する。Fe−Cr−Al系のステンレス鋼板に対する熱処理により形成した酸化アルミ皮膜を絶縁層として使用するため、従来のように接着剤用途での樹脂を必要としないことから、基材の耐熱性が良好であり、熱の問題があったり高温条件下で使用されるというような環境においても対応することができ、しかも基材表面の酸化アルミ皮膜は鋼材内部からの拡散により形成されたものであるので、絶縁層と金属板との接着強度が大きく、配線基板自体の機械的強度も良好である。

(もっと読む)

回路配線基板及びその製造方法

【課題】小形化および高周波帯域動作に適した受動素子内蔵形の回路配線基板及びその製造方法を提供するものである。

【解決手段】回路配線基板1において、互いに誘電率が異なり板面に沿う方向に相互に隣接された第1基板部分21及び第2基板部分22によって構成された平板状の絶縁基板2と、少なくとも前記第2基板部分22に設けられた受動素子と、前記受動素子の電極部分を構成する素子用導電層C1a乃至C5a、L1、L2等と、前記導電層に電気的に接続され前記第1基板部分に設けられた回路配線層31a乃至34a等とを備え、前記第1及び第2基板部分はそれぞれの板面が前記絶縁基板の平板状板面にほぼ面一に揃うように配置され、前記素子用導電層及び回路配線層は前記絶縁基板の板面上に並置されている。

(もっと読む)

21 - 40 / 55

[ Back to top ]