Fターム[4G077DB01]の内容

結晶、結晶のための後処理 (61,211) | 気相成長−CVD (2,039) | 基板上に気相成長させるもの (1,635)

Fターム[4G077DB01]の下位に属するFターム

反応原料の選択 (1,331)

Fターム[4G077DB01]に分類される特許

81 - 100 / 304

ビスマス層状構造強誘電体結晶の製造方法

【課題】抗電界Ecが小さく残留分極Prが大きいビスマス層状構造強誘電体結晶の製造方法を提供する。

【解決手段】本発明の製造方法は、ビスマスおよびビスマス化合物から選ばれる少なくとも1つのビスマス供給用材料を含む材料を用いてビスマスを含む層状構造強誘電体の結晶(A)を形成する工程と、結晶(A)を、酸素分圧が1気圧以上の雰囲気下において熱処理する熱処理工程とを含む。ビスマス供給用材料に含まれるビスマスの純度は、99.999モル%以上である。

(もっと読む)

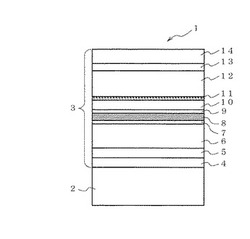

発光素子用エピタキシャルウェハおよびその製造方法

【課題】高品位で且つ低コストな発光素子用エピタキシャルウェハを提供する。

【解決手段】n型基板2上に、少なくともn型クラッド層6、活性層8、p型クラッド層を順次積層する化合物半導体発光素子用エピタキシャルウェハにおいて、n型基板2として、ほぼ円形であるn型基板の直径を(a)、n型基板の厚さを(b)としたとき、(b)/(a)が0.0047以下であるn型基板を用いて作製したものである。

(もっと読む)

半導体基板の製造方法、半導体基板

【課題】シリコン層又はシリコン基板上に、欠陥密度が低く高品質なエピタキシャル層を、少ない工程で低コストに形成することが可能な半導体基板の製造方法を提供する。

【解決手段】シリコンウエーハ11の一面11aに対して、ウエットエッチング法によって異方性エッチングを行う。シリコンウエーハ11の一面11aに対して、異方性エッチングを行うと、シリコンウエーハ11の一面11aに微細な凹凸12が形成される。この微細な凹凸12は、例えば(111)面からなる傾斜面12a,12bで構成された溝14が、周期的に多数形成されたものであればよい。

(もっと読む)

単結晶ゲルマニウムコバルトナノワイヤ、ゲルマニウムコバルトナノワイヤ構造体、及びその製造方法

反応炉の上流部に位置させたハロゲン化コバルトを含む第1先駆物質、反応炉の下流部に位置させたゲルマニウムを含む第2先駆物質、反応炉の下流部に位置させた基板を不活性ガス雰囲気で熱処理して、基板上にxが0.01以上0.99未満の値を有する単結晶体のCoxGe1−xナノワイヤが形成される。また、基板としてグラフェンまたは高配向熱分解性黒鉛基板を用い、基板上に対して垂直配向性を有し、均一なサイズの高密度ゲルマニウムコバルトナノワイヤ構造体を提供することにより、ゲルマニウムコバルトナノワイヤを電界放出エミッタとして、ゲルマニウムコバルトナノワイヤが形成された基板を電界放出ディスプレイの陰極パネルの透明電極として使用できる。 (もっと読む)

SiC薄膜形成装置

【課題】同一のSiC薄膜形成プロセスの進行中に、基板の前処理段階(昇温過程および高温過程)および基板上への薄膜の成長段階において、あるいは更に降温段階において、供給する炭化水素ガス種を瞬時に切り替えて、各段階に最適な種類の炭化水素ガスを供給できるCVDによるSiC薄膜形成装置を提供する。

【解決手段】SiC単結晶の薄膜を成長させる基板14を保持するサセプタ12を内蔵したCVD反応容器10、および該CVD反応容器にそれぞれ接続されたSi原料ガスの供給器26および炭化水素ガスの供給器28を備えたSiC薄膜形成装置において、上記炭化水素ガスの供給器は、それぞれ相互に独立して供給を制御可能な複数の炭化水素ガス源C1、C2、C3に接続されている。

(もっと読む)

サファイア基板を活性窒素に暴露して半導体デバイスを作製する方法及び半導体デバイス

【課題】真性に近い単結晶GaN膜を有し、かつこの膜をn形又はp形に選択的にドープした半導体デバイスを提供する。

【解決手段】次の要素を有する半導体デバイス:基板であって、この基板は、(100)シリコン、(111)シリコン、(0001)サファイア、(11−20)サファイア、(1−102)サファイア、(111)ヒ化ガリウム、(100)ヒ化ガリウム、酸化マグネシウム、酸化亜鉛、および炭化シリコンからなる群から選択される物質からなる;約200Å〜約500Åの厚さを有する非単結晶バッファ層であって、このバッファ層は前記基板の上に成長した第一の物質を含み、この第一の物質は窒化ガリウムを含む;および前記バッファ層の上に成長した第一の成長層であって、この第一の成長層は窒化ガリウムと第一のドープ物質を含む。

(もっと読む)

エピタキシャルウェーハの製造方法。

【課題】気相成長装置のサセプタの凹部においてシリコンウェーハの移動を防止し、ウェーハの周縁部が凹部の内周面に接触することを防止してそのウェーハの割れを回避する。

【解決手段】エピタキシャルウェーハの製造方法は、サセプタ20の凹部21にシリコンウェーハ10を収容してサセプタを回転させるとともに昇温させた後にシリコンウェーハの主面にエピタキシャル層を形成する。シリコンウェーハの凹部への収納はシリコンウェーハの周縁部11が凹部の内周面に接触しないように凹部の中央に設置する。昇温はサセプタを回転させないか或いは0.5rpm以下の一定速度で回転させつつ行われ、シリコンウェーハが昇温されて800〜1100℃の一定温度に達した後にサセプタの回転速度を増加る。サセプタの回転速度が4〜8rpmの一定速度に達した後に反応炉にシリコン原料含有ガスを供給してシリコンウェーハの主面にエピタキシャル層を形成する。

(もっと読む)

単結晶ダイヤモンドの表面損傷の除去方法

【課題】単結晶ダイヤモンド基板の表面損傷を除去するために有効な新規な方法および表面損傷が除去された単結晶タイヤモンドを基板としたCVD法による単結晶ダイヤモンドの製造方法を提供する。

【解決手段】単結晶ダイヤモンドにイオン注入を行って表面近傍に非ダイヤモンド層を形成し、該非ダイヤモンド層をグラファイト化させた後、エッチングして表面層を除去する。この様にして得られた単結晶ダイヤモンドは、表面粗さを増加させることなく、切断、研磨などによって生じた表面損傷部がほぼ完全に除去され、また、表面と交差する転位もほとんど存在しないものとなるので、処理された単結晶ダイヤモンドを基板として、CVD法によってダイヤモンドを成長させることによって、転位の伝播や新たな転位の発生を著しく抑制することができ、形成される単結晶ダイヤモンドの結晶性を著しく改善することができる。

(もっと読む)

単結晶ダイヤモンド

【課題】実質的に表面欠陥がない基体の上に化学蒸着により成長したダイヤモンドから、化学蒸着によって、単結晶ダイヤモンドの大面積プレートを製造する方法。化学蒸着によりホモエピタキシャル成長した前記ダイヤモンド及び前記基体は、ダイヤモンド成長が起こった基体の表面を横切って切り離し、化学蒸着による単結晶ダイヤモンドの大面積プレートを製造することである。

【解決手段】化学蒸着による(001)単結晶ダイヤモンドプレートにおいて、それの向かい合う側に、{100}側表面によって範囲が定められる主表面を有する前記ダイヤモンドプレートであって、各々の主表面が、10mmを超える少なくとも1つの長さ寸法を有している、上記ダイヤモンドプレート。

(もっと読む)

半導体デバイス、窒化物半導体基板及びその製造方法

【課題】 、全面に渡って転位密度を低減し、クラック発生を抑制することが可能な窒化物半導体基板及びその製造方法、及び半導体デバイスを提供する。

【解決手段】 この窒化物半導体基板は、基板(A、B,D1)と、基板(A、B,D1)上に形成され離間した結晶成長制限部Cと、基板(A、B,D1)及び結晶成長制限部Cを被覆し、その露出表面の、Z軸に平行な断面(XZ断面)が、波の形状を構成し、この波の形状が多角形状になまっている窒化物半導体からなる波状層(D2,E,F2)と、波状層(D2,E,F2)上に形成され窒化物半導体からなる平坦化層Gとを備えている。形状変更層F2の露出表面が熱処理によって多角形状になまっているため、埋め込む山谷差が小さくなり、埋め込み体積が減るため、埋め込み成長がし易く、平坦化層Gが形状変形層F2内に緻密に埋まっている。

(もっと読む)

<110>方位を有するエピタキシャル被覆されたシリコンウェハ及びその製造方法

【課題】チョクラルスキー法によるシリコン単結晶の引き上げにおいて、転位除去のため結晶の幾何学的軸を実際の[110]結晶軸に対して所定の角度分傾斜させてて成長させたシリコン単結晶の方位を、単結晶育成後、エピタキシャル成長に適した方位に補正する方法を提供する。

【解決手段】(110)結晶面に比べて方位差を有する平面をウェハ表面として有するエピタキシャル被覆されたシリコンウェハにおいて、<110>方向はウェハ表面に対する法線から角度θ傾斜されていて、かつ傾斜された<110>方向の前記ウェハ平面中の方向<−110>での投影は角度φを形成し、θは0≦θ≦3゜及び45゜≦φ≦90゜(及び全ての対称的に等価の方向)で与えられるシリコンウェハ。

(もっと読む)

炭化珪素エピタキシャル成長用炭化珪素単結晶ウェハ及び炭化珪素エピタキシャルウェハ

【課題】結晶欠陥の少ない炭化珪素エピタキシャルウェハを製造するためのエピタキシャル成長用の炭化珪素単結晶ウェハを提供する。

【解決手段】エピタキシャル成長面を上として、エピタキシャル成長用炭化珪素単結晶ウェハの形状を上に凸な形状とする。さらに好ましくは、炭化珪素単結晶ウェハのそりが0μm超100μm以下であり、上に凸である形状を持つ部分がウェハ面積全体の60%以上であり、炭化珪素単結晶のc軸と炭化珪素単結晶ウェハ面の法線のなす角が0°以上4°未満、より好ましくは、0°以上1°未満である炭化珪素単結晶ウェハを使用することにより、炭化珪素エピタキシャル膜を製膜する際に炭化珪素エピタキシャル膜中で発生する欠陥の数を減らし、良質の炭化珪素エピタキシャルウェハを製造する。

(もっと読む)

半導体エピタキシーにおけるメモリ効果の低減方法

水素ガス及びハロゲン含有ガスを含む混合ガスを使用して、複数の成長段階同士の間にCVD反応チャンバを洗い流すことによって、エピタキシャル成長工程の間のメモリ効果を低減する方法を提供する。 (もっと読む)

エピタキシャルシリコンウェーハ

【課題】結晶欠陥密度の非常に小さいエピタキシャルシリコンウェーハを提供する。

【解決手段】チョクラルスキー法により成長させたシリコン単結晶から切り出して加工した基板ウェーハの表面に、エピタキシャル成長によってシリコンエピタキシャル層を形成したエピタキシャルシリコンウェーハにおいて、前記基板ウェーハの直径が450mm以上であって、前記基板ウェーハは、空孔型点欠陥の凝集体を含まず、かつ高温酸化処理を施した際に酸化誘起積層欠陥領域がウェーハ内に発生せず、空孔型点欠陥の凝集体及び格子間シリコン型点欠陥の凝集体が存在しない無欠陥領域又は格子間シリコン型点欠陥優勢領域のいずれか一方又は双方からなる。

(もっと読む)

半導体をその基板から分離する方法

【課題】 本発明の目的は半導体をその基板から分離する方法を提供することである。

【解決手段】 複数の棒状体を基板上に形成し、複数の棒状体上で半導体層をエピタキシー成長させ、更に、複数の棒状体の間の空隙にエッチング液を注入することによって、半導体層をその基板から分離する。複数の棒状体の間の空隙がエッチングの反応面積を大幅に増加させることができるため、本発明による方法によれば、エッチングによって半導体層を基板から分離する効率を向上させ、製造工程のコストを低減させることができ、しかも、基板に使われる材料も前記分離方法に制限されない。

(もっと読む)

p型単結晶ZnO

【課題】実用レベルの発光素子を与えるに十分な低い抵抗率で且つn型ZnOと接合したとき優れたダイオード特性を示すp型ZnO単結晶及びその製造方法の提供。

【解決手段】ドーパントとして窒素とIB族元素とを含有し,IB族元素がCu及びAgより選ばれる少なくとも1種であり,温度20℃における抵抗率が0.1〜20Ω・cmである,p型単結晶ZnO,並びに,化学気相成長法によるp型単結晶ZnOの製造方法であって,(a)(0001)面を表面とする単結晶ZnO基板を加熱しつつ,基板の表面にZn源ガス,O源ガス,アンモニア並びに,Cu及びAgより選ばれるIB族元素源ガスを供給して基板上に,窒素及びIB族元素をp型ドーパントとして含んだ単結晶ZnOを成長させるステップと,(b)p型ドーパントを含んだ単結晶ZnOをO源ガスの存在下にアニールするステップを含んでなる,p型単結晶ZnOの製造方法。

(もっと読む)

半導体結晶成長用基板および半導体結晶

【課題】結晶欠陥の少ない半導体層を形成する。

【解決手段】面方位が(111)であるSiからなる半導体結晶成長用基板本体11の外周部に膜厚が100nmの窒化シリコンからなる保護膜14を形成する。すなわち、半導体結晶成長用基板本体11の側面12および半導体結晶成長用基板本体11の表面13の最外周から2mmまでの部分に保護膜14を形成する。また、半導体結晶成長用基板本体11の表面13の保護膜14が形成されていない領域上にAlNからなるバッファ層21を形成し、バッファ層21上に膜厚が3μmのGaN結晶からなる半導体層22を形成する。

(もっと読む)

ダイヤモンド薄膜形成用基板、該基板を用いてなる半導体基板及びその製造方法

【課題】シリコン基板上に緻密なダイヤモンド薄膜を形成させるためのシリコン基板及びその製造方法であって、1000℃以上の高温でも孔形態が変化せず、核発生密度も維持でき、熱膨張係数差に伴う応力の緩和機構も備えたダイヤモンド薄膜形成用シリコン基板およびその製造方法を提供すること。

【解決手段】サブミクロン〜ミクロンサイズの柱状多孔質層とナノサイズシリコン粒子層からなる2層構造を、所定濃度のフッ酸系電解液中で、シリコン単結晶基板を陽極酸化する電解酸化することによって、シリコン単結晶基板表面に設ける。

(もっと読む)

窒化物半導体および窒化物半導体の結晶成長方法ならびに窒化物半導体発光素子

【課題】表面モルフォロジと光学特性がともに良好で、しかも発光素子とした場合の発光効率が高い、高品質の窒化物半導体を提供すること。

【解決手段】m面のような非極性面の窒化物基体上に窒化物半導体を結晶成長させるに際し、窒化物半導体層を成長させる前の比較的高温領域での昇温過程におけるメインフローを構成するガス(基体の窒化物主面が暴露される雰囲気)、第1および第2の窒化物半導体層成長完了までのメインフローを構成するガス(基体の窒化物主面が暴露される雰囲気)を、窒化物に対してエッチング効果のないものを主とし、かつ、窒化物半導体層の成長開始時にはSi源を供給しないこととした。このため、エピタキシャル基体の窒化物表面近傍からの窒素原子の脱離が生じず、エピタキシャル膜への欠陥導入が抑制される。また、平坦性に優れた表面モルフォロジを有するエピタキシャル成長が可能となる。

(もっと読む)

光デバイス用基板及びその製造方法

【課題】酸化ガリウム基板部材を用いながらも表面平坦性に優れ且つ結晶品質性に優れた窒化ガリウム層を有する光デバイス用基板及びその製造方法を提供する。

【解決手段】サーマルクリーニングを施したGa2O3基板部材を窒化処理してGa2O3基板部材の表面上に六方晶GaNからなる第1のバッファ層を形成し、第1のバッファ層の表面上に成長温度480〜520℃で六方晶GaNからなる第2のバッファ層を成長形成した後、第2のバッファ層の表面上に光デバイス用基板の表面層として成長温度650〜750℃で六方晶GaN層を成長形成する。

(もっと読む)

81 - 100 / 304

[ Back to top ]