Fターム[4K030DA08]の内容

Fターム[4K030DA08]の下位に属するFターム

熱処理 (328)

Fターム[4K030DA08]に分類される特許

121 - 140 / 607

III族窒化物結晶の製造方法

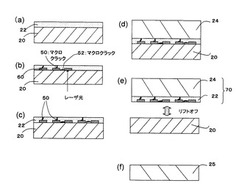

【課題】保持基板上に成長したIII族窒化物結晶を、結晶品質を劣化させることなく剥離することができる

III族窒化物結晶の製造方法を提供する。

【解決手段】(a)保持基板20上の表側主面に、第1のIII族窒化物結晶層22を形成する工程と、(b)前記保持基板20裏側主面からレーザ光を照射して、前記第1のIII窒化物結晶層22の裏面側をレーザ加工する工程と、(c)前記第1のIII族窒化物結晶層22の表側主面に第2のIII族窒化物結晶層24を成長する工程と、(d)前記保持基板20と前記第1のIII族窒化物層22の界面から分離する工程とを備え、(e)前記工程(b)において、前記第1のIII族窒化物結晶層22の表側主面にレーザ加工時に発生する分解ガスを放出するガス放出構造体を設ける。これにより、レーザ加工部の基板全体に対する面積を大きくすることができるので、剥離の際の応力による結晶のクラックを低減できる。

(もっと読む)

硬質被覆層がすぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具

【課題】硬質被覆層が高速重切削加工ですぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具を提供する。

【解決手段】工具基体の表面に、(a)下部層としてTi化合物層、(b)中間層としてα型Al2O3層、(c)上部層として、平板多角形状かつたて長形状の結晶粒組織構造を有するZr含有α型Al2O3層を蒸着形成した表面被覆切削工具において、逃げ面および切刃部の中間層及び上部層は、それぞれ、(0001)面配向率の高いα型Al2O3層、Zr含有α型Al2O3層からなり、また、逃げ面および切刃部の上部層の結晶粒の内、面積比率で60%以上の結晶粒の内部は、少なくとも一つ以上のΣ3で表される構成原子共有格子点形態からなる結晶格子界面により分断されている。

(もっと読む)

炭素膜の形成方法、磁気記録媒体、及び磁気記録再生装置

【課題】本発明は、潤滑剤に対する濡れ性が高く、平滑な表面を有し、高硬度で緻密な水素を含む炭素膜を形成することを可能とした炭素膜の形成方法、並びに、該炭素膜の形成方法により形成された水素を含む炭素膜を有する磁気記録媒体及び磁気記録再生装置を提供することを課題とする。

【解決手段】水素を含む炭素膜の形成後に、成膜室101内に不活性ガスを導入し、不活性ガスをイオン化して水素を含む炭素膜の表面に加速照射し、水素を含む炭素膜の少なくとも表層部を脱水素化する。

(もっと読む)

NGO基板、窒化物系化合物半導体基板の製造方法、窒化物系化合物半導体基板及び窒化物系化合物半導体自立基板

【課題】低温保護層の成長プロセスを省略でき、GaN系半導体基板の製造コストを低減できるとともに、低温保護層の品質のばらつきによる影響を排除できる窒化物系化合物半導体基板の製造方法を提供する。

【解決手段】平均表面粗さが0.2〜10nmに制御された成長用基板上に、窒化物系化合物半導体層をエピタキシャル成長させる。例えば、成長用基板をエピタキシャル成長装置に投入した後、成長用基板の平均表面粗さが0.2〜10nmとなるようにアニール処理を施す。

(もっと読む)

エピタキシャル成長用基板、窒化物系化合物半導体基板及び窒化物系化合物半導体自立基板

【課題】エピタキシャル成長用基板上に直接GaN系半導体厚膜層を成長させるGaN系半導体基板の製造方法により、GaN系半導体基板を生産性よく製造できる技術を提供する。

【解決手段】900℃〜1050℃の成長温度で窒化物系化合物半導体層を直接エピタキシャル成長させる際に、成長温度までの昇温プロセスにおいて表面粗さが10nmを超えて劣化しないエピタキシャル成長用基板を用いる。

具体的には、1200℃以上1400℃以下で5〜20時間保持するインゴットアニール処理を施されたNGO基板を用いる。

(もっと読む)

硬質被覆層がすぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具

【課題】硬質被覆層が高速重切削加工ですぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具を提供する。

【解決手段】工具基体の表面に、(a)下部層としてTi化合物層、(b)中間層としてα型Al2O3層、(c)上部層として、平板多角形状かつたて長形状の結晶粒組織構造を有するTi含有α型Al2O3層を蒸着形成した表面被覆切削工具において、逃げ面およびすくい面の中間層及び上部層は、それぞれ、(0001)面配向率の高いα型Al2O3層、Ti含有α型Al2O3層からなり、また、逃げ面およびすくい面の上部層の結晶粒の内、面積比率で60%以上の結晶粒の内部は、少なくとも一つ以上のΣ3で表される構成原子共有格子点形態からなる結晶格子界面により分断されている。

(もっと読む)

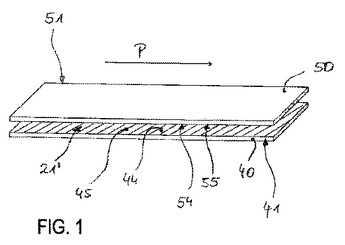

バリアフィルムの製造方法及び製造装置

【課題】バリアフィルムの製造中であってもバリアフィルムのバリア性能の異常をリアルタイムに把握することができるので、異常に対する対応を迅速に取ることができるバリアフィルムの製造方法及び製造装置を提供する。

【解決手段】真空な成膜装置内で長尺な可撓性フィルムWを搬送しながらバリア膜を形成すると共に、可撓性フィルムWの搬送に段付きローラRを用いるバリアフィルムの製造装置において、成膜装置内であって、バリア膜を形成した後に少なくとも配置された段付きローラに設けられ、可撓性フィルムが段差ローラの中央部52側へ変形する変形距離を非接触で検出する変形距離検出手段72と、検出した検出値と変形距離Lの設定基準値とを比較する比較手段74と、比較した結果、検出値が設定基準値よりも大きいときに、変形を生じたバリアフィルム部分のバリア性能が不合格であると判定する判定手段76と、を備える。

(もっと読む)

硬質被覆層がすぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具

【課題】硬質被覆層が高速重切削加工ですぐれた耐剥離性と耐摩耗性を発揮する表面被覆切削工具を提供する。

【解決手段】工具基体の表面に、(a)下部層としてTi化合物層、(b)中間層としてα型Al2O3層、(c)上部層として、平板多角形状かつたて長形状の結晶粒組織構造を有するY含有α型Al2O3層を蒸着形成した表面被覆切削工具において、逃げ面およびすくい面の中間層及び上部層は、それぞれ、(0001)面配向率の高いα型Al2O3層、Y含有α型Al2O3層からなり、また、逃げ面およびすくい面の上部層の結晶粒の内、面積比率で60%以上の結晶粒の内部は、少なくとも一つ以上のΣ3で表される構成原子共有格子点形態からなる結晶格子界面により分断されている。

(もっと読む)

コーティングされたセラミック切削インサートおよびその作製方法

炭素系物質除去方法及び該除去方法を備えた部品等の製造方法・リサイクル方法

【課題】炭素系素材及び炭素系コーティング膜を表面にもつ部品等の所定部位を選択的にかつ効率的に物質除去し、所定の寸法、形状の除去範囲を獲得する。

【解決手段】グラファイト、グラッシー・カーボン、アモルファス・カーボン(ダイヤモンド・ライク・カーボンを含む)、カーボン・ナノ・チューブ、フラーレン、焼結ダイヤモンド、天然ダイヤモンドのいずれか又はそれを含む炭素系素材又はそれらの炭素系素材からなる部品若しくは部材において、任意に選択した表面部位に、原子状酸素3あるいは活性化酸素あるいは酸素系イオンのいずれか一つ又は複数を同時に、室温以上で処理対象素材の軟化点以下の温度のもとで付与することにより、所定の寸法、形状にまで,上記任意に選択した表面部位の上記炭素系物質を除去する炭素系物質除去方法とする。

(もっと読む)

コーティングされたPCBN切削インサート、かかるコーティングされたPCBN切削インサートを使用したコーティングされたPCBN切削工具、およびその作製方法

グラフェン膜のエピタキシャル成長方法

【課題】大規模、均一かつ高品質のグラフェン膜およびその作成方法を提供する。

【解決手段】結晶質基板100上に触媒薄膜101を形成し、この触媒薄膜を加熱処理して高秩序で選択的に配向した結晶質触媒薄膜を形成し、ガス状炭素源を加熱し触媒薄膜を冷却することで、触媒薄膜上にグラフェン膜102が形成される。前記触媒薄膜の触媒材料はNi、Pt、Co、Fe、Al、Cr、Cu、Mg、Mn、Rh、Ti、Pd、Ru、Ir及びReからなる群から選択された1つまたは複数の元素を含み、厚さは約1nmから約2mmの範囲である。

(もっと読む)

半導体装置の製造方法及び基板処理方法及び基板処理装置

【課題】

汚染物やパーティクルがシリコン膜等を有する基板に混入することにより基板の品質や半導体装置の性能が劣化することを抑制し、表面粗さの小さいシリコン膜を形成する。

【解決する手段】

基板にシリコン膜を形成する膜形成工程と、前記シリコン膜に酸化種を供給し、前記シリコン膜を熱処理し前記シリコン膜の表層を酸化シリコン膜に改質する改質工程と、前記酸化シリコン膜を除去する除去工程と、を有する半導体装置の製造方法を提供することで上記課題を解決する。

(もっと読む)

薄膜光電変換装置

【課題】薄膜光電変換装置において、大面積化に適した技術により歩留まりの低下を引き起こさずに高生産性を維持し、かつ、酸化亜鉛からなる透明電極層と光電変換ユニットとの間に良好な接合界面を形成することにより光電変換装置の変換効率を改善する。

【解決手段】光入射側から順に、少なくとも酸化亜鉛層と、p型半導体層と、光電変換層と、裏面電極層とを備える光電変換装置であって、酸化亜鉛層とp型半導体層からなる界面近傍における酸化亜鉛の化学量論組成比をZn:O=1+N:1(ただし、N>0)としたことを特徴とする、光電変換装置。

(もっと読む)

多層体を処理するための配列、システム、および方法

本発明は、各々が少なくとも1つの処理対象面を有する少なくとも2つの多層体、ならびに多層体を位置決めするための少なくとも1つの装置を含む、多層体配列に関し、装置は、それぞれの処理対象面が互いに向かい合っており、そうして処理対象面の間に設けられた準閉鎖処理空間を形成するように構成されており、そこで処理が行われる。本発明はさらに、このような多層体配列を用いて多層体を処理するシステム、ならびに多層体を処理する方法にも関し、多層体は、それぞれの処理対象面が互いに向かい合っており、そうして表面の間に設けられた準閉鎖処理空間を形成するように設けられており、そこで処理が行われる。  (もっと読む)

(もっと読む)

半導体素子製造方法

【目的】

専用の装置を必要とすることなく工程数を低減した半導体素子製造方法を提供する。

【構成】

ウエハ状の基板に少なくとも1つの半導体素子を製造する半導体素子製造方法であり、前記基板のウエハ表面上に少なくとも1層の膜をこれに対応する成膜材料を用いて成膜する成膜ステップと、当該成膜がなされたウエハ表面に不活性ガスを供給しつつ、当該成膜がなされたウエハの周囲に前記成膜材料に適合するエッチングガスを供給することによって、前記ウエハ表面以外のウエハ部分の膜除去を行う膜除去ステップと、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】従来のCVD法で形成された窒化チタン膜と比較して良質な窒化チタン膜を、ALD法で形成された窒化チタン膜と比較して速い成膜速度で、すなわち高い生産性で提供することが可能な半導体装置の製造方法及び基板処理装置を提供することにある。

【解決手段】処理室に基板を搬入する基板搬入工程と、前記処理室に第1の処理ガス及び第2の処理ガスを同時に供給して前記基板に所定の膜を形成する膜形成工程と、前記第1の処理ガス及び前記第2の処理ガスの供給を停止して前記処理室内に残留する第1の処理ガス及び第2の処理ガスを除去する除去工程と、前記除去工程の後に、前記処理室に前記第2の処理ガスを供給して前記基板に形成された膜を改質する改質工程と、前記処理室から前記基板を搬出する基板搬出工程と、を有し、前記膜形成工程では、前記処理室に前記第2の処理ガスを供給する時間が、前記処理室に前記第1の処理ガスを供給する時間より長いことを特徴とする。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】高いエッチング耐性を有し、誘電率の低い窒化ホウ素膜を得ることのできる基板処理装置を提供する、あるいは、高いエッチング耐性を有し、誘電率の低い窒化ホウ素膜を形成することのできる半導体装置の製造方法を提供する。

【解決手段】処理室21内に基板16を搬入する工程と、前記処理室21内に少なくともホウ素含有ガス31aを供給し、前記基板16上にホウ素膜を形成するホウ素膜形成工程と、処理室内に少なくとも窒素含有ガス31cを供給し、ホウ素膜形成工程で形成したホウ素膜を窒化する窒化処理工程とを有し、ホウ素膜形成工程と窒化処理工程とから構成される一連の処理工程を、2回以上繰り返すことにより、所定膜厚の窒化ホウ素膜を形成する。

(もっと読む)

窒化物半導体自立基板及び発光装置

【課題】自立基板の反りを低減した窒化物半導体自立基板及びそれを用いた発光装置を提供する。

【解決手段】本発明に係る窒化物半導体自立基板は、連続成長した窒化物半導体結晶からなる窒化物半導体自立基板において、窒化物半導体自立基板の内部に、基板表面と平行な断面において10個/cm2以上から600個/cm2以下の密度でインバージョンドメインを有し、前記基板表面は、0個/cm2以上から200個/cm2以下の密度でインバージョンドメインを有し、前記窒化物半導体自立基板の内部のインバージョンドメインよりも前記基板表面に到達するインバージョンドメインの密度が少ない。

(もっと読む)

コーティング前処理方法、ダイヤモンド被膜のコーティング方法、および脱膜処理方法

【課題】ブラスト処理が困難な凹凸の大きい複雑な表面やアスペクト比の大きな穴内面などに対しても適切に表層部を除去して内部の略均一な組織を露出させ、高い付着強度でダイヤモンド被膜をコーティングできるようにする。

【解決手段】ステップS1のコーティング前処理では、酸素プラズマにより基材12の表面を酸化させるとともに、超音波洗浄でその酸化物を除去するため、本焼結の際に形成される焼結肌が適切に除去され、その上に形成されるダイヤモンド被膜18の付着強度が向上する。ステップS1−1の酸化処理では、基材12に負のバイアス電圧を印加するため、基材12の表面に沿って高密度の酸素プラズマが略均一に生成され、アスペクト比の大きな穴内面16に対しても適切に酸化処理が施され、穴内面16を含む基材12の表面全域において焼結肌が短時間で適切に除去される。同様の処理でダイヤモンド被膜18の脱膜処理を行うこともできる。

(もっと読む)

121 - 140 / 607

[ Back to top ]