Fターム[4M104AA02]の内容

Fターム[4M104AA02]に分類される特許

381 - 393 / 393

複数の半導体層を備えた半導体デバイス

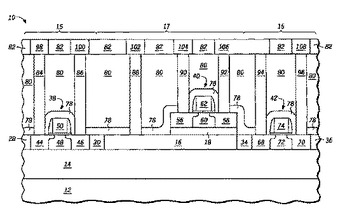

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

高誘電率誘電材料への酸窒化シリコン層の形成

本発明の実施形態は、基板上に配置された誘電層上にキャッピング層を堆積するための方法を提供する。一例では、プロセスは、基板を堆積プロセスに曝して、この上に誘電層を形成するステップと、該基板をシリコン前駆体および酸化ガスの順次パルスに曝して、堆積プロセス中にシリコン含有層を該誘電層上に形成するステップと、該基板を窒化プロセスに曝して、この上にキャッピング層を形成するステップと、所定の時間該基板をアニーリングプロセスに曝すステップとを含む。該キャッピング層は約5Å以下の厚さを有していてもよい。一例では、該酸化ガスが、触媒を含有する水蒸気生成器によって処理された水素源ガスおよび酸素源ガスから生じた水蒸気を含有する。別の例では、該堆積、窒化およびアニーリングプロセスが同じプロセスチャンバで生じる。 (もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

ショットキ・コンタクトを形成するために半導体上に導電性炭素材料を堆積するための方法、及び半導体コンタクト・デバイス

【課題】 本発明は、ショットキ・コンタクト(16)を形成するために半導体(14)上に導電性炭素材料(17)を堆積する方法に関する。

【解決手段】 本発明の方法は、半導体(14)をプロセス・チャンバ(10)内に導入するステップと、プロセス・チャンバ(10)の内部(10')を所定温度に加熱するス

テップと、プロセス・チャンバ(10)を第1所定圧力以下に減圧するステップと、プロセス・チャンバ(10)の内部(10')を第2所定温度に加熱するステップと、少なく

とも炭素を含むガス(12)を、第1所定圧力よりも高い第2所定圧力に達するまで導入するステップと、少なくとも炭素を含むガス(12)から、半導体(14)上に導電性炭素材料(17)を堆積することにより、半導体(14)上に堆積した炭素材料(17)がショットキ・コンタクト(16)を形成するステップを備えている。

(もっと読む)

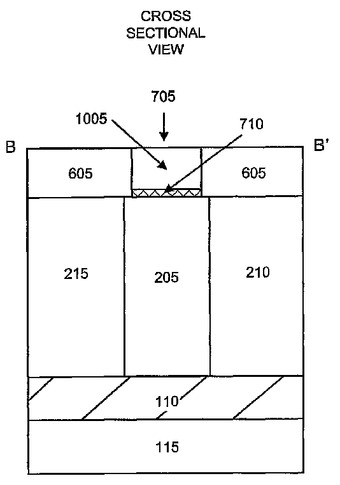

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

ダマシンプロセスにより形成されるトライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の第1端部に隣接するソース領域(210)、フィン(205)の第2端部に隣接するドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上にダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、絶縁層(605)中にトレンチ(705)を形成するように、ダミーゲート(505)を除去するステップと、トレンチ(705)中に金属ゲート(905)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

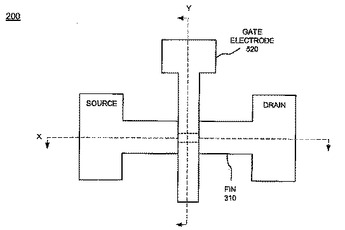

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

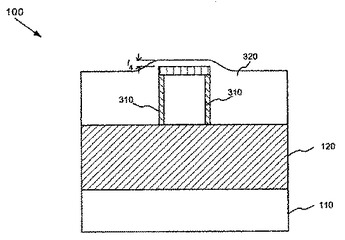

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

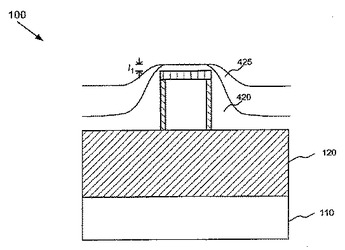

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

381 - 393 / 393

[ Back to top ]