Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

1,361 - 1,380 / 1,477

半導体装置の作製方法

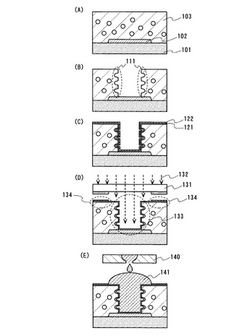

【課題】従来のCMPプロセスを用いることなく、高アスペクト比の開口を有する接続孔にも良好な埋め込みが可能である半導体装置の作製方法を提供する。また、従来よりも少ない工程数で、配線形成が可能な方法を提供することを目的とする。更には、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】複数の空孔を有する絶縁膜表面に撥水表面を有する膜を形成し、撥水表面を有する膜の一部に光を照射して、親水表面を有する領域を形成した後、親水表面を有する領域に導電性粒子を有する液状物質を吐出し、焼成して導電膜を形成することを特徴とする。

(もっと読む)

化合物半導体装置の製造方法

【課題】 スイッチMMICに採用するHEMTは、Pt埋め込みゲート構造の場合、ゲート電極となるPtの蒸着膜厚を40Å〜60Åにするとよい。しかし、膜厚数十Åの蒸着金属の膜厚制御は膜厚が薄過ぎるため、蒸着機のチャンバー内に通常配置されている水晶振動子式膜厚計による制御では制御できない。

【解決手段】 蒸着機内に抵抗素子を配置した抵抗回路を設ける。抵抗素子は絶縁基板の両端に電極が配置され、HEMTのゲート金属層の蒸着と同時に絶縁基板にモニター用金属層が蒸着される。モニター用金属層の抵抗値を測定し、所定の値に達した時点で蒸着を終了させることにより、膜厚数十Åの蒸着金属の膜厚制御を、水晶振動子式膜厚計による膜厚制御よりはるかに精度良く制御できる。

(もっと読む)

半導体電子装置

【課題】ELO(Epitaxial Lateral Over Growth)を用いる半導体装置において、選択マスク材料からSiの拡散を抑えつつ高純度のGaNを成長させて、高耐圧特性を有する半導体素子を実現する。

【解決手段】単結晶基板101上に選択的に形成されたSiO2マスク103とGaN層104、106が順次形成された構造であって、SiO2マスク103の誘電率がGaN層104より低く、さらにGaN層104とGaN層106との間にAlGaN層105が挿入された構成とする。

(もっと読む)

化合物半導体装置の製造方法

【課題】 スイッチMMICに採用するHEMTは、ゲート電極となるPtの蒸着膜厚を40Å〜60Åにするとよい。しかし、膜厚数十Åの蒸着金属の測定については、通常の触針式の段差計では測定不可能である。膜厚を正確に測定するにはTEM観察しか方法がないが、その準備として試料作成に非常に時間を要する。また1回の測定で数十万円の費用が発生する。

【解決手段】 シート抵抗値と実蒸着膜厚の一義的な相関データを算出しておき、モニターウエハのシート抵抗値からモニターウエハの実蒸着膜厚を換算し、蒸着機を管理する。管理された蒸着機によってHEMTを形成することにより、TEM観察を行うことなく、日常管理において頻繁にかつ迅速に蒸着金属の膜厚を管理できる。

(もっと読む)

半導体素子のトランジスタ及びその製造方法

【課題】 オン状態の挿入損失が減少し、オフ状態の隔離度が増加するように、エピ基板の構造を最適化する。

【解決手段】 本発明に係る半導体素子のトランジスタは、半絶縁基板上に、緩衝層、第1のシリコンドーピング層、第1の伝導層、前記第1のシリコンドーピング層と異なるドーピング濃度を有する第2のシリコンドーピング層及び第2の伝導層が順次に積層されたエピ基板と、前記第1のシリコンドーピング層の所定深さまでに浸透するように前記第2の伝導層の両側上に形成され、オーム接触を形成するソース電極及びドレイン電極と、前記ソース電極及び前記ドレイン電極間の第2の伝導層上に形成され、前記第2の伝導層とコンタクトを形成するゲート電極とを備え、前記ゲート電極と前記ソース電極及び前記ドレイン電極の間は、絶縁膜により電気的に絶縁され、前記ゲート電極の上部が前記ソース電極及び前記ドレイン電極の少なくとも一方に部分的に重なって形成される。

(もっと読む)

半導体発光素子

【課題】活性層内に電子を閉じ込めるための電子障壁を越えてオーバーフローする電子を低減することで、しきい電流が小さく、微分効率の高い、良好な特性を備える半導体発光素子を提供する。

【解決手段】活性層20を構成するバリア層のうち、最もp側に位置するバリア層である最終バリア層1のバンドギャップを、バリア層2のバンドギャップより小さくする。最終バリア層1としてバリア層2と同じバンドギャップの材料を用いる場合に比べて電子障壁層3とのバンド不連続量(電子障壁)が大きくできる。その結果、電子障壁を越えてオーバーフローする電子を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】HEMTのゲートのリセスエッチングのマスクとなる窒化膜は、所定の耐圧を確保するためキャップ層をサイドエッチすることにより、ひさし部が形成される。このひさし部を除去するためプラズマエッチングを行うと、このとき露出している動作領域表面の障壁層にダメージを与え、オン抵抗が増大する問題があった。

【解決手段】キャップ層の下層として安定層を設け、ひさし部のプラズマエッチング時においてプラズマにさらされる動作領域表面は、安定層が露出するようにしておく。これにより動作領域表面は安定層で保護され、ひさし部をプラズマエッチングにより除去しても、チャンネルがプラズマダメージを受けることは無いため、オン抵抗が増大するのを防ぐことができる。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

半導体装置およびその製造方法

【課題】オーミック電極である第1ソース電極と第1ドレイン電極は、ゲートのリセスエッチングのためのマスクとしての窒化膜を開口して形成されるため、窒化膜との間に隙間Gが形成される。このためガルバニック効果によりオーミック電極端部のキャップ層がエッチングされ、オン抵抗が増大する問題がある。

【解決手段】初期窒化膜を全面除去した後、オーミック電極を形成し、キャップ層とオーミック電極の段差を密着して覆う第1窒化膜を形成する。ゲートのリセスエッチングは、第1窒化膜をマスクとして行うと、オーミック電極の端部に隙間Gが形成されない。従って、ガルバニック効果を抑制し、オン抵抗の増大を抑制できる。

(もっと読む)

半導体装置

【課題】基板強度を保持しつつオン抵抗を低減し得る半導体装置を提供する。

【解決手段】網目状の凸部により形成された複数の凹部を裏面に有し、第1の不純物濃度を有する半導体からなる支持体21と、前記支持体の前記裏面に対向する表面に形成され、前記第1の不純物濃度よりも低い第2の不純物濃度を有する半導体層3と、前記半導体層3に形成された半導体素子とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】AlGaN層の表面を平坦とし、かつ、AlGaN/GaN界面に存在する二次元電子ガスにダメージを与えない半導体装置の製造方法を提供する。

【解決手段】先ず、サファイア又は炭化珪素で形成される支持基板12を用意して、支持基板上にバッファ層14を堆積させる。次に、支持基板及びバッファ層を900℃以上1100℃以下に設定された成長温度に保持した状態で、バッファ層上に、GaN層16及びAlGaN層20を順次に積層してGaN半導体基板10を形成する。GaN半導体基板を形成する工程に引き続いて、GaN半導体基板を500℃以上成長温度以下の温度に保持した状態で、AlGaN層の上側表面28上に、表面保護膜としてAlN層30を形成する。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】半導体素子及びその製造方法を開示する。

【解決手段】この半導体素子は単一金属膜をフッ素及び/または炭素で選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極を有する。

(もっと読む)

ショットキーバリアダイオード及びダイオードアレイ

【課題】耐圧が高く且つオン抵抗が低い上に、チップ面積が小さいショットキーバリアダイオード及びダイオードアレイを実現できるようにする。

【解決手段】導電性のシリコン基板2の上にバッファ層3と、アンドープの窒化ガリウムである第1の半導体層4と、アンドープのアルミニウム窒化ガリウムである第2の半導体層5とが順に形成されている。第2の半導体層5の上には、ショットキー電極6とオーミック電極7とが互いに間隔をおいて形成されている。第2の半導体層5と第1の半導体層4とバッファ層3とを貫通して、n+−Si基板2に達するビア8が形成されており、オーミック電極7とn+−Si基板2とは電気的に接続されている。n+−Si基板2の裏面には裏面電極1が形成されており、オーミック電極7は基板2の裏面に引き出されている。

(もっと読む)

半導体発光素子及びその製造方法

半導体発光素子は、発光機能を有する半導体基板(2)とアノード電極(3)とオーミックコンタクト領域(4)と合金化阻止用の光透過層(20)と金属光反射層(5)と導電性支持基板(8)とを有する。前記光透過層(20)は絶縁性を有する材料から成り、前記半導体基板(2)と前記金属光反射層(5)との合金化を阻止する機能を有する。オーミックコンタクト領域(4)は光透過可能な厚みに形成される。前記半導体基板(2)から発生した光は前記光透過層(20)を通って前記金属光反射層(5)で反射し、且つ前記オーミックコンタクト領域(4)を通って前記金属光反射層(5)で反射する。この結果、半導体発光素子の発光効率が高くなる。 (もっと読む)

CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成するための方法

【課題】 位置ずれの問題を克服する新規のデュアルFUSIゲート形成プロセスを提供する。

【解決手段】 1つのリソグラフィ段階しか必要としない、CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成する方法であり、本方法は、半導体基板(252)の中の第1のウェル領域(253)、第1のウェル領域(253)の中の第1のソース/ドレイン・シリサイド・エリア(266)、及び第1のソース/ドレイン・シリサイド・エリア(266)から分離された第1のタイプのゲート(263)を有する第1のタイプの半導体デバイス(270)を形成するステップと、半導体基板(252)の中の第2のウェル領域(254)、第2のウェル領域(254)の中の第2のソース/ドレイン・シリサイド・エリア(256)、及び第2のソース/ドレイン・シリサイド・エリア(256)から分離された第2のタイプのゲート(258)を有する第2のタイプの半導体デバイス(280)を形成するステップと、第2のタイプの半導体デバイス(280)の上に第1の金属層(218)を選択的に形成するステップと、第2のタイプのゲート(258)のみの上で第1のフルシリサイド(FUSI)ゲート形成を行うステップと、第1及び第2のタイプの半導体デバイス(270、280)の上に第2の金属層(275)を堆積させるステップと、第1のタイプのゲート(263)のみの上で第2のFUSIゲート形成を行うステップとを含む。

(もっと読む)

ショットキーバリアダイオード及びそれを用いた集積回路

【課題】ショットキーバリアダイオード(SBD)の耐圧が低下することを防止すると共に、複数のSBDのそれぞれの電極に異なる電圧を印加できるようにして、高耐圧のSBD及び高耐圧のSBDが集積化されたコンパクトな集積回路を実現できるようにする。

【解決手段】基板1の上には、厚さが100nmの窒化アルミニウムからなるバッファ層2と、厚さが1500nmのアンドープの窒化ガリウムからなる第1の半導体層3と、厚さが25nmのアンドープのアルミニウム窒化ガリウムからなる第2の半導体層4とが形成されている。第2の半導体層4の上には、ショットキー電極6とオーミック電極7とが間隔をおいて形成されている。ショットキーバリアダイオードの周縁部には、ショットキー電極6とオーミック電極7とを囲むように高抵抗領域5が設けられている。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子装置

【課題】 HBT(Hetero-junction Bipolar Transistor)の特性を向上させる。

【解決手段】 HBT(Q)は、化合物からなる基板の主面上に順に形成されたコレクタ層、ベース層、エミッタ層およびそれぞれに電気的に接続されたコレクタ電極9a、ベース電極8、エミッタ電極7を有し、さらにエミッタ電極7とエミッタ層との間に形成されたエミッタコンタクト層6を有する。その基板の主面に平行な平面において、エミッタコンタクト層6およびエミッタ電極7の平面形状は、ベース電極8を囲う略環状形状を有し、エミッタコンタクト層6の最小寸法Leは、1.2μm以上である。

(もっと読む)

半導体センサ及びその製造方法

本発明は、半導体センサ及びその製造方法に関し、電子移動度が高く、シート抵抗が比較的大きなInSbやInAs膜をSi基板上に形成することを可能にし、高感度で低消費電力の優れた素子を工業的に提供可能にする。(111)Si基板(1)上に、まず、Ga、Al、In、As、Sb,Pのうち少なくとも2種以上の元素から構成された第一化合物半導体層(2)を形成し、この第一化合物半導体層(2)の上に、第二化合物半導体層(3)として、InSbやInAsを形成することにより、1μm前後の膜厚で高電子移動度であり、かつ、高抵抗の膜が得られる。さらに、得られた薄膜を用いてホール素子を形成し、高感度で比較的高抵抗の素子形成が可能となる。  (もっと読む)

(もっと読む)

CMOS技術における自己整合デュアル・サリサイド形成のための方法

【課題】 従来のデュアル・サリサイド処理における典型的な位置ずれの問題を克服する、新規なデュアル・サリサイド・プロセスを提供すること。

【解決手段】 相補型金属酸化膜半導体(CMOS)デバイスを製作する方法であって、本方法は、第1のタイプの半導体デバイス(130)を収容するために半導体基板(102)の中に第1のウェル領域(103)を形成するステップと、第2の半導体デバイス(140)を収容するために半導体基板(102)の中に第2のウェル領域(104)を形成するステップと、第1のタイプの半導体デバイス(130)をマスク(114)で遮蔽するステップと、第2のタイプの半導体デバイス(140)の上に第1の金属層(118)を堆積させるステップと、第2のタイプの半導体デバイス(140)の上で第1のサリサイド形成を行うステップと、マスク(114)を除去するステップと、第1及び第2のタイプの半導体デバイス(130、140)の上に第2の金属層(123)を堆積させるステップと、第1のタイプの半導体(130)の上で第2のサリサイド形成を行うステップとを含む。本方法は、1つのパターン形成段階しか必要とせず、また、異なるデバイスの上に異なるシリサイド材料を形成するプロセスを単純化するため、パターンの重なりを排除することができる。

(もっと読む)

へテロ接合型のIII−V族化合物半導体装置とその製造方法

【課題】 ヘテロ接合型のIII-V族化合物半導体装置において、オフ時のリーク電流を抑制するとともにオン時の抵抗を低減する。

【解決手段】 GaNの下層46と、その下層46にヘテロ接合されており、下層46のバンドギャップよりも大きなバンドギャップを有するAlGaNの上層48と、上層48の表面の一部に形成されているソース電極54と、上層48の表面の他の一部に形成されているゲート電極52を備えており、前記下層46は、ヘテロ接合界面と平行な面内において、結晶欠陥高密度領域72と結晶欠陥低密度領域が分布しており、ソース電極54は、結晶欠陥低密度領域に対向する領域内に形成されており、ゲート電極52は、結晶欠陥高密度領域72に対向する領域に形成されているIII-V族化合物半導体装置。

(もっと読む)

1,361 - 1,380 / 1,477

[ Back to top ]