Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

1,341 - 1,360 / 1,477

化合物半導体デバイス

【課題】 エネルギー損失が少なく、高効率かつ破壊電圧が高い化合物半導体デバイスを提供する。

【解決手段】 結晶面方位{111}、キャリア濃度1016〜1021/cm3(≒抵抗率1〜0.00001Ωcm)、伝導型n型のSi単結晶基板上2に、厚さ0.05〜2μm、キャリア濃度1016〜1021/cm3、伝導型n型の3C−SiC単結晶バッファー層3と、厚さ0.01〜0.5μmの六方晶InwGaxAl1-w-xN単結晶バッファー層4(0≦w<1、0≦x<1、w+x<1)と、厚さ0.1〜5μm、キャリア濃度1011〜1016/cm3(≒抵抗率1〜100000Ωcm)、伝導型n型の六方晶InyGazAl1-y-zN単結晶層5(0≦y<1、0<z≦1、y+z≦1)とを順次積層し、かつ、Si単結晶基板2の裏面に裏面電極6、および、六方晶InyGazAl1-y-zN単結晶層5の表面に表面電極7を形成する。

(もっと読む)

金属ベーストランジスタおよびそれを用いた発振器

【課題】 テラヘルツ帯の分光ならびに透視装置を小型・低コストで実現する上で、これに用いられる発振器を小型・低コスト化することが最重要課題であった。

【解決手段】 発振器の能動素子に金属ベーストランジスタを採用し、その最大発振周波数を数THzにまで向上するために、電子の飽和速度の高いInN或いはInNを主成分とする材料をコレクタに用いた。特性を再現性よく得るために、コレクタとベースの界面にInGaNを挿入することが有用である。本発明の金属ベーストランジスタを用いてテラヘルツ帯の発振を可能とする発振器を構成することが可能である。又、この発振器を信号源あるいは局所発振器の少なくとも一つに適用した分光装置を提供する。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 半導体層間の接合の端面におけるリーク電流を抑え、かつ、水分の侵入や放熱不足の問題を解消できるパッシベーション膜を備えたヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にメサ構造に加工した半導体層2〜6を形成する。エミッタメサおよびベース・コレクタメサの端部に凹部11および12を形成し、これらの凹部にそれぞれ絶縁性有機膜13および14を形成して、エミッタ層5の端面とベース層4との界面、およびベース層4とコレクタ層3との界面を絶縁性有機膜で被覆する。さらに、半導体層2〜6を被覆する緻密な無機パッシベーション膜15を、例えばプラズマCVD法による窒化シリコン膜によって形成し、開口部に電極7〜9を形成する。HBT10では、接合の端面が絶縁性有機膜13および14によって被覆されているので、接合部にプラズマダメージが生じることはない。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 積層方向における電極位置の高低差を緩和或いは解消し易く、製造工程の増加や生産性の低下を抑え易く、電気的特性の悪化を招かない構造を有するヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 サブコレクタ層、コレクタ層、ベース層及びエミッタ層が、この順に基板上に積層されてなるHBTにおいて、

ベース層14と同レベル位置のベース層構成材料層14a上、コレクタ層13と同レ ベル位置のコレクタ層構成材料層13a上、コレクタ層13の途中レベル位置のコレク タ層構成材料層13a上、又は、エミッタ層15又はエミッタキャップ層16と同レベ ル位置のエミッタ層構成材料層15a上又はエミッタキャップ層構成材料層16a上に コレクタ電極7が形成され、

このコレクタ電極7とサブコレクタ層12とが、オーミックアロイ法によって形成さ れた導電領域21を介して電気的に接続されていること

を特徴とする、HBT10a。

(もっと読む)

半導体装置

【課題】エミッタ、ベース、コレクタ電極を同一にすることで大幅な工程削減と微細化を実現するとともに、ヘテロ接合型バイポーラトランジスタ特性の安定化を実現した半導体装置を提供する。

【解決手段】エミッタ構造、ベース構造、コレクタ構造の1E19/cm3以上のn++InGaAs層104,408、p+GaAs層302のノンアロイ層を配することで各電極構造を同一構造化することが可能となり、また各電極構造の各半導体層のキャリアの高濃度と低濃度もしくは混晶比の連続性を持たせることによりヘテロ接合型バイポーラトランジスタ特性の安定化が図れる。

(もっと読む)

ゲート誘電体上にゲート金属または他の導体材料または半導体材料を電着するための方法(ゲート誘電体貫通電流を用いた電気化学処理によるゲート・スタック技術)

【課題】 ゲート誘電体等の誘電体の上に直接ゲート金属または他の導体材料または半導体材料を電気めっきするための方法を提供する。

【解決手段】 この方法は、基板、誘電体の層、および電解液または溶融物を選択することを含み、基板、誘電体層、および電解液または溶融物の組み合わせによって、基板から誘電体層を介して電解液または溶融物へと電気化学電流を流すことができる。また、誘電体貫通電流を用いて誘電体の電気化学的な変更を行うための方法も提供する。

(もっと読む)

窒化ガリウム半導体デバイス用のパッケージ

【課題】電力用半導体デバイスのための改善されたパッケージを提供すること。

【解決手段】パッケージ化された半導体デバイスはダイ105装着用支持体104を含み、ダイの底面がこのダイ装着用支持体の最上面に取り付けられ、間隔を置かれた複数の外部導体101,102,103がこの支持体から延び、前記間隔を置かれた外部導体のうちの少なくとも1つがその一方の端部にボンド・ワイヤ用ポスト110を有し、このボンド・ワイヤ用ポストと、複数のメサの最上面へのコンタクト領域との間にボンディング・ワイヤ108が延びる。

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

エピタキシャル基板および半導体素子

【課題】逆方向耐圧を向上可能な構造を有するIII族窒化物半導体素子を提供する。

【解決手段】ショットキダイオード11では、p型の窒化ガリウム支持基体13は、第1の面13aと第1の面の反対側の第2の面13bとを有しており、1×1017cm−3を超えるキャリア濃度を示す。p型の窒化ガリウムエピタキシャル層15は、第1の面13a上に設けられている。オーミック電極17は、第2の面13b上に設けられている。ショットキ電極19は、窒化ガリウムエピタキシャル層15に設けられている。窒化ガリウムエピタキシャル層15の厚さD1は5マイクロメートル以上1000マイクロメートル以下である。また、窒化ガリウムエピタキシャル層15のキャリア濃度は、1×1014cm−3以上1×1017cm−3以下である。

(もっと読む)

化合物半導体装置

【課題】 ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】 化合物半導体層100上にショットキー接合してなるゲート電極101において、化合物半導体層100とショットキー障壁を形成するNi層41と、低抵抗金属層42との間に、低抵抗金属層42の金属の化合物半導体層100への拡散を抑止するTixW1-xN(0<x<1)からなる拡散防止層を設けるようにして、ゲート電極のリーク電流の増大を抑制する。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】製造工程において電子ビーム露光を必要としないT字型ゲート電極を有するIII−V族窒化物系電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、複数の半導体膜が積層された第1の半導体層14と、第1の半導体層14の上に形成された第2の半導体層15とを備えている。第2の半導体層15の上には、互いに間隔をおいてソース電極17及びドレイン電極18が形成されている。第2の半導体層15のソース電極17及びドレイン電極18に挟まれた領域には、側壁に絶縁膜16が形成され、第1の半導体層14を露出する開口部が形成されている。開口部には、絶縁膜16と接し且つ開口部の底面において第1の半導体層14と接するゲート電極19が形成されている。

(もっと読む)

n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

窒化物系半導体素子及びその製造方法

窒化物系半導体素子を形成するためにp型不純物がドープされ且つ十分な導電性を有するp型シリコン基板(1)を用意する。シリコン基板(1)の上に、AlNから成る第1のバッファ層(11)、n−InGaNから成る第2のバッファ層(12)、n−GaNから成るn型窒化物半導体層(13)、活性層(14)、及びp−GaNから成るp型窒化物半導体層(15)を順次にエピタキシャル成長させる。エピタキシャル成長時の加熱処理によって第1の層(11)のAl、第2の層12のGa及びInがp型シリコン基板(1)に拡散してp型シリコン基板(1)とバッファ層(11)との間に合金層(2)が形成される。Al,Ga,Inは合金層(2)に隣接するp型シリコン基板(1)の内部にも拡散するが、Al,Ga,Inはシリコンに対してp型不純物として機能し且つシリコン基板(1)がp型であるので、シリコン基板(1)中にpn接合が形成されない。この結果、窒化物系半導体素子の駆動電圧が低くなる。  (もっと読む)

(もっと読む)

半導体素子および電界効果トランジスタ

【課題】 良好なショットキー特性を有する電極を備えた半導体素子を提供する。また、良好なショットキー特性を有するゲート電極を備えた電界効果トランジスタを提供する。

【解決手段】 n型GaN層3の上に形成されたショットキー電極6は、WNx層4を有し、n型GaN層3とWNx層4とが接触する面において、n型GaN層3の結晶面は六方晶の(0001)面であり、WNx層4の結晶面は(111)面に配向している。WNx層4は、Zr、Ha、Nb、Ta、MoおよびWよりなる群から選ばれる少なくとも1種の元素と、窒素および炭素の少なくとも一方の元素とからなる塩化ナトリウム型構造の電極層であればよい。また、電極層の格子定数は、n型GaN層3におけるa軸格子定数を2(1/2)倍した値の0.95倍〜1.05倍であることが好ましい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 パッド電極下に能動層が配置されている場合においても、パッド電極下における密着性を確保しつつ、バリアメタル構造を能動面上に安定して形成できるようにする。

【解決手段】 不純物拡散層5a、5bの表面が覆われるようにして層間絶縁膜6上にバリアメタル膜8を形成し、フォトリソグラフィー技術を用いることにより、開口部7が覆われるようにしてパッド電極16下に配置されるバリアメタル膜8の表面を露出させるレジストパターンRを形成し、レジストパターンRをマスクとして、バリアメタル膜8をエッチングすることにより、パッド電極16下に配置される層間絶縁膜6上のバリアメタル膜8を除去し、バリアメタル膜8を介してゲート電極4および不純物拡散層5a、5bに接続された配線層9を層間絶縁膜6上に形成し、ゲート電極4および不純物拡散層5a、5b上に配置されたパッド電極16を形成する。

(もっと読む)

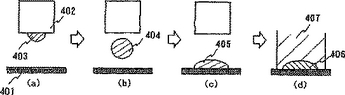

液滴吐出装置、パターンの形成方法、および半導体装置の製造方法

本発明では液滴吐出装置から吐出された液滴が基板に着弾した後の位置制御を改善することが可能なパターンの作製方法を提供する。また着弾後の液滴位置精度を改善することが可能な液滴吐出装置を提供する。更には、本発明の液滴吐出装置を用いた半導体装置の製造方法を提供する。

本発明は、吐出部から吐出された液滴、又は液滴を着弾する基板にレーザ光を照射して、液滴の着弾位置を制御することを特徴とする。本発明によりフォトリソグラフィー工程を用いることなくパターンを形成することが可能である。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】従来のCMPプロセスを用いることなく、高アスペクト比の開口を有する接続孔にも良好な埋め込みが可能である半導体装置の作製方法を提供する。また、従来よりも少ない工程数で、配線形成が可能な方法を提供することを目的とする。更には、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】複数の空孔を有する絶縁膜表面に撥水表面を有する膜を形成し、撥水表面を有する膜の一部に光を照射して、親水表面を有する領域を形成した後、親水表面を有する領域に導電性粒子を有する液状物質を吐出し、焼成して導電膜を形成することを特徴とする。

(もっと読む)

ナノチューブ/ナノワイヤFETのための自己整合プロセス

【課題】 ナノチューブ及びナノワイヤのような一次元ナノ構造体を含むCMOSデバイスを製造するための自己整合プロセスを提供すること。

【解決手段】 半導体構造体は、少なくとも1つのゲート領域が上に配置され、少なくとも1つのゲート領域が少なくとも1つの一次元ナノ構造体の層を含む、基板と、基板の表面上に配置され、少なくとも1つの一次元ナノ構造体の層の縁と整合される、金属カーバイド・コンタクトと、を含む。

(もっと読む)

1,341 - 1,360 / 1,477

[ Back to top ]