Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

1,401 - 1,420 / 1,477

電極形成方法

【課題】透光性が高く、低抵抗の透光性電極の製造方法。

【解決手段】半導体発光素子100は、サファイア基板上にバッファ層102、ノンドープGaN層103、高キャリヤ濃度n+層104、n型層105、発光層106、p型層107、p型コンタクト層108を順に積層して形成され、少なくとも酸素が存在する雰囲気下で電子線蒸着法又はイオンプレーティング法により形成され、後に焼成されて形成されたITOから成る透光性電極110を有する。

(もっと読む)

エピタキシャル基板および半導体素子

【課題】逆方向耐圧を向上可能な構造を有するIII族窒化物半導体素子を提供する。

【解決手段】ショットキダイオード11で窒化ガリウム支持基体13は、第1の面13aと第1の面の反対側の第2の面13bとを有しており、1×1018cm−3を超えるキャリア濃度を示す。窒化ガリウムエピタキシャル層15は、第1の面13a上に設けられている。オーミック電極17は、第2の面13b上に設けられている。ショットキ電極19は、窒化ガリウムエピタキシャル層15に設けられている。窒化ガリウムエピタキシャル層15の厚さD1は5マイクロメートル以上1000マイクロメートル以下である。また、窒化ガリウムエピタキシャル層15のキャリア濃度は、1×1014cm−3以上1×1017cm−3以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】 基板浮遊効果を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】 絶縁層と、前記絶縁層の上方に形成された半導体層と、前記半導体層の上方に形成されたゲート絶縁層と、前記ゲート絶縁層の上方に形成されたゲート電極と、前記半導体層に形成されたソース領域およびドレイン領域と、前記ゲート絶縁層の下方に形成されたボディ領域と、前記半導体層において、前記ボディ領域に対して前記ソース領域側に形成され、かつ、前記ボディ領域とショットキー接合する複数のショットキー接合領域と、を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】従来と同等の駆動力を確保しつつ、ヘテロ界面で生じる漏れ電流を低減することが可能な高耐圧電界効果トランジスタを容易に製造する。

【解決手段】基板1とドレイン領域2からなる半導体基体の一主面側に第二のヘテロ半導体領域形成用半導体層400を積層する工程と、所定の開口14を有するマスク層9をマスクとして用いて、第二のヘテロ半導体領域形成用半導体層400を選択的にエッチングして第二のヘテロ半導体領域4を形成する工程と、マスク層9を有した状態で、第一のヘテロ半導体領域形成用半導体層300を積層する工程と、第一のヘテロ半導体領域形成用半導体層300を選択的にエッチングして第一のヘテロ半導体領域3を形成する工程と、第一のヘテロ半導体領域3並びに半導体基体に接するようにゲート絶縁膜5を形成する工程を有する。

(もっと読む)

GaN系半導体集積回路

【課題】 小型化が可能で、発熱量の少ない大電力用途の半導体集積回路を提供する。

【解決手段】 種類が互いに異なる複数のGaN系半導体素子を一つの基板上に集積したGaN系半導体集積回路において、前記GaN系半導体素子には、ショットキーダイオード及び電界効果トランジスタが含まれ、該ショットキーダイオードを構成する所定の幅を有するGaN系半導体層上に、前記所定の幅よりも狭い幅でショットキー接合する第1アノード電極と、前記第1アノード電極に接触する部分以外の前記GaN系窒化物半導体層上にショットキー接合すると共に前記第1アノード電極に電気的に接続する第2アノード電極とを備え、前記第1アノード電極と前記GaN系半導体層との間で形成されるショットキーバリアの高さが前記第2アノード電極と前記GaN系半導体層との間で形成されるショットキーバリアの高さよりも低いことを特徴とする。

(もっと読む)

半導体装置

【課題】ゲート電極近傍のヘテロ接合界面で生じる漏れ電流を低減する。

【解決手段】第一導電型の基板1とドレイン領域2からなる半導体基体と、該半導体基体の一主面に接し、該半導体基体とはバンドギャップが異なるヘテロ半導体領域3と、ヘテロ半導体領域3と前記半導体基体との接合部にゲート絶縁膜5を介して形成されたゲート電極6と、ヘテロ半導体領域3と接続されたソース電極6と、前記半導体基体とオーミック接続されたドレイン電極7と、少なくともヘテロ半導体領域3と前記半導体基体とゲート絶縁膜5とが互いに接する領域から所定距離離れたドレイン領域2中に、第二導電型のウェル領域4とを有し、ウェル領域4内に空乏層が形成されない場合の該ウェル領域4内のフリーキャリア濃度が、該ウェル領域4内に空乏層が形成される場合の空乏層内の空間電荷濃度よりも小さくなっている。

(もっと読む)

超高周波半導体素子

【課題】半導体素子測定のための時間と費用を減らし、また、半導体素子モデリング過程での時間と費用を減らし、超高周波単一チップ集積回路設計時間の短縮と正確な設計を実現する。

【解決手段】半導体素子で測定用パッドの形成とデ・エンベディング過程を省略し、デ・エンベディングされた高周波半導体素子における入出力端の測定パッドの代わりに拡張電極を代置することにより、電極と測定パッド部分で発生する不連続特性を除去して超高周波単一チップ集積回路の設計時に必要なデ・エンベディング過程を省略する。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

電界効果トランジスタ

T字型ゲート(10)を有する電界効果トランジスタにおいて、ゲートはネック部(16)と該ネック部から張り出したTバー部(18)とを有し、ネック部(16)は複数の相隔てられたピラー(20)を有する。ネック部を複数の相隔てられたピラーから形成することにより、ゲートとチャネルとの接触面積すなわち“実効ゲート幅”が狭くされる一方で、Tバー部(18)がピラー(20)を橋渡しすることによりゲートを通じての電気的な連続性を確保している。これにより入力ゲート容量が低減され、向上されたデバイス性能を備えたFETがもたらされる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

金属層を有する半導体素子の形成方法

半導体基板(12)上に形成された金属酸化物(14)上に金属層(24)を形成する。金属層の所定の限界寸法を決定する。第1エッチングにより金属層を下方へと金属酸化物に至るまでエッチングし、金属層の側壁にフーティング(26)を形成する。金属酸化物に対し選択的である第2エッチングにより、所定の限界寸法を狙ってフーティングを除去する。一実施形態において、金属層上に導電層(22)を形成する。金属層と接触している部分を残存させつつ、導電層の大部分をエッチングする。次に、金属層と接触している残余部分を、金属層に対して選択的な化学物質を用いてエッチングする。  (もっと読む)

(もっと読む)

半導体素子とその製造方法、及び電子部品ユニット

【課題】 高品質の半導体素子を提供する。

【解決手段】 基板と、基板上方に形成された複合接合層と、複合接合層上方に形成された第1の電極と、第1の電極上を含む領域に形成された半導体層と、半導体層上の一部の領域に形成された第2の電極とを有し、複合接合層は、基板、及び第1の接合層を含む支持基板と、半導体層、第1の電極、及び第2の接合層を含む半導体積層構造とを接合するときに形成され、第1または第2の接合層は共晶成分を含み、支持基板及び半導体積層構造の少なくとも一方は、拡散材料を含む拡散材料層を含み、複合接合層は、第1または第2の接合層の一方に含まれる共晶成分が他方の接合層と混合して第1の混合体を形成し、更に第1の混合体と拡散材料層に含まれる拡散材料とが混合し、第1の混合体の溶融温度より高い溶融温度を有する第2の混合体を形成することにより形成される半導体素子を提供する。

(もっと読む)

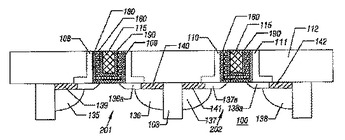

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

ヘテロバイポーラ・トランジスタ(HBT)およびその製作方法(BiCMOS技術におけるコレクタ形成方法)

【課題】デバイスのサブコレクタ上のシャロー・トレンチ分離領域の下部に埋め込み高融点金属シリサイド層を設けることによりコレクタ抵抗Rcを低下させる、高速BiCMOS用途用のヘテロバイポーラ・トランジスタ(HBT)、および、このようなHBTを製作する方法を提供する。

【解決手段】本発明のHBTは、少なくともサブコレクタ(13)を含む基板(12)と、サブコレクタ上に位置する埋め込み高融点金属シリサイド層(28)と、埋め込み高融点金属シリサイド層の表面上に位置するシャロー・トレンチ分離領域(30)とを含む。また、本発明の方法は、デバイスのサブコレクタ上のシャロー・トレンチ分離領域の下部に埋め込み高融点金属シリサイド層を形成するステップを含む。

(もっと読む)

窒化物系半導体装置

【課題】高耐圧/低オン抵抗の窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体装置は、窒化物系半導体から実質的になる第1半導体層1と、第1半導体層上に配設されたノンドープ若しくは第1導電型の窒化物系半導体から実質的になる第2半導体層2と、を有する。第1及び第2半導体層はヘテロ界面を形成する。第2半導体層上にゲート電極11が配設される。ゲート電極を間に挟むように第2半導体層の表面内に第1及び第2トレンチ3、4が形成される。第1及び第2トレンチの表面内に、第1及び第2半導体層よりも低抵抗の拡散層から実質的になる第1導電型の第3及び第4半導体層5、6が形成される。第3及び4半導体層にソース電極15及びドレイン電極16が電気的に接続される。

(もっと読む)

発光ダイオード

【課題】コンタクト層と透明電極とのオーミックコンタクトを容易に取ることができる発光ダイオードを提供する。

【解決手段】発光ダイオードは、p型AlGaInP活性層15、透明電極用p型GaAsコンタクト層17およびITO透明電極110を備えている。このp型GaAsコンタクト層17のキャリア濃度は1.0×1019cm-3に設定されている。

(もっと読む)

半導体基板、半導体素子、半導体素子の製造方法及び半導体基板の製造方法

【課題】貫通転移などの欠陥やひび割れが少なく高品質窒化物結晶層をサファイア基板上に均一に形成することにより、高性能な窒化物系III−V族化合物半導体素子、その製造方法及びその製造に用いるエピタキシャル成長基板及びその製造方法を提供する。

【解決手段】基板11と、この基板11上のバッファ層(12,13)と、このバッファ層(12,13)上の、周期表第4及び第5周期に含まれるIV族元素を濃度1×1017cm-3以上、1×1019cm-3以下で含む、基板11とは格子定数の異なる窒化物系III−V族化合物半導体単結晶層からなる欠陥低減層16とを備える。

(もっと読む)

HEMT装置及び製造方法

【課題】

【解決手段】基板と垂直な縦壁を備えた柱部を有するHEMT型装置。柱部はGaN等の絶縁性半導体材料からなる。柱部の側面上には、柱部の絶縁性材料のそれより大きいバンドギャップを有するAlGaN等の半導体材料からなるバリア層が配置される。電子流は2つの材料の界面の狭いチャネルに制限される。適当なソース、ドレイン及びゲートコンタクトがHEMTの動作のため含まれる。

(もっと読む)

半導体素子のための非活性化保護リング

【課題】 半導体素子、特にショットキーダイオードのような金属対半導体整流接合を組み込む半導体素子を提供する。

【解決手段】 保護リングは、ショットキー接合又はショットキーダイオードの一部である半導体領域に形成される。保護リングは、高抵抗領域を形成するために、半導体コンタクト層を完全にアニール処理することなく半導体コンタクト層内へのイオン注入によって形成される。保護リングは、層のエッジ部か又は代替的に層のエッジ部からある一定距離を離して位置することができる。ショットキー金属接点は、層の上に形成され、ショットキー接点のエッジ部は、保護リングの上に配置される。

(もっと読む)

半導体素子の製造方法

【課題】エピタキシャル成長法により半導体層を形成する際の加工寸法誤差を少なくすることができる半導体素子の製造方法を提供する。

【解決手段】有機金属化合物を含有する感光性ペーストを塗布した後ベークして、基板1上に感光性マスク層を形成する。この感光性マスク層をフォトリソグラフィによりパターニングし、更に酸化処理又は還元処理して、基板1上に金属酸化物を主成分とするエピタキシャルマスク4を形成する。そして、基板1表面のエピタキシャルマスク4が形成されていない領域上にダイヤモンドをエピタキシャル成長させて、半導体ダイヤモンド層5a及び5bを形成する。エピタキシャルマスク4を除去した後、半導体ダイヤモンド層5a及び5b上に夫々ソース電極7及びドレイン電極8を形成すると共に、基板1表面におけるチャネル領域上にゲート絶縁膜6を介してゲート電極9を形成する。

(もっと読む)

1,401 - 1,420 / 1,477

[ Back to top ]