Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

241 - 260 / 766

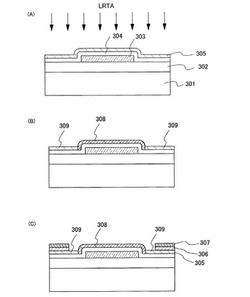

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供する。

【解決手段】基板301上にゲート電極303を形成し、ゲート電極303を覆ってゲート絶縁膜304を形成し、ゲート絶縁膜304上に酸化物半導体膜305を形成し、酸化物半導体膜305上に第1の導電膜306及び第2の導電膜307を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも加熱処理LRTAにより結晶化した領域308を有する。

(もっと読む)

絶縁性薄膜、絶縁性薄膜の形成用溶液、絶縁性薄膜の製造方法、電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】低温で塗布形成可能で高い絶縁性と誘電率を有し、かつ表面処理可能な絶縁性薄膜の形成用溶液、それを用いて形成した絶縁性薄膜、絶縁性薄膜をゲート絶縁層として用いることで優れた性能を有する電界効果型トランジスタ及びその製造方法並びに画像表示装置を提供する。

【解決手段】基板と、基板上に形成されたゲート電極と、ゲート電極上に形成された高分子と、高分子と酸素原子を介して結合を有し第4族元素、第5族元素、第6族元素、第13族元素、亜鉛、錫のうちから選ばれる金属原子と、金属原子と酸素原子または窒素原子を介して結合を有する有機分子とを含む絶縁性薄膜からなるゲート絶縁層と、ゲート絶縁層上に離間して形成されたソース電極及びドレイン電極と、ソース電極及びドレイン電極間に形成された半導体と、を備えることを特徴とする電界効果型トランジスタ。

(もっと読む)

薄膜半導体デバイス及びその製造方法

【課題】活性層と半導体層との接触面をホモ接合、あるいはホモ接合に限りなく近づけて、界面のバンド障壁を防止して大きなオン/オフ比を得ることができ、かつ製造コスト及び作業工数を低減できる。

【解決手段】薄膜半導体デバイスが、基板1と、基板1上に積層されたソース及びドレイン電極層3と、ソース及びドレイン電極層3上に積層された結晶性シリコンからなる不純物含有半導体層4と、不純物含有半導体層4上に積層された結晶性シリコンからなる活性層5と、活性層5上に積層されたゲート絶縁膜6と、ゲート絶縁膜6の上に積層されたゲート電極7と、を備え、不純物含有半導体層4と活性層5の接合面において、これらの結晶性を連続にする。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

スパッタリングターゲット及び透明導電膜及び透明導電ガラス基板

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、バリヤーメタル等を堆積するための工程が不要な簡略化されたTFT(薄膜トランジスタ)基板の製造方法を提供することである。

【解決手段】 酸化インジウムを主成分とし、W、Mo、Nb、Ni、Pt、Pdからなる第1金属群M1から選ばれた1種又は2種以上の金属又はその金属の酸化物と、ランタノイド系金属からなる第2金属群M2から選ばれた1種又は2種以上の金属の酸化物と、を含むスパッタリングターゲットを利用して、透明導電膜を作製する。この透明導電膜を画素電極として利用することによって、ソース電極7等との接触抵抗を小さく抑えることができる。更に、バリヤーメタル等を用いる必要がなくなったため、バリヤーメタル等を堆積する工程をなくすことができ、TFT基板の製造工程が簡略化される。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】本発明は、ゲート電極とソース電極間の絶縁性を向上させ、ゲート電極とソース電極間のリーク電流を低減させることにより、確実に動作する薄膜トランジスタおよび画像表示装置を提供する。

【解決手段】基板と、前記基板上に形成されたゲート電極と、ゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層および前記ゲート絶縁膜上に形成され、前記半導体層の直上に離間して形成された第1の開口部および第2の開口部を有する保護膜と、前記保護膜上に形成され、前記保護膜の第1の開口部で前記半導体層と電気的に接続されたソース電極と、前記保護膜上に形成され、前記保護膜の第2の開口部で前記半導体層と電気的に接続されたドレイン電極を備える薄膜トランジスタにすることにより、ゲート電極とソース電極との間の絶縁膜の膜厚が実質的に増すこととなり、絶縁性を向上させることができる。

(もっと読む)

トランジスターの製造方法

【課題】アルミニウムやマグネシウムを用いた金属層を形成し400℃程度で熱処理することで、ゲート絶縁層中の不純物を不活性化できるが、当該金属層はヒロックが発生しやすい等、ゲート電極としては適当なものではなく、一旦、当該金属層を除去して、新たにゲート電極を形成する必要がある。この工程では、エッチング雰囲気中にゲート絶縁層を露出させる必要が生じ、ゲート絶縁層の劣化が懸念される。

【解決手段】TiNをスパッタ法にて堆積し、エッチングを行うことで第1ゲート電極106を形成する。そしてアルミニウムを主成分とする触媒金属層108をスパッタリング法等を用いて堆積する。そして、触媒金属層108が堆積された状態で、400℃で1時間熱処理を行う。この熱処理を行うことにより、ゲート絶縁層15と半導体層13との界面の欠陥準位密度を低減させることができた。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

電子デバイスの製造方法

【課題】可撓性を有する電子デバイスを、素子の劣化を防いで簡易に且つ短時間で製造することができる電子デバイスの製造方法を提供する。

【解決手段】支持基板12上に、特定の刺激によって発泡する発泡材を含む剥離層14を形成する工程と、前記剥離層上に電子デバイスを構成する素子を含む構造体11を形成する工程と、前記剥離層に前記特定の刺激を加えることにより該剥離層に含まれる前記発泡材を発泡させ、該剥離層を介して前記構造体を前記支持基板から剥離させる工程と、を有する電子デバイス10の製造方法。好ましくは、発泡材として熱膨張性マイクロカプセル15を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、絶縁膜を構成するSiN膜や半導体膜におけるSiN層との密着性に優れると共に、エッチング時に良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】絶縁膜および/または半導体膜と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、上記SiN膜やSiN層と直接接触する第一層と、該第一層上に形成される第二層とを含み、前記第一層は、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1〜0.5原子%、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1〜0.3原子%含み、かつ前記第一層の膜厚が2〜100nmである表示装置用Cu合金膜。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

配線構造の製造方法、及び配線構造

【課題】製造コストが低い配線構造の製造方法、及び配線構造を提供する。

【解決手段】本発明に係る配線構造の製造方法は、基板10を準備する基板準備工程と、基板10上に半導体層を形成する半導体層形成工程と、半導体層上にドーパントを含むドーパント含有半導体層を形成するドーパント含有半導体層形成工程と、ドーパント含有半導体層の表面を、水分子を含ませた酸化性ガス雰囲気中で加熱することにより、ドーパント含有半導体層の表面に酸化層を形成する酸化層形成工程と、酸化層上に合金層を形成する合金層形成工程と、合金層上に配線層を形成する配線層形成工程とを備える。

(もっと読む)

薄膜トランジスタの製造方法及び表示装置の製造方法

【課題】レジスト組成物を用いたマスクパターンを用いることなくTFT及びそれを用いた表示装置を製造することを目的とする。

【解決手段】ロールツーロール方式により加工処理を行う表示装置の製造方法であって、組成物の吐出口が一軸方向に複数個配列した第1の液滴吐出手段により、可撓性を有する基板上に開口部を有する絶縁性樹脂膜を形成し、組成物の吐出口が一軸方向に複数個配列した第2の液滴吐出手段により、開口部にゲート電極を形成し、プラズマの噴出口が一軸方向に複数個配列したノズル体を備えた被膜形成手段により、ゲート電極および絶縁性樹脂膜上にゲート絶縁膜を形成する。

(もっと読む)

絶縁膜の形成方法、半導体装置の製造方法および半導体装置の製造装置

【課題】半導体を高濃度の硝酸の蒸気および/または溶液に接触させる処理で、短時間に、前記半導体表面に高品質の二酸化シリコン膜の生成を実現する。

【解決手段】被処理用シリコンを濃度70wt%の硝酸の加熱溶液から発生させた蒸気中で数秒、および/またはその加熱硝酸溶液で10分程度接触させて、前記シリコンの表面に膜厚約1.39nmの酸化膜を形成した。この被膜は、リーク電流性能が(1V印加時)0.6A/cm2であり、同膜厚換算のオキシナイトライド膜の以下のレベルを実現できた。

(もっと読む)

薄膜トランジスタおよび該薄膜トランジスタの製造方法

【課題】低温で簡便なプロセスにより形成可能で、移動度、on/off比に優れ、立ち上がり電圧のマイナス側へのシフト、S値劣化、素子間の性能バラツキを改良した、安定性の高い薄膜トランジスタ、および該薄膜トランジスタの製造方法を提供する。

【解決手段】基板106上にゲート電極104、ゲート絶縁層105、ソース電極102、ドレイン電極103、及び半導体層101を有する薄膜トランジスタにおいて、半導体層101が塗布によって形成された酸化物半導体からなり、フッ素化合物含有層107がゲート電極104と半導体層101との間に設けられる。

(もっと読む)

集積型光発電素子及び集積型光発電素子の製造方法

【課題】集積型光発電素子の集電効率を高めること。

【解決手段】複数のセルが直列に接続された集積型光発電素子Iであって、基板10と、基板10上に形成され、隣接する他のセル側に突き出る形状を有する第1のパターニングにより分割された複数の裏面電極層11と、隣接する2個の裏面電極層11を跨ぐように裏面電極層11上に形成され、且つ分割溝15によって分割された複数の半導体層12と、分割された半導体層12上にそれぞれ形成された電極層(透明電極層)13と、少なくとも半導体層12の一部に裏面電極層11を分割する第1のパターニングに倣う形状の第2のパターニングにより形成され、隣接する他のセルから電流を集電する集電端部14と、を有することを特徴とする集積型光発電素子I。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

241 - 260 / 766

[ Back to top ]