Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

181 - 200 / 766

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

パターン形成方法およびパターン形成装置

【課題】 バス配線パターン71aに対して交差するフィンガー配線パターン73aを基板9の主面に形成する際に、フィンガー配線パターン73aを厚膜(高アスペクト比)に形成するとともに、基板9の主面に開始太り3および開始細り4が発生することを防止する。

【解決手段】 基板の主面に形成された第1方向に延びるバス配線パターン71a上に、ノズルからペーストを供給した後、ノズルからのペーストの供給を継続しつつ、ノズルに対して基板9を第1方向と交差する第2方向に沿って移動させて、基板の主面にフィンガー配線パターン73aを形成する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一とする。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

液晶表示装置及びその製造方法

【課題】表示品質と開口率を向上することができる液晶表示装置及びその製造方法を得る。

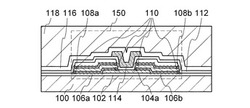

【解決手段】基板上に位置し、相互に交差して画素領域を定義するゲート配線204及びデータ配線と、ゲート配線に接続されるゲート電極202と、ゲート電極上に位置するゲート絶縁膜と、ゲート絶縁膜上に位置するアクティブ層220と、アクティブ層上に位置し、相互に離間されたソース電極234及びドレイン電極236と、アクティブ層及びソース電極間、並びにアクティブ層及びドレイン電極間に位置するオーミックコンタクト層と、アクティブ層上に位置し、ソース電極及びドレイン電極の内側に向かう二つの側面を有し、二つの側面のうち、少なくとも一つは、ソース電極及びドレイン電極の内側間に位置するシールドパターン222と、画素領域に位置し、ドレイン電極に接続される画素電極とを設けた。

(もっと読む)

半導体膜の製造方法、薄膜トランジスタの製造方法および表示装置の製造方法

【課題】半導体薄膜の結晶の不均一性を緩和し、薄膜トランジスタの動作特性を向上させることが可能な半導体膜の製造方法を提供する。

【解決手段】

基板10上に非晶質シリコン膜15Aおよび光熱変換層16をこの順に形成する。光熱変換層16を介して非晶質シリコン膜15Aに第1ビームL1を照射することにより非晶質シリコン膜15Aに高温過熱領域11を形成する。同時に、第2ビームL2を照射することにより高温過熱領域11の走査方向の前後に低温過熱領域12(昇温領域12Aおよび徐冷領域12B)を形成する。非晶質シリコン15Aでは、第1レーザL1の照射により結晶成長が始まり、第2レーザL2の照射により昇温、徐冷されるため、非晶質シリコン15Aの結晶化が緩やかに進行し、結晶粒径の不均一性が緩和される。

(もっと読む)

表示装置

【課題】結晶性シリコン薄膜トランジスタのオフ電流を低減させ、表示コントラストを向上させることが可能な表示装置を提供する。

【解決手段】基板SUB1上に形成されるゲート絶縁膜GIを介してゲート電極GTの上層に形成される第1の半導体層MSFと、第1の半導体層MSFの上面に形成され、凹部が形成される第2の半導体層ASFとからなる活性層と、凹部を挟んで対向配置される一対のコンタクト層CNLと、コンタクト層CNLの一方の上層に形成されるドレイン電極DTと、他方の上層に形成されるソース電極STと、活性層の上面及び前記ドレイン電極DTと前記ソース電極STの上面に連続して形成される保護膜PASiとを有する薄膜トランジスタを備え、凹部が形成されている領域の膜厚は160nm以上である装置。

(もっと読む)

酸化物半導体を用いた薄膜トランジスタおよびその製造方法

【課題】オフ特性およびキャリア移動度に優れた、高品質の、酸化物半導体を用いた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、ゲート絶縁膜と、酸化物半導体からなる活性層とを備えてなる。そして、活性層とソース電極の間および活性層とドレイン電極の間には、炭素製のバッファ層が設けられてなる。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好で信頼性の高いトランジスタをスイッチング素子として用い、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】加熱処理により脱水化または脱水素化され、表面にナノ結晶からなる微結晶群が形成された酸化物半導体層を形成し、酸化物半導体層上に非晶質で透光性のある酸化物導電層を用いてソース電極層及びドレイン電極層を形成し、酸化物半導体層上の酸化物導電層を選択的にエッチングすることで透光性のあるボトムゲート型のトランジスタを形成し、同一基板上に駆動回路部と画素部を設けた信頼性及び表示品質の高い半導体装置を作製する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性が良好な薄膜トランジスタ及び当該薄膜トランジスタをスイッチング素子として用いた半導体装置を提供することを目的の一とする。

【解決手段】薄膜トランジスタが、絶縁表面上に形成されたゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と重なっており、なおかつ、酸化物半導体が有する一または複数の金属の濃度が、他の領域よりも高い層を含む酸化物半導体膜と、層に接するように酸化物半導体膜上に形成された一対の金属酸化膜と、該金属酸化膜に接するソース電極またはドレイン電極とを有する。そして、金属酸化膜は、ソース電極またはドレイン電極に含まれる金属が酸化することで形成されている。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、エッチングレジストを形成するためのフォトリソグラフィの工程を減らすことを目的とする。

【解決手段】ゲート電極30、ドレイン電極52及びソース電極54を含む薄膜トランジスタを形成する。薄膜トランジスタを覆う第1絶縁膜44を形成する。第1絶縁膜44上に第2絶縁膜46を形成する。第2絶縁膜46上に透明導電膜170を形成する。透明導電膜170上にフォトリソグラフィによってパターニングされたエッチングレジスト50を形成する。エッチングレジスト50を介して、透明導電膜170を第1エッチングによってパターニングして第1透明電極70を形成する。エッチングレジスト50を介して、第2絶縁膜46の第1透明電極70から露出する表面に対して行う第2エッチングによって第2絶縁膜46にドレイン電極52及びソース電極54の一方の上方に位置する貫通穴40を形成する。

(もっと読む)

薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法

【課題】ソース−ドレイン間等の電圧−電流特性を改善することができる薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法を提供する。

【解決手段】薄膜トランジスタ100は、半導体膜119と、半導体膜119の上方に形成されたソース電極層140と、半導体膜119の上方に形成されたドレイン電極層142と、ソース電極層140とドレイン電極層142との間、かつ、半導体膜119の上方に形成されたチャネル保護膜113と、を備える薄膜トランジスタであって、ソース電極層140とドレイン電極層142の少なくとも何れか一方は、チャネル保護膜113と接し、その上面がチャネル保護膜113の上面を超えない接触領域を有して、チャネル保護膜113の上面と重なっていない。

(もっと読む)

薄膜形成装置、薄膜の製造方法及び電子素子の製造方法

【課題】比較的に大型の矩形基板に対して、構造が簡易で、かつ、均一性の良く膜質が良好な薄膜を形成できるスパッタリング装置、薄膜の製造方法及び電子素子の製造方法を提供すること。

【解決手段】排気可能な真空容器内に、ターゲット1a裏面側に平面矩形状のマグネットユニット3を備え、ターゲット1aの表面でスパッタされたスパッタ粒子により基板保持台5に載置する基板2上に薄膜を形成するスパッタリング装置であって、スパッタ粒子が放出される側のターゲット1aと基板2間に、基板保持台5の面内方向に対して垂直な遮蔽板4を具備した構造を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】酸化物半導体をチャネル形成領域に用いたトランジスタを有する半導体装置の作製において、酸化物半導体膜を形成した後、水分、ヒドロキシ基、または水素などを吸蔵或いは吸着することができる金属、金属化合物または合金を用いた導電膜を、絶縁膜を間に挟んで酸化物半導体膜と重なるように形成する。そして、該導電膜が露出した状態で加熱処理を行うことで、導電膜の表面や内部に吸着されている水分、酸素、水素などを取り除く活性化処理を行う。

(もっと読む)

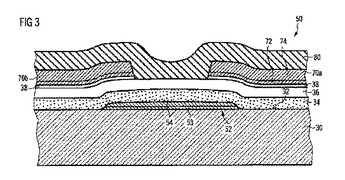

半導体デバイスを製造する方法および設備と半導体デバイス

半導体デバイスを生産する方法が提供され、この半導体デバイス(50)は、基板(30)と、半導体層(36、38)と、基板および半導体層から選択された少なくとも1つの要素に隣接する少なくとも1つのメタライゼーション層(52、70)とを含み、この方法は、基板および半導体層から選択された少なくとも1つの要素の近くに酸素を含む少なくとも1つのメタライゼーション層を形成するステップを含む。  (もっと読む)

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

液晶表示装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成することにより、開口率を上げる。

(もっと読む)

181 - 200 / 766

[ Back to top ]