Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

201 - 220 / 766

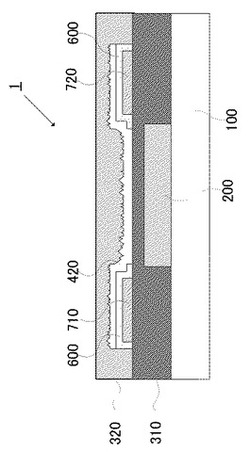

トランジスタ基板及びトランジスタ基板の製造方法

【課題】ソース領域及びドレイン領域と、チャネル層との間で、良好な電気的接合を確保でき、かつオン電流の低下を防ぐことのできるトランジスタ素子及びその製造方法を提供する。

【解決手段】トランジスタ基板1は、基板100上に配置されたゲート電極200と、前ゲート電極200上に配置されたゲート絶縁膜310と、ゲート絶縁膜310上の、互いにゲート電極200を挟んで対向する位置に形成されたソース電極710及びドレイン電極720と、ソース電極710上に形成されたソース領域と、ドレイン電極720上に形成されたドレイン領域と、ソース領域上、ドレイン領域上、及びソース領域と前記ドレイン領域との間のゲート絶縁膜310上に配置され結晶性シリコンを含む半導体膜420と、を備える。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを用いた表示装置及び薄膜トランジスタの製造方法

【課題】工程数の増大を引き起こさずに、遮光層で囲まれた薄膜トランジスタと同等以上の遮光能力を有する薄膜トランジスタおよびそれを用いた表示装置を提供する。

【解決手段】第1のゲート電極2と、第1のゲート電極2を覆う第1のゲート絶縁層3と、第1のゲート絶縁層3の上の半導体層6と、半導体層6の上の第2のゲート絶縁層7と、第2のゲート絶縁層7の上の第2のゲート電極8と、半導体層6に電気的に接続されたドレイン電極5及びソース電極4を有する薄膜トランジスタにおいて、半導体層6がZn、Ga、In、Snのうち少なくとも1種以上を含む非晶質酸化物半導体であり、第1のゲート電極2が下方から半導体層6への光の入射を遮り、第2のゲート電極8が上方から半導体層6への光の入射を遮り、第2のゲート電極8は第1のゲート絶縁層3及び第2のゲート絶縁層7を貫通して第1のゲート電極2と電気的に接続され、少なくとも一方の側方から半導体層6に入射する光を遮る。

(もっと読む)

結晶シリコン膜の形成方法、それを用いた薄膜トランジスタおよび表示装置

【課題】可視光領域の波長のレーザーを用いて、結晶性の安定した結晶シリコン膜を形成する結晶シリコン膜の形成方法を提供する。

【解決手段】金属膜を形成する第1工程と、前記金属膜上に絶縁膜を形成する第2工程と、前記絶縁膜に多結晶Siからなる結晶シリコン膜を形成する第3工程とを含み、前記第2工程において、前記絶縁膜を160nm〜190nmの膜厚範囲で形成し、前記第3工程は、前記絶縁膜にa−Siからなる非晶質シリコン膜を30nm〜45nmの膜厚範囲で形成する工程と、前記非晶質シリコン膜に可視光領域の波長のレーザーの光を照射することにより、前記結晶シリコン膜を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

金属ゲートトランジスタ、集積回路、システム、およびその製造方法

【課題】金属ゲートトランジスタ、集積回路、システム、およびその製造方法を提供する。

【解決手段】半導体デバイスであって、第1MOS構造は、基板上に配置された第1ゲート誘電体、前記第1ゲート誘電体上に配置された第1仕事関数金属層、および前記第1仕事関数金属層上に配置された第1ケイ化物を含み、且つ第2MOS構造は、前記基板上に配置された第2ゲート誘電体、前記第2ゲート誘電体上に配置された第2仕事関数金属層、および前記第2仕事関数金属層上に配置された第2ケイ化物を含む半導体デバイス。

(もっと読む)

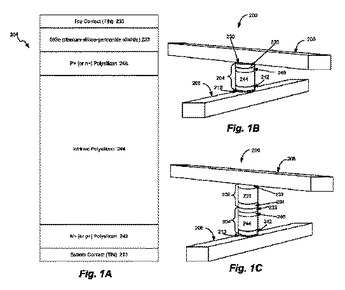

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に第1の薄膜トランジスタを有する駆動回路及び第2の薄膜トランジスタを有する画素を有し、前記第1の薄膜トランジスタは、第1のゲート電極層と、ゲート絶縁層と、第1の酸化物半導体層と、第1の酸化物導電層及び第2の酸化物導電層と、前記第1の酸化物半導体層の一部に接し、且つ前記第1の酸化物導電層及び前記第2の酸化物導電層の周縁及び側面に接する酸化物絶縁層と、第1のソース電極層と、第1のドレイン電極層と、を有し、前記第2の薄膜トランジスタは、第2のゲート電極層と、第2の酸化物半導体層と、透光性を有する材料により構成された第2のソース電極層及び第2のドレイン電極層と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン表面に厚さがサブナノから数ナノメートル(nm)レベルの極薄の絶縁膜を形成し、これを利用して、低電圧動作MOSデバイスを実現する。

【解決手段】ガラス基板上の多結晶シリコン(薄膜)に対して、その上に室温硝酸酸化法により1.8nmのSiO2膜1を形成し、さらに、その上にプラズマCVD法により40nmのSiO2膜2を堆積して積層にし、これをゲート絶縁膜10として、p−チャンネルMOSトランジスタ(TFT)を創製した。このTFTは、駆動電圧を3Vに低減しても十分に動作可能であり、消費電力を顕著に低減することできる。

(もっと読む)

発光装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えた発光装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネルストップ型を用い、画素用薄膜トランジスタと電気的に接続する発光素子と重なる位置にカラーフィルタ層を薄膜トランジスタと発光素子の間に設ける。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

薄膜トランジスタの製造方法及びそれを含む有機電界発光表示装置の製造方法

【課題】薄膜トランジスタ及びそれを含む有機電界発光表示装置の製造において、金属膜を半導体層に直接接触させて結晶化時にアーク発生を防止し、熱伝導を効率的に行い結晶化させるとともに、工程を単純化させて収率を高くする。

【解決手段】基板を提供する工程、上記基板上にバッファ層を形成する工程、上記バッファ層上に非晶質シリコン層のパターンを形成する工程、上記基板全面にソース/ドレイン電極用金属膜を形成する工程、上記ソース/ドレイン電極用金属膜に電界を印加する工程、上記非晶質シリコン層パターンを結晶化して半導体層を形成する工程、上記ソース/ドレイン電極用金属膜をパターニングし、上記半導体層と接続するソース/ドレイン電極を形成する工程、上記基板全面にゲート絶縁膜を形成する工程、上記ゲート絶縁膜上に位置し、上記半導体層に対応するゲート電極を形成する工程、および上記基板全面に保護膜を形成する工程を含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5×1010dyn/cm2 〜5×1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

太陽電池基板及び太陽電池基板の製造方法

【課題】太陽電池に使用可能な優れた電気的、光学的特性を有し、且つ耐湿性に優れた太陽電池基板用透明導電膜を有する太陽電池基板及び太陽電池基板の製造方法を提供する。

【解決手段】本発明による太陽電池基板は、透明基板と、透明基板に形成されるドーパントがドープされた酸化亜鉛(ZnO)薄膜と酸化亜鉛(ZnO)薄膜に熱処理によって形成される表面電荷活性化層と、を備えた透明導電膜を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を作製し、提供することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体膜とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層に接して保護膜となる酸化物絶縁膜を形成した後に、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行って、ソース電極層、ドレイン電極層、ゲート絶縁層中、及び酸化物半導体膜中に加え、上下に接して設けられる膜と酸化物半導体膜の界面に存在する水分などの不純物を低減する。

(もっと読む)

半導体装置の製造装置および配線パターンの形成方法

【課題】大量生産上、大型の基板に適している液滴吐出法を用いたパターン形成装置を

備えた半導体装置の製造装置を提供する。

【解決手段】本発明では、液滴吐出法を用いたパターン形成装置と、加熱処理室をそれぞ

れ複数設置し、それぞれを一つの搬送室と連結させたマルチチャンバー方式とし、吐出と

焼成とを効率よく行って生産性を向上させる。パターン形成装置にブロー手段を設け、着

弾直後にガスの吹きつけを基板の走査方向(或いは吐出ヘッドの走査方向)と同じ方向に

行い、ガス流路中に加熱ヒータを設けて局所的に焼成を行う。

(もっと読む)

201 - 220 / 766

[ Back to top ]