Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

141 - 160 / 766

液晶表示装置および液晶表示装置の製造方法

【課題】液晶表示装置の製造コストの低減を図る。

【解決手段】電界効果型の薄膜トランジスタを備える液晶表示装置であって、薄膜トランジスタの半導体層に、インジウムを材料に含む透明アモルファス酸化物半導体が用いられ、半導体層は、ソース電極およびドレイン電極並びにそれらの電極線として必要な領域を含む形状に形成され、半導体層に積層されるソース・ドレイン層に、インジウムを含む金属薄膜が用いられ、ソース・ドレイン層に積層される絶縁層に、窒化珪素による絶縁膜が用いられ、薄膜トランジスタのチャネル部が、絶縁層とソース・ドレイン層とに設けられた開口部によって形成されていることを特徴とする。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

有機FET

【課題】有機FETにおいて、電極から活性層へのキャリア注入効率を向上させること。

【解決手段】有機半導体層3とソース電極5および有機半導体層3とドレイン電極6との間に、電極表面との密着性が良好な界面層4を挿入することで、キャリア注入効率が向上する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

成膜方法及び半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供することを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でスパッタリングを行う。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて製造することが可能な電界効果トランジスタを提供する。

【解決手段】ソース領域144及びドレイン領域146並びにチャネル領域142を含む酸化物導電体層140と、チャネル領域142の導通状態を制御するゲート電極120と、ゲート電極120とチャネル領域142との間に形成され強誘電体材料からなるゲート絶縁層130とを備え、チャネル領域142の層厚は、ソース領域144の層厚及びドレイン領域146の層厚よりも薄い電界効果トランジスタ。酸化物導電体層140は、型押し成形技術を用いて形成されている。

(もっと読む)

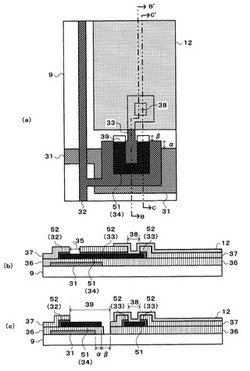

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

SiC半導体素子の製造方法

【課題】薄板化に伴うSiC基板の反りを修正するSiC半導体素子の製造方法の提供を目的とする。

【解決手段】本発明の半導体素子の製造方法は、(a)表面側に素子活性領域が形成されたSiC基板1を準備する工程と、(b)SiC基板1の表面を平坦面に固定し、裏面を研削する工程と、(c)SiC基板1の表面を平坦面に固定したまま、研削によるSiC基板の反りを相殺する応力を付与する内部応力層を、SiC基板内部に形成する工程とを備える。

(もっと読む)

薄膜トランジスタ、その製造方法、及びこれを含む表示装置

【課題】不完全結晶成長領域を含まない多結晶シリコンでゲート電極または遮光部材のような金属パターン上に位置する半導体層を形成することにより、駆動特性及び信頼性を向上させる薄膜トランジスタ、その製造方法、及びこれを含む表示装置を提供する。

【解決手段】多結晶シリコンで形成された半導体層142を含む薄膜トランジスタにおいて、前記半導体層と基板110との間に前記半導体層と絶縁するように位置する金属パターンをさらに含み、前記半導体層の多結晶シリコンは、結晶成長方向と平行な結晶粒界を含み、表面における波状線の最大ピークと最小ピークとの間の距離として定義される表面粗度が15nm以下である。

(もっと読む)

薄膜電界効果型トランジスタの製造方法

【課題】TFT特性が良好であり、しかも面内均一性等も良好な薄膜電界効果型トランジスタを低コストで提供すること。

【解決手段】基板上に、少なくともゲート電極、絶縁膜、活性層、ソース電極およびドレイン電極が形成され、活性層上にソース電極およびドレイン電極が設けられた薄膜電界効果型トランジスタの製造方法である。本発明の製造方法は、エッチング液として、りん酸、酢酸および硝酸を含む混酸水溶液を用いて、ソース電極およびドレイン電極を形成する工程を有する。この活性層は、In、GaおよびZnを含むアモルファス酸化物半導体で構成されるものであり、かつZn濃度が20%未満であり、In濃度が40%以上であり、Ga濃度が37%以上である。

(もっと読む)

アルミニウム電極配線用のガラス組成物と導電性ペースト、そのアルミニウム電極配線を具備する電子部品、及び、この電子部品の製造方法

【課題】鉛を含まず、アルミニウム(Al)の仕事関数より電極配線としての見かけの仕事関数が小さくなるアルミニウム電極配線用のガラス組成物を提供する。

【解決手段】アルミニウムより仕事関数が小さい元素の酸化物から構成される。この酸化物は、バナジウム(V)の酸化物と、アルカリ土類金属の酸化物と、アルカリ金属の酸化物とから構成され、アルカリ土類金属の元素としてはカルシウム(Ca)、ストロンチウム(Sr)及びバリウム(Ba)の元素の内少なくともバリウムを含む1種以上の元素がなり、アルカリ金属の元素としてはナトリウム(Na)、カリウム(K)、ルビジウム(Rb)及びセシウム(Cs)の元素の内少なくとも1種以上の元素がなる。バナジウムの元素が五酸化バナジウム(V2O5)として含まれているとした場合に、五酸化バナジウムを40〜70重量%含む。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極とチャネル領域を挟んで対向する第2のゲート電極とを有するデュアルゲート型の薄膜トランジスタのチャネル領域の形成方法において、結晶粒の間に非晶質半導体が充填される微結晶半導体膜を形成する第1の条件で第1の微結晶半導体膜を形成した後、結晶成長を促進させる第2の条件で、第1の微結晶半導体膜上に第2の微結晶半導体膜を形成する。

(もっと読む)

141 - 160 / 766

[ Back to top ]