Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

261 - 280 / 766

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

Al−Ni系合金配線材料及びそれを用いた素子構造

【課題】ITOなどの透明電極層と直接接合が可能なAl系合金配線材料であって、現像液への耐食性に優れ、コンタクトホール形成時における耐食性にも優れ、大面積のガラス基板において素子を形成した場合においても、そのガラス基板面内に形成された素子の接合抵抗値をより均一にすることができるAl−Ni系合金配線材料を提供する。

【解決手段】アルミニウムにニッケルを含有したAl−Ni系合金配線材料において、セリウムとボロンとを含有し、各濃度は、ニッケル含有量をニッケルの原子百分率Xat%とし、セリウム含有量をセリウムの原子百分率Yat%とし、ボロン含有量をボロンの原子百分率Zat%とした場合、式0.5≦X≦5.0、0.01≦Y≦1.0、0.01≦Z≦1.0の各式を満足する領域の範囲内にある。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

メッシュ構造を有する電極を具備した太陽電池及びその製造方法

【課題】低抵抗と高透過性を併せ持ち、さらに太陽光を効率よくキャリアの励起に利用できる、安価な材料を用いた光入射面側電極を備えた太陽電池、及びその製造方法を提供する。

【解決手段】本発明の太陽電池は、光電変換層と、光入射面側電極層と、対向電極層とを具備し、前記光入射面側電極層が前記層を貫通する複数の開口部を有し、かつその膜厚が10nm以上200nm以下の範囲にあり、前記開口部の1つあたりの面積が80nm2以上0.8μm2以下の範囲にあり、開口部の開口率が10%以上66%以下の範囲にあり、光吸収層の少なくとも一部が、前記光入射面側電極層と前記光電変換層の接触面から1μm以内の距離に配置されていることを特徴とする。この電池の光入射面側電極層は、微粒子の単粒子層や、ブロックコポリマーの自己組織化によるドットパターンをマスクにエッチングしたり、スタンパーを利用して形成させることができる。

(もっと読む)

半導体装置、半導体装置製造方法、TFT基板、および表示装置

【課題】オン電流を増加させて駆動能力を大きくした半導体装置(ダブルゲート型薄膜トランジスタ)、この半導体装置を製造する半導体装置製造方法、この半導体装置を搭載したTFT基板、およびこのTFT基板を適用した表示装置を提供する。

【解決手段】半導体装置1は、絶縁性基板10(絶縁性基板110)の上に形成された第1ゲート電極11と、第1ゲート電極11の上に形成された第1絶縁層12と、第1絶縁層12の上に形成された半導体層13と、半導体層13の一端に接続されたソース電極15と、ソース電極15に対向して半導体層13の他端に接続されたドレイン電極16と、半導体層13の上に形成された第2絶縁層17と、第2絶縁層17の上に形成された第2ゲート電極19とを備え、第1ゲート電極11および第2ゲート電極19の少なくとも一方は、透明導電性材料で形成され、透明電極を構成している。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】キャパシタの表面積を増大させて容量が増加した有機電界発光表示装置及びその製造方法。

【解決手段】薄膜トランジスタ及びキャパシタ領域を含む基板と;バッファー層と;トランジスタ領域に位置する金属触媒を利用して結晶化した半導体層パターンと;ゲート絶縁膜と;前記パターンの一定領域に対応されるゲート電極及びキャパシタ領域のキャパシタ下部電極と;層間絶縁膜と;前記パターンと一部が連結されるソース/ドレイン電極及びキャパシタ下部電極に対応される上部電極と;同じく層間絶縁膜上のソース/ドレイン電極と電気的に連結される第1電極と;発光層を含む有機膜層;及び第2電極をこの順で含み、キャパシタ領域に対応されるバッファー層、ゲート絶縁膜、及び層間絶縁膜の一定領域、キャパシタ下部電極、及びキャパシタ上部電極の表面には半導体層パターンを形成する結晶粒の結晶粒界及びシードの形状と一致する形状の突出部を形成する。

(もっと読む)

表示装置

【課題】オフ電流の低減とともにオフリーク電流の低減が図れ、製造工数の増大をもたらすことなく回路の集積化が図れる薄膜トランジスタを備えた表示装置の提供。

【解決手段】表示部が形成された基板上に複数の薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を跨って形成されたゲート絶縁膜と、

このゲート絶縁膜の上面に形成され、平面的に観て前記ゲート電極の形成領域内に開口が形成された層間絶縁膜と、

前記層間絶縁膜の表面に前記開口を間にして配置された一対の高濃度半導体膜と、

前記層間絶縁膜の前記開口を跨いで形成され、平面的に観て、前記ゲート電極の形成領域内に形成されるとともに前記一対の高濃度半導体膜に電気的に接続された多結晶半導体層と、

前記一対の高濃度半導体膜のそれぞれに重ねられ前記多結晶半導体膜に重ねられることなく形成された一対の電極と、

を備えたものを含む。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】酸化物半導体の活性層を、Ga等を主成分とする酸化物を含む層によって確実に保護して電界効果型トランジスタを製造する方法を提供する。

【解決手段】絶縁基板10又は絶縁層14上に、酸化物半導体層16と、該酸化物半導体層上にGaを主成分とする酸化物を含む第1の保護層18及びInを主成分とする非晶質酸化物を含む第2の保護層20をこの順に交互に少なくとも1層ずつ積層した複合保護層21とを有する積層体30をパターン形成する。次いで、積層体上に、対向配置されたソース電極40A及びドレイン電極40Bをパターン形成する。積層体のソース電極及びドレイン電極が形成されている領域以外において、複合保護層の最上部に位置する第2の保護層から、層ごとに順次エッチングして除去することにより、複合保護層の最下部に位置する第1の保護層を露出させる。

(もっと読む)

半導体装置

【課題】還流ダイオードの逆回復動作時に生じる振動現象の収束時間を低減することが可能な半導体装置を提供する。

【解決手段】 ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、半導体基板領域を含む半導体スナバ200とを備える。半導体スナバ200は、還流ダイオード100の逆バイアス時に少なくとも前記基板領域の一端側に形成されるキャパシタ210と、基板領域の一部を含む抵抗220と、還流ダイオード100の順バイアスに対して逆阻止状態となるように、基板領域の少なくとも一部に形成された逆阻止型ダイオード222とを含む。

(もっと読む)

トランジスタ及び当該トランジスタの作製方法

【課題】酸化物半導体層をチャネル層として適用するトランジスタにおいて、特性のばらつきを低減すると共に、酸化物半導体層とソース電極層及びドレイン電極層とのコンタクト抵抗を低減することを課題とする。

【解決手段】チャネル層を酸化物半導体で設けるトランジスタにおいて、酸化物半導体層の領域のうち、ソース電極層とドレイン電極層の間に位置しチャネルが形成される領域を少なくとも非晶質構造で設け、ソース電極層及びドレイン電極層等の外部と電気的に接続する領域を結晶構造で設ける。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

電界効果型トランジスタ

【課題】酸化物半導体の活性層が保護されるとともにソース電極及びドレイン電極とのオーミックコンタクトが確保され、閾値変動が抑制される電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタ100は、ゲート電極12と、ゲート電極上に形成されている絶縁層14と、絶縁層を隔てて前記ゲート電極に対向する位置に形成されている酸化物半導体層16と、Gaを主成分とする酸化物を含み、酸化物半導体層上に形成されている保護層18と、Inを主成分とする非晶質酸化物を含み、保護層上に形成されている接触層20A,20Bと、接触層上で、該接触層に接触しているとともに対向配置されているソース電極22A及びドレイン電極22Bと、を有する。接触層は、保護層とソース電極及びドレイン電極とが厚さ方向で重なる領域に形成されており、ソース電極とドレイン電極との間では分離している。

(もっと読む)

半導体装置

【課題】並列接続された還流ダイオードと半導体スナバ回路が隣接して配置されるので、小型化され且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置を提供する。

【解決手段】ユニポーラ動作する還流ダイオード100と、少なくともキャパシタ210及び抵抗220を有し、還流ダイオード100と並列接続されて還流ダイオード100に隣接して配置された半導体スナバ回路200とを備える。

(もっと読む)

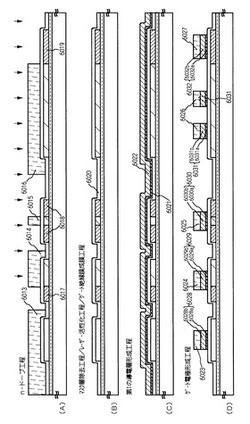

薄膜トランジスタの作製方法及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜と、絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上にレジストマスクを形成し、第1のエッチングを行って薄膜積層体を形成し、該第1の導電膜に対してサイドエッチングを伴う第2のエッチングをドライエッチングにより行ってゲート電極層を形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。ドライエッチングを行う前に、少なくともエッチングされた半導体膜の側壁を酸化処理することが好ましい。

(もっと読む)

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オン電流を低下させることなくオフ電流を低減し、画素回路やゲート駆動回路の制御に適用可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ100は、中央部がチャネルとなる微結晶シリコン層4と、この微結晶シリコン層4上に設けられた非晶質シリコン層5とを備え、ソース電極7およびドレイン電極8を、コンタクト層6a、6bにそれぞれ接続された下部ソース電極7aおよび下部ドレイン電極8aと、この下部ソース電極7aおよび下部ドレイン電極7bの上面に形成された上部ソース電極7bおよび上部ドレイン電極8bとの2層で構成するとともに、上部ソース電極7bおよび上部ドレイン電極8bのチャネル側端部をそれぞれ下部ソース電極7aおよび下部ドレイン電極8aのチャネル側端部に対して庇状に突出するように構成した。

(もっと読む)

電界効果型トランジスタ及び電界効果型トランジスタの製造方法

【課題】非晶質酸化物を含む活性層を有する電界効果型トランジスタ及び電界効果型トランジスタの製造方法において、活性層への水分や酸素の影響が抑制されると共に閾値シフトの改善された電界効果型トランジスタ及び電界効果型トランジスタの製造方法を提供する。

【解決手段】電界効果型トランジスタ10において、非晶質無機材料からなる保護層24を、活性層18の少なくともソース電極20Aとドレイン電極20Bとの電極間に対応する領域を覆うように配置し、且つ該保護層24のバンドギャップが活性層18のバンドギャップより大きい保護層24とする。

(もっと読む)

261 - 280 / 766

[ Back to top ]