Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

1,421 - 1,440 / 1,522

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 SiC基板に対して電極を形成するときに、従来よりも低温の焼鈍により、良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】 n型SiC基板1の電極形成領域上に、合金層2を形成し、少なくとも該合金層2に対して焼鈍を施すことにより、該電極形成領域上に電極を形成するSiC半導体装置10の製造方法であって、合金層2は、Niを該合金層2の代わりとして前記焼鈍したときにシリサイドが形成される該焼鈍の温度よりも低温で、前記焼鈍してもシリサイドを形成するものからなることを特徴とする。

(もっと読む)

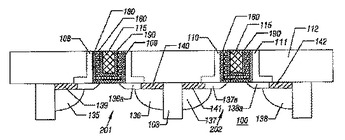

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

金属アミジナートを用いる原子層の析出

銅(I)N,N’−ジイソプロピルアセトアミジネートの蒸気と水素ガスとを交互に投与する複数回分の投与量を順次反応させて、加熱基板上に銅の金属薄膜を析出させる。コバルト(II)ビス(N,N’−ジイソプロピルアセトアミジネート)の蒸気と水素ガスとを交互に投与する複数回分の投与量を順次反応させて、加熱基板上にコバルトの金属薄膜を析出させる。これら金属の窒化物及び酸化物の薄膜は、前記水素をそれぞれアンモニア又は水蒸気に代えることによって形成することができる。これらの薄膜は、均一な厚さを有しかつ細孔での優れたステップカバレッジを有する。好適な応用には、マイクロエレクトロニクスにおける電子的連結及び磁気情報記録装置における磁気抵抗が含まれる。  (もっと読む)

(もっと読む)

バナジウム含有膜の形成方法

【課題】CVD法により良好な特性を有する下地層としてのバナジウム含有膜の形成方法の提供。

【解決手段】TDEAVまたはTDMAVなどの金属原料ガスと還元性ガスとを用いて、CVD法によりバナジウム含有膜を形成する。還元性ガスは、乖離してH*ラジカルや、H+イオンを放出することができるガスであり、例えばターシャリーブチルヒドラジン、NH3、H2などから選ばれたガスである。金属原料ガスと還元性ガスとの反応は、成膜速度が基板温度に依存する温度領域で行われる。

(もっと読む)

液晶表示装置の製造方法およびTFT基板

【課題】液晶表示装置製造の費用減少、生産性向上。

【解決手段】TFT部及びゲート−パッド連結部に第1及び第2金属膜を蒸着しそれら金属膜をパターニングしゲート電極及びゲートパッドを形成する段階、全面に絶縁膜を形成する段階、第1及び第2非晶質シリコン膜パターンをTFT部の絶縁膜上に形成する段階であって第2非晶質シリコン膜全体の下部表面が第1非晶質シリコン膜表面と当接するようそれらのパターンを形成する段階、ソース及びドレイン電極をTFT部上に形成しソース及びドレイン電極間の第2非晶質シリコン膜を除去する段階、ドレイン電極及びゲートパッドの一部が露出されるよう保護膜を形成しゲートパッドの一部上の絶縁膜を除去する段階、第1及び第2画素電極パターンを形成する段階を含み、第1金属膜はCr、Mo、Ta及びTiのうち1つの金属膜であり、第2金属膜はAl又はAl合金である。

(もっと読む)

半導体装置

【課題】 高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えることができるようにし、ゲートリーク電流の増大を抑えて、信頼性の低下を招かないようにする。

【解決手段】 半導体装置を、ゲート電極1がメタルゲート電極であるか、又は、ゲート絶縁膜4が高誘電率ゲート絶縁膜である場合に、ゲート電極1とゲート絶縁膜4との間に、ゲート電極1側から順に、シリコン酸化膜2、シリコン窒化膜3を備えるものとする。

(もっと読む)

蒸着源と蒸着装置

【課題】膜質の良い薄膜を成膜可能な蒸着装置を提供する。

【解決手段】

筒状のアノード電極21の上端部分を除去し、切り欠き部分22を設け、基板13から見える部分にアノード電極21の内壁面が存在しないようにした。従って、基板13から見える部分で小滴が発生せず、基板表面に小滴が到達することが無くなる。微小荷電粒子は磁力線17に巻き付きながら移動するため、基板13表面に到達し、薄膜が成長する。

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 黒鉛の発生を充分に回避しながら、n型SiC基板に対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】 n型SiC基板1の電極形成領域上に、第1層2a1を形成し、第1層2a1上に第2層2b1を形成し、第1層2a1及び第2層2b1に対してアニールを施すことにより、前記電極形成領域上に電極を形成するSiC半導体装置10Aの製造方法であって、前記第1層2a1は、Ni、Cu、W、Co、Mo、Ta、Pd、Tiのいずれかと、Ni、Cu、W、Co、Mo、Ta、Pd、Tiのうちの2つ以上からなる合金と、のうちの一つで形成し、前記第2層2b1は、Siで形成することを特徴とする。

(もっと読む)

ダブルバリアトンネル接合共鳴トンネリング効果に基づくトランジスタ

本発明は、ダブルバリアトンネル接合共鳴トンネリング効果に基づくトランジスタに関し、基板、エミッタ、ベース、コレクタ、第1トンネルバリア層および第2トンネルバリア層とを備え、第1トンネルバリア層が、エミッタとベースの間に設けられ、第2トンネルバリア層が、ベースとコレクターの間に設けられ、かつエミッタとベース間及びベースとコレクタ間に形成されたトンネル接合の接合面積が1〜10000μm2であり、前記ベースの厚さが当該層材料の電子平均自由行程に匹敵し、前記エミッタ、ベースおよびコレクタの中でただ1つの極(pole)の磁化方向が自由である。ダブルバリア構造を採用するため、ベースとコレクタの間に発生したショットキーバリアを克服している。ベース電流は変調信号であり、ベース又はコレクタの磁化方向を変えることによって、共鳴トンネリング効果を発生し、適当な条件において増幅信号が得られる。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法、並びにテレビジョン

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型のTFTを有する半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜を成膜し、該非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜上にドナー型元素又は希ガス元素を有する層を形成し加熱して触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型のTFTを形成して半導体装置を作製する。

(もっと読む)

トランジスタ及びこれを有する表示装置

【課題】寄生容量を最小化する。

【解決手段】ゲート電極配線210はボディ部212、互いに平行する2つのハンド部214、216を含む。ドレイン電極配線230は、ゲート電極配線と絶縁されていて、2つのハンド部234、236との間でゲート電極配線の一部と重なって延びている。ソース電極配線240は、ゲート電極配線と絶縁されていて、ボディ部241、2つのハンド部242、244の外側領域で重なりながらドレイン電極と離隔される。これによって、ゲート−ドレインの間の寄生容量を最小化し、ゲート電極領域がカバーする領域内にドレイン及びソース電極を配置することで、ドレイン−ゲートの間のカップリング容量を最小化させかつトランジスタの配置空間を減らすことができる。

(もっと読む)

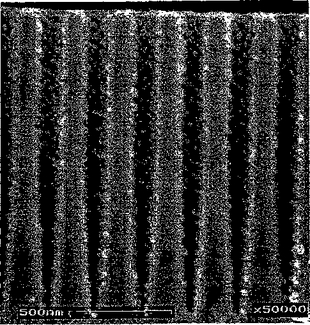

CNT入り配線材の製造方法およびスパッタリング用ターゲット材

【課題】配線パターンとなる金属材料中にCNTを均一に分散させると共に、配線パターンの電気導電率を向上させる。また、スパッタリングによって金属薄膜中にCNTを均一に分散混入するためのターゲット材を提供する。

【解決手段】絶縁性材料からなる基材8の表面にCNT入り金属層13を形成し、金属層13をパターンエッチングして配線パターンを形成する配線材の製造方法において、CNT入り金属層13をスパッタリング法により形成する。CNTとCuを同時にスパッタリングしてCNT入り金属層13を形成しているため、CNTをCu中に均一に混入できると共に、CNTとCu間の界面抵抗を低減でき配線の電気導電率が向上する。スパッタリング用ターゲット材10としては、CuにCNTが含まれたターゲット材を用いる。

(もっと読む)

薄膜トランジスタアレイ基板及びその製造方法

【課題】本発明の目的は、工程を単純化すると共に、コストを低減できる薄膜トランジスタアレイ基板及びその製造方法を提供するところにある。

【解決手段】薄膜トランジスタアレイ基板は、基板上に形成されたゲートラインと、前記ゲートライン上に形成されたゲート絶縁膜と、前記ゲート絶縁膜を挟んで前記ゲートラインと交差されるように形成され、WSix、CoSix、NiSixのうち少なくともいずれか一つを含むデータラインと、前記ゲートライン及びデータラインの交差部に位置する薄膜トランジスタと、前記ゲートライン及びデータラインの交差で設けられた画素領域に形成され、前記薄膜トランジスタと接続される画素電極と、を備えることを特徴とする。

(もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

液晶表示素子及びその製造方法

【課題】薄膜トランジスタの製造に使用されるマスクの数を減少させた液晶表示素子及びその製造方法を提供する。

【解決手段】第1基板及び第2基板を提供する段階と、第1基板上にソース領域、ドレイン領域、チャネル領域及びストレージ領域を含むアクティブ層を形成する段階と、第1絶縁膜を形成する段階と、ゲート電極、ゲートライン、画素電極及びストレージラインを形成する段階と、第2絶縁膜を形成する段階と、第1絶縁膜と第2絶縁膜を介してソース領域とドレイン領域の一部をそれぞれ露出させる第1、第2コンタクトホールを形成する段階と、第2絶縁膜を介して画素電極を露出させる画素ホールを形成する段階と、第1コンタクトホールを介してソース領域と電気的に接続されるソース電極、及び前記第2コンタクトホールを介してドレイン領域と電気的に接続されるドレイン電極を形成する段階と、第1基板と第2基板の間に液晶層を形成する段階とを含む。

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 n型SiC基板に対して、低抵抗で良好なオーミック電極を容易に形成できるSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】 n型SiC基板1の電極形成領域上に、メッキ法によって、n型の不純物を含む金属層2を形成し、金属層2に対して、焼鈍処理を施すことを特徴とする。

(もっと読む)

スイッチング装置

比較的低いインピーダンス及び比較的低い光学的スイッチングフラックスで、オン状態で大きな電流を維持することができる高電圧ダイヤモンド系スイッチング装置。この装置は、スイッチされる高電圧の存在下でスイッチをオフにすることもできる。この装置は、本質的に固有のダイヤモンド層又はダイヤモンド体中の一部分への、スイッチされる印加電圧により逆バイアスに保持されるショットキー障壁接点及び第二金属接点を有するダイヤモンド体からなる。それは、光源又は他の照明又は照射手段も含み、固有ダイヤモンド層へのショットキー接点により形成された空乏領域がその放射線に露出された時、帯電キャリヤーが発生するようになっている。その時、帯電キャリヤーの全数の利得は、それらの帯電キャリヤーが固有ダイヤモンド層内の電界で加速されること及び補助電子なだれ降伏の仕方で更にキャリヤーを発生する結果として起きる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 はんだ接続用パッドを有する半導体装置において、製造工程中の熱負荷などによって発生する恐れのある、パッド部の膜剥がれを防止する。

【解決手段】 シリコン、シリコン酸化膜上に形成されるTi膜またはTi化合物膜と、はんだが接続されるNi膜(またはCu膜)との間に、両者との密着性が良好なCr膜を挿入したパッド構造とする。さらに、Ti膜またはTi化合物膜とシリコン酸化膜との界面に生じる剥離を防止するため、Cr膜がTi膜またはTi化合物膜よりも大きな面積で形成された構造とする。

(もっと読む)

薄膜型電界効果トランジスタ、薄膜型電界効果トランジスタの製造方法、アクティブマトリクス回路および液晶表示装置

【課題】側壁保護膜を利用したリフトオフ法を利用してソース・ドレイン電極およびそれを分離するチャネル開口部を形成することで、狭いゲート長を形成することを可能とする。

【解決手段】基板11上に形成されたゲート電極12と、ゲート電極12を被覆するように基板11上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成されたもので、線状のチャネル開口部27により分割されたソース・ドレイン電極14、15と、チャネル開口部23を埋め込むようにソース・ドレイン電極14、15上に形成されたチャネル層17とを備えた薄膜型電界効果トランジスタ1である。

。

(もっと読む)

1,421 - 1,440 / 1,522

[ Back to top ]