Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

1,481 - 1,500 / 1,522

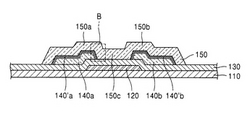

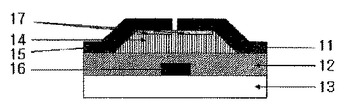

薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置

【課題】 ソース/ドレイン電極間の電気的疎通を円滑にすることが可能な,薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置を提供する。

【解決手段】 本発明に係る薄膜トランジスタは,基板110と,基板110上に形成されたゲート電極120と,ゲート電極120上に形成されるゲート絶縁層130と,ゲート電極120と絶縁されるようにゲート絶縁層130上に形成されるソース/ドレイン電極140a,140bと,ソース/ドレイン電極140a,140bと接するとともに,ゲート電極120と絶縁される有機半導体層150と,を含み,ソース/ドレイン電極140a,140bの少なくとも有機半導体層150と接する部分には酸化部140´a,140´bが設けられ,酸化部140´a,140´bを構成する物質は,有機半導体層150のHOMOエネルギー準位より大きい仕事関数を有する物質を含む。

(もっと読む)

半導体装置の作製方法

【課題】 より高精細なパターンの形成が可能な、液滴吐出法を用いた半導体装置の作製方法の提供を課題とする。

【解決手段】 パターンが形成されたモールドを絶縁膜に押し付けた状態で絶縁膜の硬化を行なった後、モールドを取り外すことで、絶縁膜に凹部を形成し、導電材料を有する液滴を吐出することにより、凹部に導電膜を形成し、導電膜を覆うようにゲート絶縁膜を形成し、ゲート絶縁膜上に島状の半導体膜を形成することを特徴とする半導体装置の作製方法。

(もっと読む)

メッキ法による金属パターン形成方法

【課題】 金属集積回路構造を好適に電気鋳造する方法を提供する。

【解決手段】 本発明による方法は、中間絶縁体を貫通するビアまたはラインといった開口部(108)を形成して基板(102)の表面(104)を露出し、中間絶縁体(106)と基板の表面との上にあるベース層(110)を形成し、ベース層の上にあるストライク層(112)を形成し、ストライク層の上にある最上層を形成し、選択的にエッチングすることにより基板の表面の上にある最上層を除去してストライク層(112)の表面を露出し、ストライク層の表面の上にある金属構造(114)を電気鋳造する。電気鋳造された金属構造(114)は、電気メッキまたは無電解堆積プロセスを用いて堆積される。典型的には、この金属はCu、Au、Ir、Ru、Rh、Pd、Os、PtまたはAgである。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

自己走査型発光素子アレイチップおよびその製造方法

【課題】基板の表面側にアノード電極またはカソード電極を設けた発光素子サイリスタが複数配列された自己走査型発光素子アレイチップであって、チップ面積が大きくならない構造を提供する。

【解決手段】p形GaAs基板10の上に、p形GaAs層12,n形GaAs層14,p形GaAs層16,n形GaAs層18が順次積層され、n形GaAs層18上にカソード電極22が、p形GaAs層16上にゲート電極23が形成されている。GaAs層12に溝50が設けられ、溝の側壁にアノード電極20が形成されている。

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

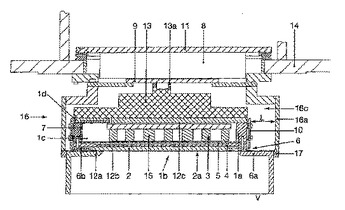

可動な平らなターゲットを用いて材料を飛散させるための装置及び方法

真空室内で材料を飛散させる装置であって、−平面内で可動な、平らでかつカソードとして接続可能な少なくとも1つのターゲットを有するターゲット装置を有し、

定置のターゲット環境と、ターゲット装置に対応配置された駆動装置と、ターゲット

に対応配置された少なくとも1つのアノードを有するアノード装置と、

ターゲットの飛散表面からの材料の遊離を助けるための磁場を発生させるための磁気

装置と

を備えている形式のものにおいて、少なくとも1つの非回転対称的な有利には方形のターゲットプレートとして構成されたターゲットが設けられ、該ターゲットがターゲット装置で−平面内で可動であることが提案されている。さらに本発明は材料を飛散させる方法にも関する。  (もっと読む)

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

複数のフィールドプレートを有するワイドバンドギャップトランジスタ

ソース電極およびドレイン電極が半導体層に接触した、基板上の複数の活性半導体層を備えるトランジスタ。ゲートが、ソース電極とドレイン電極との間に、複数の半導体層上に形成される。複数のフィールドプレートが、半導体層上に配置され、各フィールドプレートは、ゲートのエッジからドレイン電極に向かって延び、また各フィールドプレートは、前記半導体層から、また他のフィールドプレートから分離される。最上部のフィールドプレートは、ソース電極に電気的に接続され、他のフィールドプレートは、ゲートまたはソース電極に電気的に接続される。  (もっと読む)

(もっと読む)

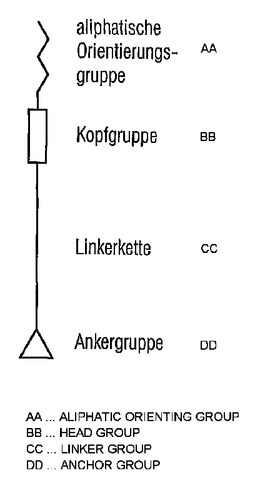

超薄膜誘電体、および、有機電界効果トランジスタでの超薄膜誘電体の使用

本発明は、基板、ソース電極、ドレイン電極、ゲート電極、および有機半導体材料を含む有機電界効果トランジスタに関するものである。このとき、誘電体層(ゲート誘電体)が、ゲート電極と半導体材料との間に配置されている。上記誘電体層は、アンカー基、リンカー基、頭部基、および脂肪族基を含んだ有機化合物の自己組織化単分子層からなる。アンカー基、リンカー基、頭部基、および脂肪族基は、この順にて互いに結合されている。  (もっと読む)

(もっと読む)

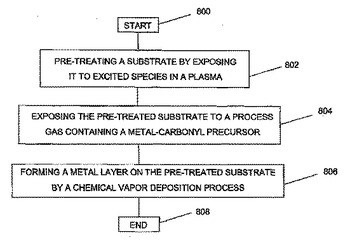

金属層を形成する方法および装置

形態が向上した金属層を基材の上に形成する方法および処理ツールが提供される。本方法は、プラズマの中で励起された化学種に基材を曝すことによって基材を前処理するステップと、金属カルボニル前駆物質を含有するプロセスガスに前処理された基材を曝すステップと、金属層を前処理された基材の上に化学蒸着法で形成するステップとを含む。金属カルボニル前駆物質は、W(CO)6、Ni(CO)4、Mo(CO)6、Co2(CO)8、Rh4(CO)12、Re2(CO)10、Cr(CO)6、またはRu3(CO)12、もしくはこれらの任意の組合せを含み、金属層は、W、Ni、Mo、Co、Rh、Re、Cr、またはRu、もしくはこれらの任意の組合せをそれぞれ含み得る。  (もっと読む)

(もっと読む)

基板処理方法

処理チャンバ内のセラミック基板ヒータ上の基板を処理する方法である。この方法は、処理チャンバ内のセラミック基板ヒータ上に保護コーティングを形成する段階、前記コーティングされたセラミック基板ヒータ上で基板を処理する段階、を含む。前記処理する段階は、前記セラミック基板ヒータ上で処理される基板を提供する段階と、前記基板を処理ガスで露光することによって前記基板上で処理を行う段階と、前記処理された基板を前記処理チャンバから取り外す段階と、を含む。  (もっと読む)

(もっと読む)

原子層堆積を実行するための方法およびシステム

【課題】 原子層堆積を実行するための方法およびシステムを提供することである。

【解決手段】 原子層堆積(ALD)を実行するためのプラズマ処理システムは、処理チャンバと、処理チャンバ内で提供される基板ホルダと、処理チャンバに第1のガスおよび第2のガスを供給するように構成されたガス注入システムとを具備する。システムは、処理チャンバに連続的に第1のガス流れを流し、第1の時間に処理チャンバに第2のガス流れをパルス化して流すガス注入システムを制御するコントローラを含む。コントローラは、第2の時間に基板ホルダにRF電力をパルス化する。

(もっと読む)

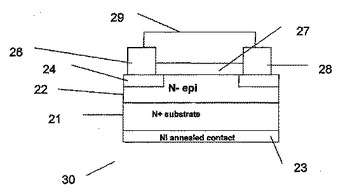

炭化ケイ素上に耐久性接触を有するデバイスおよびその製造方法

ショットキーバリア炭化ケイ素デバイスは、レニウムショットキー金属接触を有している。レニウム接触(27)は250Åよりも厚く、2000Åから4000Åまでの間であり得る。ターミネーション構造は、ショットキー接触の周囲の環状領域をイオンミリングすることによって与えられる。  (もっと読む)

(もっと読む)

低ジルコニウムのハロゲン化ハフニウム組成物

本発明は、約1000ppm未満のジルコニウム濃度を有するハロゲン化ハフニウム組成物、約1000ppm未満のジルコニウム濃度を有するハロゲン化ハフニウム組成物の製造方法、有機金属化合物前駆体、有機金属化合物前駆体の製造方法、及び有機金属化合物前駆体からの膜又は被膜の製造方法に関する。有機金属化合物は、膜蒸着のための化学蒸着又は原子層蒸着の前駆体として半導体用途に有用である。  (もっと読む)

(もっと読む)

窒化物半導体装置のオーム性電極構造

窒化物半導体を有する窒化物半導体装置のオーム性電極構造であって、窒化物半導体上に形成された第1の金属膜と、第1の金属膜上に形成された第2の金属膜とを有する。第1の金属膜は、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zrから成るグループの中から選ばれた少なくとも一つの材料で構成されている。第2の金属膜は、第1の金属膜102と異なる、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zr、Pt、Auから成るグループの中から選ばれた少なくとも一つの材料で構成されている。 (もっと読む)

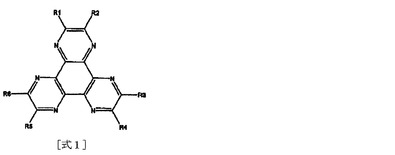

有機薄膜トランジスタ

本発明は、有機物層を有する有機トランジスタが提供される。本発明の前記有機物層は、下記式1で表される化合物のうち少なくともいずれか1種を含む。

(もっと読む)

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

本発明は、基板110、基板上に形成されているゲート電極124、基板及びゲート電極を覆っているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173及びドレイン電極175、ゲート絶縁膜、ソース電極、及びドレイン電極上に形成されている半導体層150、半導体層、ソース電極、ドレイン電極及びゲート絶縁膜を覆っている保護膜180を含み、ゲート絶縁膜及び保護膜はパリレンからなる薄膜トランジスタ表示板を提供する。  (もっと読む)

(もっと読む)

配線構造の形成方法及び半導体装置

下層配線(101)と不図示の上層配線とを接続するためのビア孔(102)を絶縁膜(103)にエッチングストッパー膜(104)及びハードマスク(105)を用いて形成した後、本発明の1ステップの低パワー・バイアス・スパッタ法によりビア孔(102)の内壁を覆うように絶縁膜(103)上にTaからなる下地膜(106)を形成する。ここで、ビア孔(102)の内壁面から絶縁膜(103)上にわたって薄く均一な膜厚の下地膜(106)が得られる。このように、比較的簡素な工程により、配線形成上の不都合を生ぜしめることなく、開口の内壁面、即ち側壁面から底面にかけて薄く均一に下地膜を成膜することを可能とし、信頼性の高い極微細な配線構造を実現する。

(もっと読む)

(もっと読む)

1,481 - 1,500 / 1,522

[ Back to top ]