Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

161 - 180 / 250

半導体素子の製造方法

【課題】理想的なトレンチコンタクト形成によってコンタクトの低抵抗化と製造の低コスト化を実現する半導体素子の製造方法を提供する。

【解決手段】半導体装置の製造方法においては、半導体基板上に中間絶縁膜20を形成する工程と;前記中間絶縁膜上に第1の層22を形成する工程と;前記中間絶縁膜及び第1の層にコンタクトホールを形成する工程と;前記第1の層をハードマスクとして用いて、前記半導体基板に前記コンタクトホールと連通するトレンチ40を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】好適な特性を有するゲート絶縁膜及びゲート電極からなるP型FET及びN型FETを備える半導体装置を提供する。

【解決手段】P型FET形成予定領域とN型FET形成予定領域とにわたって、基板上にゲート絶縁膜を形成し、ゲート絶縁膜上にP型FET用のゲート電極層を形成し、P型FET形成予定領域とN型FET形成予定領域とにおいて、P型FET用のゲート電極層を加工することにより、P型FET形成予定領域にP型FET用のゲート電極を形成すると共に、N型FET形成予定領域にダミーゲート電極を形成し、N型FET形成予定領域において、ゲート絶縁膜上からダミーゲート電極を除去することにより、溝を形成し、溝にゲート電極材料を埋め込むことにより、ゲート絶縁膜上にN型FET用のゲート電極を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】 薄膜トランジスタの駆動特性を向上させることができる薄膜トランジスタ基板及びこれの製造方法が開示される。

【解決手段】 薄膜トランジスタ基板は、絶縁基板、絶縁基板上に形成されてゲートライン及びゲートラインに接続されたゲート電極を含むゲート配線、ゲート配線を覆うゲート絶縁膜、ゲート電極と対応してゲート絶縁膜上に形成された活性層、活性層上に形成された酸化防止層、並びにゲート絶縁膜及び酸化防止層上に形成され、データライン、ソース電極、及びドレイン電極を含むデータ配線を含む。ゲート配線及びデータ配線は、インジウム酸化物、銀、及びインジウム酸化物が順次積層された3層膜構造を有する。したがって、配線抵抗を減少させると共に薄膜トランジスタの駆動特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜に高誘電率膜を使用し、ゲート電極に金属を含む導体膜を使用するpチャネル型MISFETにおいて、生産性向上を図ることができる技術を提供することにある。そして、金属を含む導体膜の仕事関数値が酸化シリコン膜に接するとした場合にシリコンの価電子帯近傍の値から離れたものであっても、pチャネル型MISFETのしきい値電圧を下げることができる技術を提供する。

【解決手段】半導体基板1上に形成されたpチャネル型MISFETQ1は、酸化ハフニウム膜よりなるゲート絶縁膜10を有し、このゲート絶縁膜10上に、酸化アルミニウム膜よりなる金属酸化物膜11を有する。そして、金属酸化物膜11上に窒化タンタル膜よりなるゲート電極12を有している。ここで、金属酸化物膜11は、ゲート電極12の仕事関数値をシフトする機能を有している。

(もっと読む)

半導体装置の製造方法

【課題】 優れた金属シリケート膜を形成することができ、特性や信頼性に優れた半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11上にゲート絶縁膜13を形成する工程と、ゲート絶縁膜上にゲート電極14を形成する工程と、を備えた半導体装置の製造方法であって、ゲート絶縁膜を形成する工程は、金属シリケート膜を形成する工程を含み、金属シリケート膜の形成に用いるシリコン原料は、モノシラン中の少なくとも1つの水素原子をアルキル基で置換した第1の炭化水素シリコン化合物、ジシラン中の少なくとも1つの水素原子をアルキル基で置換した第2の炭化水素シリコン化合物、及びトリシラン中の少なくとも1つの水素原子をアルキル基で置換した第3の炭化水素シリコン化合物の少なくとも1つを含む。

(もっと読む)

半導体装置

【課題】しきい値電圧を低くすることが可能な半導体装置を提供する。

【解決手段】この半導体装置は、シリコン基板1にチャネル領域3(13)を挟むように形成された一対のソース/ドレイン領域4(14)と、チャネル領域3(13)上にゲート絶縁膜5を介して形成され、ゲート絶縁膜5との界面近傍に配置された金属含有層7を含むゲート電極6(16)とを備えている。そして、金属含有層7は、ゲート絶縁膜5の表面を部分的に覆うようにドット状に形成されており、金属含有層7のドット間の平均距離は、金属含有層7のドットの直径以下に設定されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Finに応力を印加することによってN型MISおよびP型MISの両方のキャリア移動度を向上させることができるFin型FETを提供する。

【解決手段】半導体装置の製造方法は、半導体材料から成る複数のFin11、12を絶縁層10上に形成し、複数のFinの側面にゲート絶縁膜25を形成し、複数のFinのうちN型FETに用いられる第1のFin11の側面を該側面に対して垂直方向から圧縮し、かつ、P型FETに用いられる第2のFin12の側面を該側面に対して垂直方向へ引張するように、ゲート絶縁膜上にゲート電極31、32を形成することを具備する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】高精細でありトランジスタ特性の良好な、フレキシブルで大面積にも対応でき量

産性のある、薄膜トランジスタおよび薄膜トランジスタの製造方法を提供することを目的

とする。

【解決手段】基材上に、少なくとも下部電極のゲート電極、上部電極のソース電極及びド

レイン電極、絶縁層のゲート絶縁層、半導体からなる活性層の半導体活性層を含む層構成

の薄膜トランジスタであって、少なくとも上部電極が前記基材とは異なる第二の基材上の

、例えば、表面に凹部、又は凸部、又は平部を有する基材の凹部、又は凸部、又は平部に

電極材料が形成された後、前記基材のゲート絶縁層上に転写されて、上部電極のソース電

極及びドレイン電極を形成したことを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極としてFUSIゲート電極を用いた半導体装置において、同一導電型を有する各トランジスタの閾値電圧を調整する。

【解決手段】基板100上に第1のゲート絶縁膜103Aを介して形成された金属シリサイド膜よりなる第1のゲート電極115a(又は115b)を有する第1導電型の第1のトランジスタ115A(又は115B)と、基板100上に第2のゲート絶縁膜103Aを介して形成された金属シリサイド膜よりなる第2のゲート電極116a(又は116b)を有する第1導電型の第2のトランジスタ116A(又は116B)とを備え、第1のゲート電極115a(又は115b)及び第2のゲート電極116a(又は116b)の各々は、互いに異なるシリサイド組成比を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】高いオン電流とソース/ドレイン拡散層における低い接合リーク電流を両立可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に設けられたゲート絶縁膜3を含む。ゲート電極21は、ゲート絶縁膜上に設けられ、第1部分を含む。第1部分は、半導体と金属との化合物からなり、下面がゲート絶縁膜に達する。第1部分内の金属元素の密度は第1値である。1対のソース/ドレイン拡散層11は、ゲート電極の下方のチャネル領域を挟む。導電膜23は、半導体基板のソース/ドレイン拡散層の部分に設けられ、半導体と金属との化合物からなる。導電膜内の金属元素の密度は、第1値より小さい第2値である。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタを備える半導体装置において、ゲート絶縁膜と接する部分が金属シリサイド膜からなるゲートの仕事関数のマッチングと、ゲート電極低抵抗化との両立を実現する。

【解決手段】半導体装置は、基板100上にゲート絶縁膜102を介して形成されたゲート電極と、基板100におけるゲート電極123の両側に形成されたソース領域及びドレイン領域106とをそれぞれ有する複数のMOSトランジスタを備え、複数のMOSトランジスタは、ゲート電極としてPMOSゲート電極123を有するPMOSトランジスタを含み、PMOSゲート電極123は、ゲート絶縁膜102と接する第1の部分123aと、第1の部分123aの上に位置し且つ第1の部分123aよりもゲート長方向の幅が大きい第2の部分123bとを有する。

(もっと読む)

半導体装置のデュアルゲート構造物及びその形成方法

【課題】高誘電膜を含むCMOSトランジスタの形成に適合した構造を有するデュアルゲート構造物及びその形成方法を提供する。

【解決手段】デュアルゲート構造物は、第1及び第2領域が区分される基板と、前記第1領域の基板上に形成され、金属酸化膜、第1仕事関数を有する金属物質からなる第1金属パターン、シリコン拡散防止膜パターン、及びシリコンを含む導電膜パターンが積層された第1ゲート構造物と、前記第2領域の基板上に形成され、金属酸化膜、前記金属物質及びシリコン元素を含み前記第1仕事関数より低い第2仕事関数を有する第2金属パターン、及び前記シリコンを含む導電膜パターンが積層された第2ゲート構造物と、を含む。前記デュアルゲート構造物は各領域に形成されるゲート電極が同一の金属物質からなるので前記金属物質の一部を除去しなくてもよいので前記除去工程の際発生する金属酸化膜の損傷を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】Pチャネル電界効果トランジスタとNチャネル電界効果トランジスタとを有し、これらの電界効果トランジスタの高性能化を図り易い半導体装置の製造方法を得ること。

【解決手段】形成しようとする電界効果トランジスタ毎に、ゲート絶縁膜11,21とポリシリコン電極63a,63bとキャップ膜65a,65bとがこの順で積層された積層体を半導体基板10上に形成した後、各ポリシリコン電極の線幅方向両側面に直接、またはオフセットスペーサ膜15,25を介してサイドウォールスペーサ17,27を形成し、各キャップ膜の上面を含む平面に上面が位置する層間絶縁膜73aを形成してからこれらのキャップ膜を除去して各ポリシリコン電極の上面を露出させ、その上に第1金属層75aまたは第2金属層79を形成した後に該金属層によりその下のポリシリコン電極全体をシリサイド化して、互いに異なる金属のシリサイドからなるゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜中の電場を緩和するとともに素子の電流駆動力を高め、高速動作を可能にし、且つ高信頼性、高性能の半導体装置を提供する。

【解決手段】基板に設けられた半導体領域3と、それぞれの端部が互いに向かい合うように離間して半導体領域に設けられたソースおよびドレイン領域4a、4bと、ソースおよびドレイン領域上とソース領域およびドレイン領域間の領域上とに設けられた半導体層5と、半導体層を介してソース領域およびドレイン領域間の領域上に設けられたゲート絶縁膜7と、ゲート絶縁膜上に設けられたゲート電極8と、を備えている。

(もっと読む)

金属−窒化ケイ素、酸化ケイ素、又は酸窒化ケイ素のALD/CVD用のTi、Ta、Hf、Zr及び関連する金属のケイ素アミド

【課題】金属窒化ケイ素ベース膜、金属酸化ケイ素又は金属酸窒化ケイ素ベース膜を形成させるために好適な前駆体の提供。

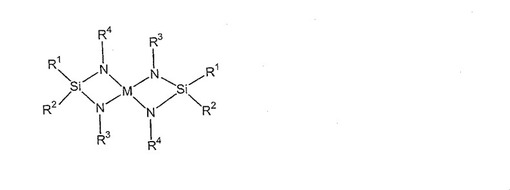

【解決手段】次の構造により表される有機金属錯体。

(式中、Mは、元素周期表の4族から選択される金属であり、そしてR1〜4は、同一又は異なって、ジアルキルアミド、ジフルオロアルキルアミド、水素、アルキル、アルコキシ、フルオロアルキル及びアルコキシ、脂環式、並びにアリールから成る群から選択されることができるが、但しR1及びR2が、ジアルキルアミド、ジフルオロアルキルアミド、アルコキシ、フルオロアルキル及びアルコキシである場合には、それらは連結して環を形成することができる。)。関連化合物もまた、開示されている。上記錯体を用いるCVD及びALD堆積法がまた、含まれる。

(もっと読む)

電気的プログラム可能ヒューズおよびその製造方法

【課題】 プログラム中にシリサイド層に形成されるギャップの長さに依存しない抵抗を有するeヒューズおよびその製造方法を提供する。

【解決手段】 電気的プログラム可能ヒューズ(eヒューズ(eFuse))は、基板の絶縁酸化物層の上の(1)半導体層、この半導体層に形成された(2)ダイオード、および、ダイオード上に形成された(3)シリサイド層を含む。ダイオードは、N+、p−、P+、またはP+、n−、N+構造を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイドプロセス前にイオン注入を行う半導体装置およびその製造方法であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法

【課題】絶縁破壊電界が高く、熱伝導率が極めて良好で放熱性に優れ、化学的にも安定であり、またバンドギャップが大きいというダイヤモンド半導体の特性を最大限に活用するために、ダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法を提供する。

【解決手段】半導体ダイヤモンドの表面と電極の表面が同一面となるように、半導体ダイヤモンドに設けた溝に電極が埋め込まれた構造を有することを特徴とするダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス。

(もっと読む)

FETデバイスにおいて低欠陥密度のニッケルシリサイドを形成するための方法及び装置

【課題】 方向性及び無方向性のプロセス・ステップを統合し、その結果、得られるシリサイドが最小限のシート抵抗を有し、かつパイプ欠陥を回避する、ニッケル堆積プロセス及びツールを提供すること。

【解決手段】 無方向性及び方向性の金属(例えば、Ni)堆積ステップが同一のプロセス・チャンバ内で実行される、方法及び装置が提供される。第1のプラズマは、ターゲットから材料を取り出すために形成され、材料のイオン密度を増大させる第2のプラズマは、RF発生器に接続された環状電極(例えば、Ni環)の内側に形成される。材料は、第2のプラズマ及び基板への電気的バイアスが存在しない場合、基板上に無方向性の堆積をされ、第2のプラズマが存在し、基板に電気的にバイアスがかけられている場合、方向性の堆積をされる。堆積された金属から形成されるニッケルシリサイドは、方向性プロセスのみで堆積された金属から形成されるNiSiよりも、ゲートポリシリコンの低シート抵抗を有し、より低いパイプ欠陥密度を有することができ、かつ無方向性堆積のみで堆積された金属から形成されたNiSiよりも低いソース/ドレイン接触抵抗を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜とシリサイドゲート電極の組み合わせ技術におけるしきい値制御の問題を解決し、高性能で信頼性に優れた半導体装置を提供する。

【解決手段】シリコン基板上に、ゲート絶縁膜とこのゲート絶縁膜上に設けられたゲート電極とを有する電界効果トランジスタを備えた半導体装置において、高誘電率絶縁膜(例えばHfSiON膜)を含むゲート絶縁膜を用い、高誘電率絶縁膜に接するように下層側に設けられた、第1の金属M1(例えばNi)、M1と異なる仕事関数をもつ第2の金属M2(例えばW)およびシリコン(Si)を含むシリサイドからなる第1の層領域と、第1の層領域に接する上層側に設けられたM1(例えばNi)およびSiを含むシリサイドからなる第2の層領域とを有するゲート電極を用いる。

(もっと読む)

161 - 180 / 250

[ Back to top ]