Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

101 - 120 / 250

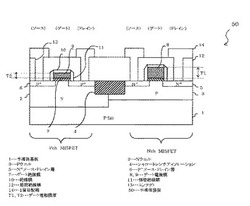

半導体装置及びその製造方法

【課題】ゲート電極構造が異なるNch絶縁ゲート型電界効果トランジスタとPch絶縁ゲート型電界効果トランジスタのゲート電極形状を安定化させる。

【解決手段】半導体装置50には、Nch MISFETとPch FMISFETが半導体基板1上に設けられる。半導体基板1上に、Nch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜8、及び絶縁膜10が積層形成される。半導体基板1上に、Pch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜9、及び絶縁膜10が積層形成される。ゲート電極膜9はゲート電極膜8よりもゲート電極膜同時加工時での補正膜厚分だけ薄く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧が低く、トランジスタ間でしきい値電圧のばらつきの無いトランジスタを含む半導体装置を提供する。

【解決手段】nチャネルトランジスタとpチャネルトランジスタとを含む相補型の半導体装置において、nチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)とシリコン(Si)からなる第1化合物層を含む第1メタルゲート電極を備え、pチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)と第2金属(M2)とシリコン(Si)からなる第2化合物層を含む第2メタルゲート電極を備え、第1化合物層の組成が、組成式:M1Six(1≦x)で表され、第2化合物層の組成が、組成式:M1M2Siy(0<y≦0.5)で表される。

(もっと読む)

トレンチ型MOSFET及びその製造方法

【課題】遅延時間を短縮し高速化が可能であり、Chip面積の縮小が可能なトレンチ型MOSFET及びその製造方法を実現する。

【解決手段】本発明のトレンチ型MOSFET10は、P型の高ドープドレイン部1、P型の低ドープドレイン部2、N型のチャネルボディ部3、P型のソース拡散部4がこの順で積層され、トレンチゲート電極6が基板表面から低ドープドレイン部2に達するトレンチに形成される。ここで、トレンチゲート電極6から電位をとるためのゲート電極引き出し部7・17が、トレンチゲート電極6と略直交してトレンチゲート電極6の長手方向に沿って複数配列されているので、トレンチゲート電極6により生じる寄生抵抗を分割することができる。したがって、遅延時間を短縮し高速化が可能であり、Chip面積の縮小が可能である。

(もっと読む)

半導体装置の製造方法

【課題】N−chトランジスタとP−chトランジスタとの境界の寸法制御性に優れ、工程数の増加を最小限に抑制しながら、N−chトランジスタ及びP−chトランジスタのゲートパターンの高さが可能な限り揃った構造を実現する。

【解決手段】基板上のHigh−k膜よりなる絶縁膜上にポリシリコンを形成する。該ポリシリコン膜をエッチングする際にハロゲン系ガスを用いた低バイアス処理を施すことにより、下地のHigh−k膜の膜質を改善しながら、N−chトランジスタ及びP−chトランジスタに独立した仕事関数を持つ金属電極を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】MOSFET等のデバイスのための高誘電率膜の製造方法を提供する。

【解決手段】Si基板101上のSiO2膜(又はSiON膜)102上にHf金属膜103をスパッタし、それを熱酸化処理してHfSiO膜104を形成する。その上にTi金属膜105をスパッタし、それを熱酸化処理して、TiO2膜106を形成する。TiO2膜106上に、TiN金属膜107を堆積させる。これら一連の処理は、大気に晒すことなく真空中で一貫して行われる。形成されたTiN/TiO2/HfSiO/SiO2/Si構造は、EOT<1.0nm, 低リーク電流, ヒステリシス<20mVを満たしている。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

金属ケイ素窒化物の被着方法

【課題】金属アミド、ケイ素前駆体及び窒素源ガスガスを前駆体として用いてプラズマ雰囲気下で循環式膜被着によって金属ケイ素窒化物膜を形成するための方法を提供する。

【解決手段】金属アミド前駆体をパルス送りする工程、未反応金属アミドをパージ除去する工程、プラズマ雰囲気下で反応チャンバ内に窒素源ガスを導入する工程、未反応窒素源ガスをパージ除去する工程、ケイ素前駆体をパルス送りする工程、未反応ケイ素前駆体をパージ除去する工程、プラズマ雰囲気下で反応チャンバ内に窒素源ガスを導入する工程、及び未反応窒素源ガスをパージ除去する工程を含む被着方法。

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】イオン注入される不純物濃度以上に不純物濃度を増大させた高濃度不純物層を有し、この高濃度不純物装置とシリサイド電極とにおける接触電気抵抗を低減したソース・ドレインを有するCMOS電界効果トランジスタ及びその製造方法を提供する。

【解決手段】n型MOS電界効果トランジスタ10とp型MOS電界効果トランジスタ20とを備え、そのソース・ドレイン13、14で、シリサイド電極132、142の下に、急峻な濃度勾配を有する2層の高濃度不純物層133、134、143、144を有するCMOS電界効果トランジスタ1を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダマシンゲートプロセスを用いて特性の高いMOSトランジスタを形成半導体装置及びその製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上に形成された絶縁膜Iにゲート電極用溝Aが形成され、ゲート電極用溝の底部にゲート絶縁膜21が形成され、ゲート絶縁膜の上層においてゲート電極用溝に埋め込まれてゲート電極22が形成され、絶縁膜の一部としてゲート電極用溝の側壁を構成し、酸化シリコンまたはホウ素含有窒化シリコンからなるオフセットスペーサ15が形成され、さらに絶縁膜の一部としてゲート電極から遠い側のオフセットスペーサの両側部にサイドウォールスペーサ17aが形成され、オフセットスペーサ及びサイドウォールスペーサの下部における半導体基板においてエクステンション領域16を有するソース・ドレイン領域18が形成されている構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化プロセスにおいても、また、Nchトランジスタ及びPchトランジスタの両方を持つデバイスにおいても、欠陥等を発生させることなく、トランジスタのチャネル領域に対する応力制御を行うことを可能にする。

【解決手段】Nchトランジスタの第1のゲート電極107及びPchトランジスタの第2のゲート電極108のそれぞれの構成材料として、互いに応力の大きさが異なる材料を用いている。

(もっと読む)

半導体装置

【課題】複数のフィンと、これらフィン側面の半導体層を有しつつ、隣接する他の素子への接触を防止しうる半導体装置を提供する。

【解決手段】本発明の実施の形態による半導体装置1は、半導体基板2と、半導体基板2上に所定の間隔を置いて互いに略平行に配置された複数のフィン3a、3b、3cと、複数のフィン3a、3b、3cの各々の両側面をゲート絶縁膜7を介して挟むように形成されたゲート電極4と、複数のフィン3a、3b、3cの少なくとも一部の側面上に形成される半導体層としてのエピタキシャル層9と、を有し、エピタキシャル層9は、複数のフィン3a、3b、3cのうちの両端に位置する2つのフィン3a、3cの外側側面上に位置する領域における厚さが、前記外側側面の反対側の側面上に位置する領域における厚さよりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

半導体装置の作製方法

【課題】結晶の面方位が制御された結晶性半導体膜を用いることで、均一なシリサイド膜を作製する方法及び、該シリサイド膜を用いた絶縁基板に形成された電気的特性のばらつきの小さい薄膜トランジスタの作製方法に関する。

【解決手段】キャップ膜を有する半導体膜を所定の条件でレーザ結晶化することにより結晶の面方位が一方向に制御された大粒径結晶からなる結晶性半導体膜を形成し、その結晶性半導体膜をシリサイドに用いることで、均一なシリサイド膜を形成することができる。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシンゲートプロセスを用いて抵抗素子を形成する場合、精度のよい抵抗素子を形成すされた半導体装置意およびその製造方法を提供する。

【解決手段】基板10に絶縁膜15が形成され、絶縁膜15に抵抗素子用溝15bが形成され、抵抗素子用溝15b内において抵抗素子用溝15bの全ての側壁面から少なくとも所定の距離A離間して抵抗素子17bが形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】ダミーゲートを除去することで形成された溝39、59を有して半導体基板11上に形成された側壁絶縁膜33、53と、前記溝39、59内にゲート絶縁膜41を介して形成されたゲート電極43、63と、前記側壁絶縁膜33、53上から前記半導体基板11上にかけてそれぞれに形成された第1、第2応力印加膜21、22と、前記ゲート電極43、63の両側に前記半導体基板11に形成されたソース・ドレイン領域35、36、55、56とを有し、前記応力印加膜21、22は前記第1溝39、第2溝59が形成される前に成膜されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置の製造方法

【課題】フルシリサイドゲート電極を有し、電気特性に優れたCMOSデバイスを容易に製造することが可能な半導体装置の製造方法を得る。

【解決手段】半導体基板における第1の導電型の領域上の高誘電率ゲート絶縁膜上に第1のポリシリコンゲート電極を、第2の導電型の領域上の高誘電率ゲート絶縁膜上に第2のポリシリコンゲート電極を形成する工程と、シリサイド化反応を抑制するシリサイド化反応抑制金属の元素を第2のポリシリコンゲート電極には注入せずに第1のポリシリコンゲート電極に注入する工程と、シリサイド化反応抑制金属の元素の注入後に、シリサイド化する金属の膜を少なくとも第1および第2のポリシリコンゲート電極上に形成する工程と、金属の膜を形成した半導体基板を熱処理して第1および第2のポリシリコンゲート電極をシリサイド化させてそれぞれをフルシリサイド電極とする熱処理工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】貴金属を含む合金を用いて金属シリサイドを形成する工程において、新たな製造設備の導入や運用コストの増加をもたらすことなく、貴金属の残渣を生じることなく、未反応のまま残存している合金を除去しうる半導体装置の製造方法を提供する。

【解決手段】シリコンが部分的に露出した領域を含む半導体基板上に、Ni等の金属と貴金属との合金よりなる金属合金膜を形成する工程と、熱処理により、前記露出した領域のシリコンと金属合金膜とを選択的に反応させ、Ni等の金属及び貴金属を含む金属シリサイド膜を前記露出した領域上に形成する工程と、未反応のまま残存している金属合金膜を、Ni等の金属よりもイオン化傾向の高い遷移金属を溶解した、過酸化水素を含有する溶液を用いて除去する工程とを有する。

(もっと読む)

101 - 120 / 250

[ Back to top ]