Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

21 - 40 / 250

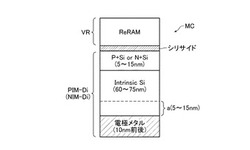

不揮発性半導体記憶装置

【課題】電圧−電流特性を改善した整流素子を用いたメモリセルを有する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の配線と、前記第1の配線に交差する第2の配線と、前記第1及び第2の配線に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子及び非オーミック素子を直列接続してなるメモリセルとを備え、前記非オーミック素子は、メタル層と、前記メタル層に接合された真性半導体層と、前記真性半導体層に接合された第1の不純物を含む不純物半導体層とを有することを特徴とする。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

熱処理方法および熱処理装置、ならびに半導体装置の製造方法

【課題】従来技術よりも小さい熱エネルギーで、SiC基板上に低抵抗のオーミック電極を形成することができ、熱処理における半導体装置の素子部の損傷および特性の劣化を防止することができる熱処理方法および熱処理装置、ならびに前記熱処理方法を用いた半導体装置の製造方法を提供する。

【解決手段】熱処理装置1の電源部21によって、複数のパルスを含むパルス列で構成される複数パルス電流を発生させ、導線22および電流端子部23を介して、SiC基板11上の電極金属膜12に供給する。これによって電極金属膜12にジュール熱を発生させ、発生したジュール熱によって電極金属膜12を加熱する。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーボン膜の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化できるようにする。

【解決手段】オーミック電極5を形成するための金属層15の形成前にレーザ光の吸収効果の高いカーボン層14を形成しておき、その上に金属層15を形成してからレーザアニールを行うようにしている。これにより、金属層15を構成する金属がカーボン層14を構成する炭素(C)やn+型基板1を構成するシリコン(Si)または炭素と反応してオーミック電極5が形成されるため、カーボン層14を除去する必要がない。また、レーザアニール時にカーボン層14を用いているため、レーザ光の吸収率を高くすることができ、オーミック電極5のコンタクト抵抗の低抵抗化を十分に行うことが可能となる。したがって、カーボン膜14の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

21 - 40 / 250

[ Back to top ]