Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

41 - 60 / 250

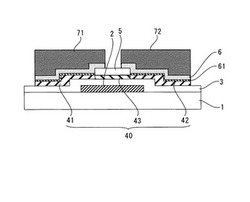

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】酸化珪素膜上の第1及び第2のシリサイド、チャネル形成領域、ソース領域及びドレイン領域を有する結晶性珪素膜と、チャネル形成領域上のゲイト絶縁膜と、ゲイト絶縁膜上のゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに接して設けられた第1の金属配線と、第2のシリサイドに接して設けられた第2の金属配線と、を有し、第1のシリサイドは、ソース領域の上面の一部及び側面に設けられ、第2のシリサイドは、ドレイン領域の上面の一部及び側面に設けられ、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1及び第2のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ゲート絶縁膜上のゲート電極の仕事関数を増大させることができ、低い閾値電圧の半導体装置を提供する。

【解決手段】半導体装置1は、基板(シリコン基板2)と、シリコン基板2上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極(Pt含有Ni3Si電極19)を備え、Pt含有Ni3Si電極19が、ゲート絶縁膜4とPt含有Ni3Si電極19との接する部分に、第一金属を含む第一金属シリサイド、および第二金属を含む第二金属シリサイドまたは第二金属を含み、第二金属を含む第二金属シリサイドが、第二金属を含む第二金属シリサイド中のシリコンに対する第二金属の組成比が1より大きい金属リッチシリサイドであることを特徴とする。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

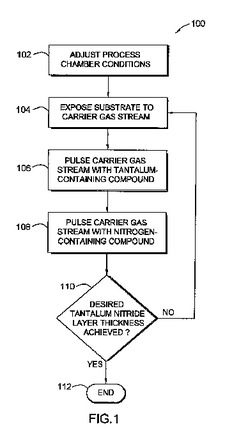

インサイチュチャンバ処理および堆積プロセス

本発明の実施形態は、原子層堆積(ALD)または化学気相堆積(CVD)などの気相堆積プロセス中に、プロセッシングチャンバの内面を処理し、材料を堆積させる方法を提供する。一実施形態では、前処理プロセス中に、プロセッシングチャンバの内面および基板を、水素化配位子化合物などの試薬にさらすことができる。この水素化配位子化合物は、次の堆積プロセス中に使用される有機金属前駆体から形成される遊離配位子と同じ配位子とすることができる。この遊離配位子は、堆積プロセス中に、通常、水素化または熱分解によって形成される。一例では、プロセッシングチャンバおよび基板は、ペンタキス(ジメチルアミノ)タンタル(PDMAT)などのアルキルアミノ配位子を有する有機金属化学前駆体を利用した気相堆積プロセスを行う前に、前処理プロセス中に、アルキルアミン化合物(例えば、ジメチルアミン)にさらされる。  (もっと読む)

(もっと読む)

成膜方法

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、たとえゲート構造間の距離が小さくなったとしても、ゲート構造間の半導体基板上に適正な膜厚のシリサイド膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施例によれば、ゲート構造G1,G2間の半導体基板1上の領域である第一の領域に形成される金属膜8の膜厚が、所望の膜厚以上となるように、第一の領域を含む半導体基板1上に、金属膜8を形成する。そして、シリサイド膜11形成のために、所望の膜厚分の金属膜8が半導体基板1を構成するシリコンと反応する程度の熱エネルギーを、半導体基板1に対して加える。

(もっと読む)

41 - 60 / 250

[ Back to top ]