Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

241 - 250 / 250

半導体装置、及びそれらの作製方法

【課題】 本発明では、工程、装置を複雑化することなく、要求される特性を有する薄膜トランジスタを作製することを目的とする。また、薄膜トランジスタの特性を精密に自由に制御することで、高い信頼性や優れた電気特性を有する半導体装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 本発明は、薄膜トランジスタにおいて、ゲート電極層で覆われている半導体層のソース領域側かドレイン領域側の一方に、低濃度不純物領域を作製する。低濃度不純物領域は、ゲート電極層をマスクとして、半導体層表面に対し、斜めにドーピングすることによって形成される。よって、薄膜トランジスタの微細な特性の制御を行うことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

半導体装置

【課題】デュアルゲート構造を有するMIS型トランジスタにおいて、デュアルゲートにおけるシリサイド部分の断線に起因する遅延の劣化を防止して、動作不良を防止できるようにする。

【解決手段】 半導体装置は、上部がシリサイド化されたゲート電極22を有するP型MOSトランジスタ100及びN型MOSトランジスタ200を備え、ゲート電極22におけるP型MOSトランジスタ100部分は、P型不純物が導入されたポリシリコンを含み、そのN型MOSトランジスタ200部分は、N型不純物が導入されたポリシリコンを含む。P型MOSトランジスタ100及びN型MOSトランジスタ200の互いのドレインは、シリサイド化されたポリシリコンを含む共有配線23により接続されている。共有配線23の線幅は、ゲート電極22の線幅よりも大きくなるように設定されている。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

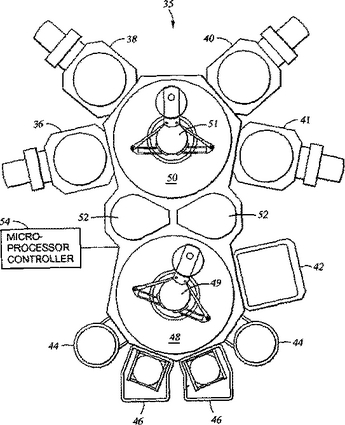

物理的気相堆積システムにおけるアニール方法及び装置

処理チャンバに配置された材料をアニールしてケイ化物層を形成するための方法及び装置が提供される。1つの態様において、シリコン材料が配置された基板を、チャンバ内の基板支持体上に配置するステップと、少なくともシリコン材料上に金属層を形成するステップと、上記基板をその場でアニールして、金属ケイ化物層を生成するステップとを備えた基板面を処理する方法が提供される。別の態様において、この方法は、ロードロックチャンバと、該ロードロックチャンバに結合された中間基板移送領域であって、第1基板移送チャンバ及び第2基板移送チャンバで構成される中間基板移送領域と、上記第1基板移送チャンバに配置された物理的気相堆積処理チャンバと、上記第2基板移送チャンバに配置されたアニールチャンバとを備えた装置において実行される。  (もっと読む)

(もっと読む)

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

241 - 250 / 250

[ Back to top ]